16 Bit Barrel Shifter Using D 3 L

16 Bit Barrel Shifter Using D 3 L Logic BY A HARISH 108 W 1 D 8002

Barrel Shifter � Combinational logic circuit with n data inputs, n data outputs and a set of control inputs � Control i/p’s specify how to shift the data between input and output � Part of µp CPU that specifies the direction of shift(left or right), type of shift and amount of shift from 0 to n-1 bits � Shift operation is controlled by 6 bits: Four bits for the length, one bit for direction, and one bit for type shift/rotate

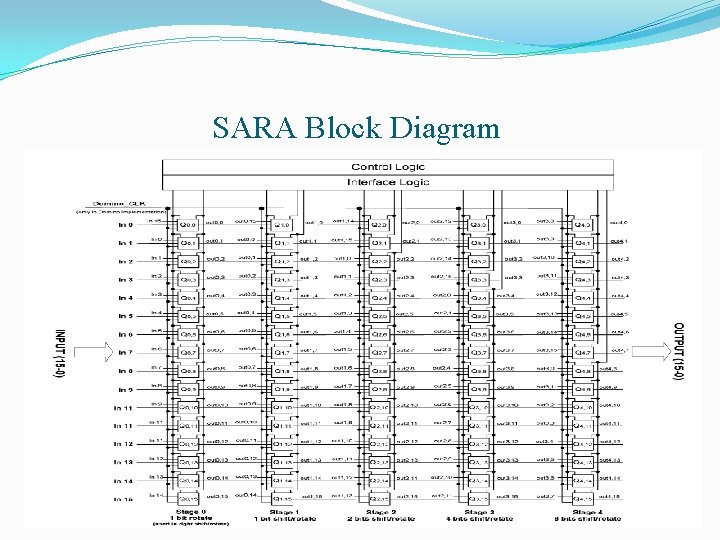

Cont. . � The 2 main blocks of barrel shifter are: shift-and-rotate array (SARA) and the control logic � SARA performs the actual shift-and-rotate task on available data while its controlling signals comes from control logic � SARA occupies most of the chip area, determines the critical path delay of the barrel shifter and so implemented in dynamic or D 3 L logic

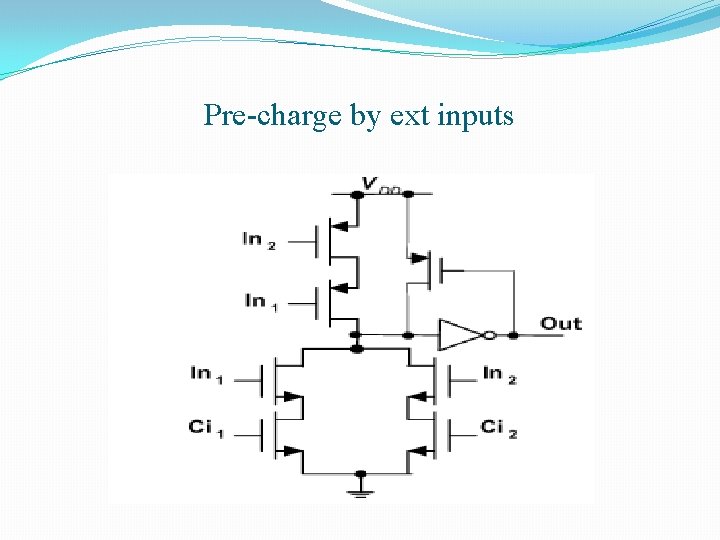

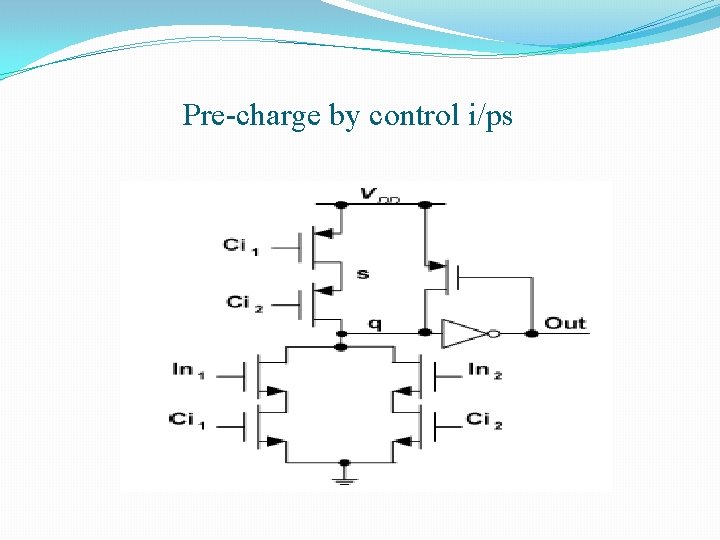

SARA � For a 16 bit barrel shifter, SARA is designed using 5 stages each with sixteen cells � Basic cell used in this array is an AO 22 gate that is called q-mux � Implements the function F= Ci 1* In 1 + Ci 2* In 2 , where Ci 1, Ci 2 come for control logic and In 1, In 2 come from external inputs or previous stage o/p’s

D 3 L Logic � Uses local data instead of a global clock to maintain correct pre-charge and evaluation phases � Eliminating the clock from dynamic gates using D 3 L logic yields less power consumption and faster gate operation � A D 3 L gate operates in two phases, pre-charge , evaluate and combination of inputs plays the role of the clock signal � Low power consumption and faster gate operation are advantages of D 3 L logic

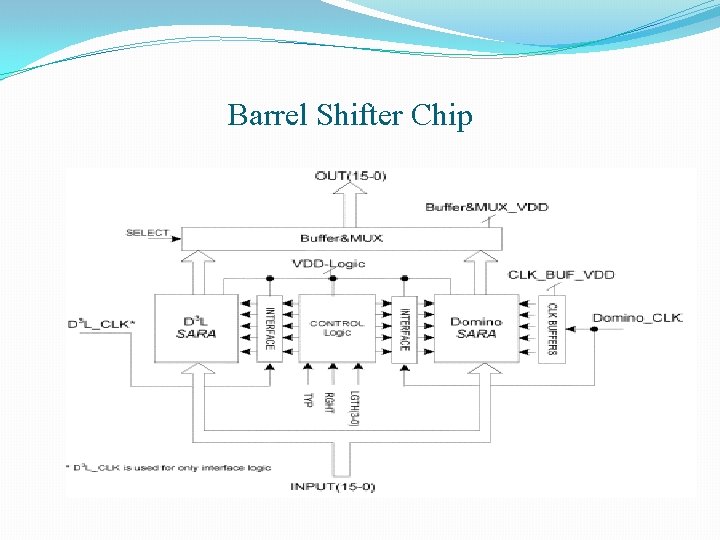

Barrel Shifter Chip

SARA Block Diagram

SARA Implementation � Elimination of clk signal is done by substitution of suitable input combinations with external inputs (In 1, In 2) and control inputs (Ci 1, Ci 2) � Control logic o/p’s are set low in pre-charge phase to charge the entire circuit � When the condition In 1=In 2=0 is satisfied , each qmux cell is pre-charged and transition in In 1 or In 2 starts the evaluation phase � Advantage over domino logic is conditional evaluation and less power consumption

Pre-charge by ext inputs

Pre-charge by control i/ps

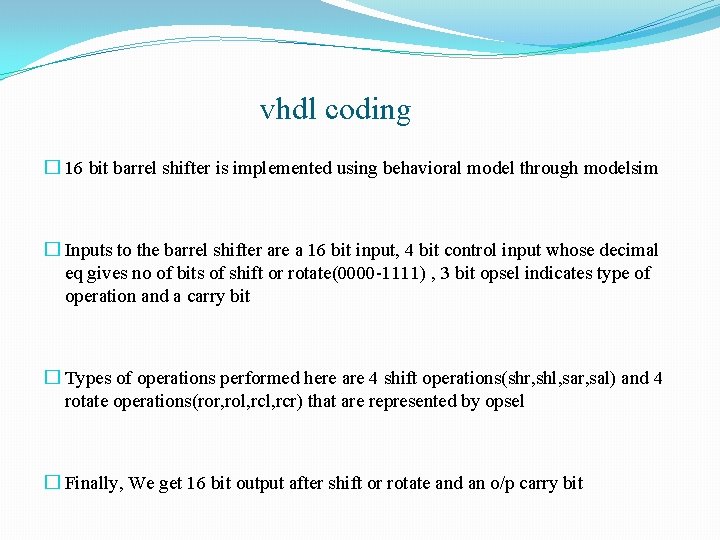

vhdl coding � 16 bit barrel shifter is implemented using behavioral model through modelsim � Inputs to the barrel shifter are a 16 bit input, 4 bit control input whose decimal eq gives no of bits of shift or rotate(0000 -1111) , 3 bit opsel indicates type of operation and a carry bit � Types of operations performed here are 4 shift operations(shr, shl, sar, sal) and 4 rotate operations(ror, rol, rcr) that are represented by opsel � Finally, We get 16 bit output after shift or rotate and an o/p carry bit

Simulations � For 2 bits shift or rotate: Let, 16 bit input (a) = 1011000101; 4 bit control i/p (b)= 0010 ; opsel =000, 010, 100, 110 ; c_in= 0 � Indicates the operations of logical shift left, arithmetic shift left, rotate left and rotate carry left operations by 2 bit positions

- Slides: 12