16 317 Microprocessor Systems Design I Instructor Dr

- Slides: 26

16. 317 Microprocessor Systems Design I Instructor: Dr. Michael Geiger Fall 2015 Lecture 31: Continue with PIC example programs: Interrupts (review) Analog to Digital Conversion

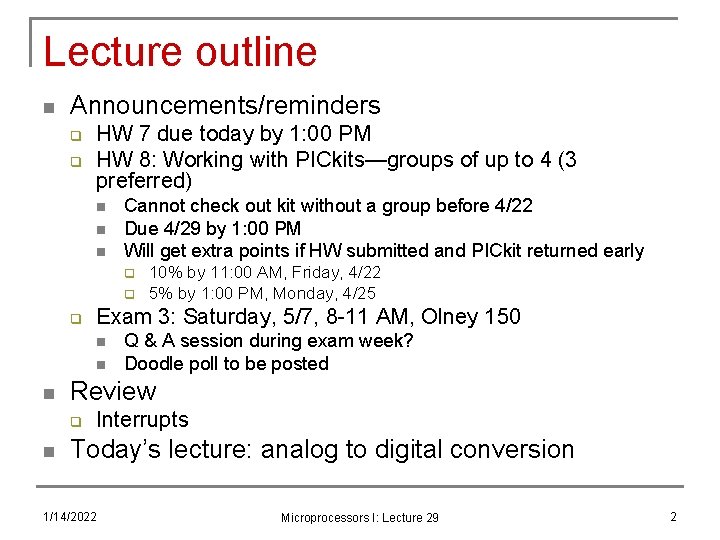

Lecture outline n Announcements/reminders q q HW 7 due today by 1: 00 PM HW 8: Working with PICkits—groups of up to 4 (3 preferred) n n n Cannot check out kit without a group before 4/22 Due 4/29 by 1: 00 PM Will get extra points if HW submitted and PICkit returned early q q q Exam 3: Saturday, 5/7, 8 -11 AM, Olney 150 n n n Q & A session during exam week? Doodle poll to be posted Review q n 10% by 11: 00 AM, Friday, 4/22 5% by 1: 00 PM, Monday, 4/25 Interrupts Today’s lecture: analog to digital conversion 1/14/2022 Microprocessors I: Lecture 29 2

Review: Interrupts n n PIC controllers allow internal and external interrupts Single interrupt service routine q q Must determine interrupt cause, then handle Code addresses handled slightly differently n n Interrupt setup q q n Processor goes to address 0 on reset, 4 on interrupt Reset “vector”: jump to start of main program Interrupt “vector”: jump to start of ISR Enable device-specific interrupts first Enable global interrupts (GIE bit on PIC 16 F 1829) Interrupt handling q q q Determine which device caused interrupt Clear device-specific interrupt flag Execute code to actually process interrupt, then retfie 1/14/2022 Microprocessors I: Lecture 29 3

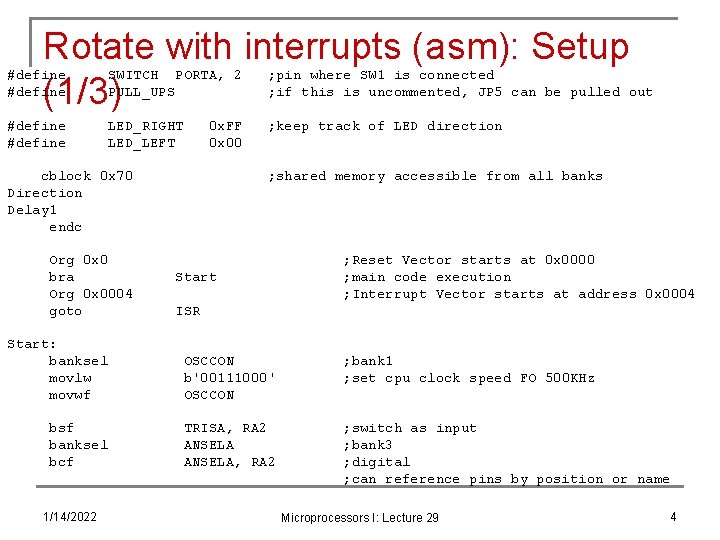

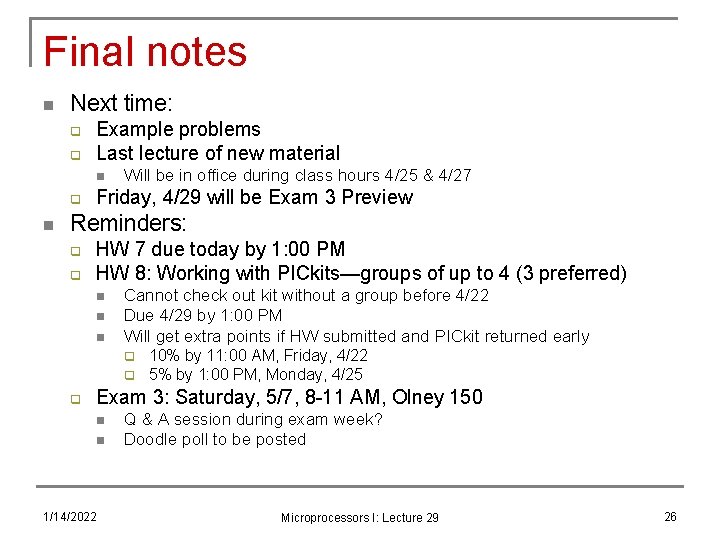

Rotate with interrupts (asm): Setup (1/3) #define SWITCH PORTA, 2 PULL_UPS ; pin where SW 1 is connected ; if this is uncommented, JP 5 can be pulled out #define LED_RIGHT LED_LEFT ; keep track of LED direction 0 x. FF 0 x 00 cblock 0 x 70 Direction Delay 1 endc Org 0 x 0 bra Org 0 x 0004 goto ; shared memory accessible from all banks Start ; Reset Vector starts at 0 x 0000 ; main code execution ; Interrupt Vector starts at address 0 x 0004 ISR Start: banksel movlw movwf OSCCON b'00111000' OSCCON ; bank 1 ; set cpu clock speed FO 500 KHz bsf banksel bcf TRISA, RA 2 ANSELA, RA 2 ; switch as input ; bank 3 ; digital ; can reference pins by position or name 1/14/2022 Microprocessors I: Lecture 29 4

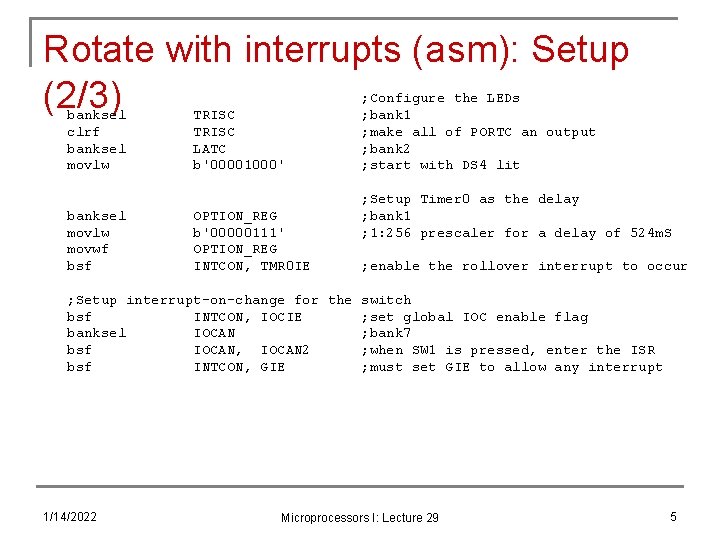

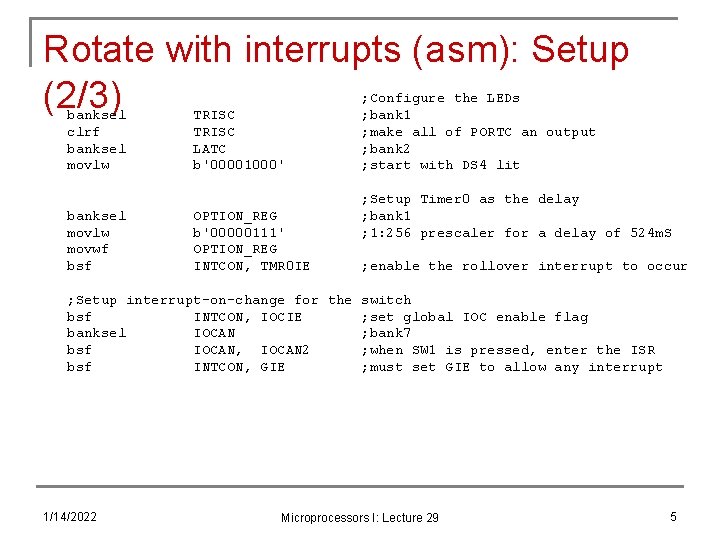

Rotate with interrupts (asm): Setup (2/3) banksel clrf banksel movlw movwf bsf TRISC LATC b'00001000' OPTION_REG b'00000111' OPTION_REG INTCON, TMR 0 IE ; Configure the LEDs ; bank 1 ; make all of PORTC an output ; bank 2 ; start with DS 4 lit ; Setup Timer 0 as the delay ; bank 1 ; 1: 256 prescaler for a delay of 524 m. S ; enable the rollover interrupt to occur ; Setup interrupt-on-change for the switch bsf INTCON, IOCIE ; set global IOC enable flag banksel IOCAN ; bank 7 bsf IOCAN, IOCAN 2 ; when SW 1 is pressed, enter the ISR bsf INTCON, GIE ; must set GIE to allow any interrupt 1/14/2022 Microprocessors I: Lecture 29 5

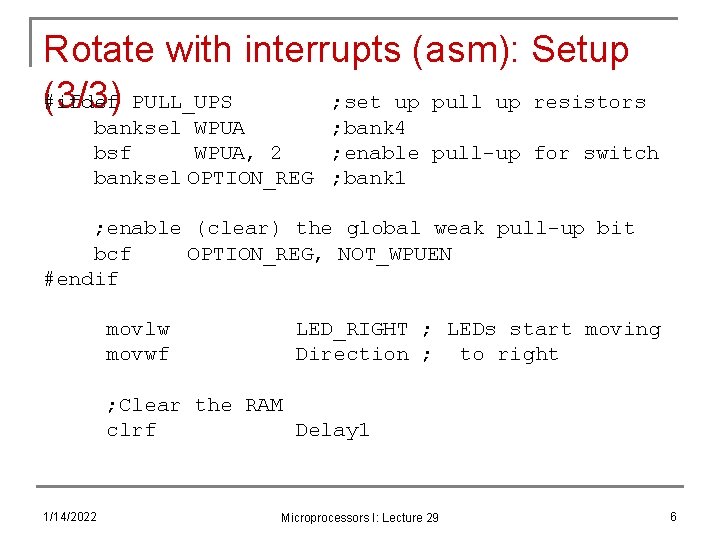

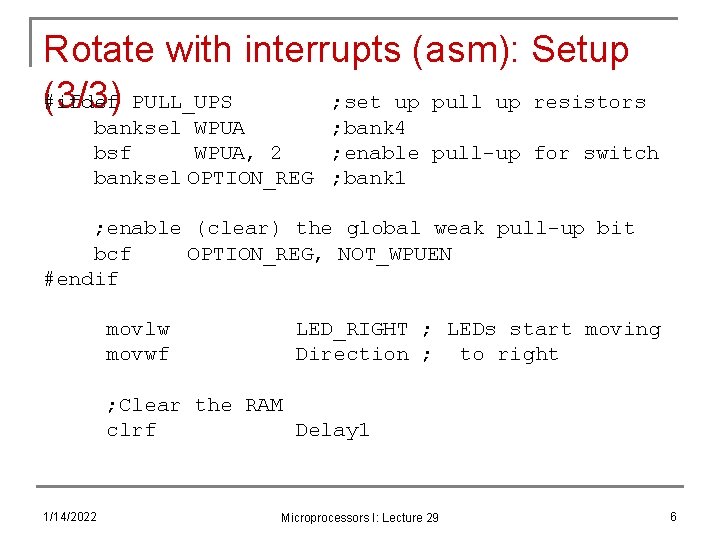

Rotate with interrupts (asm): Setup (3/3) PULL_UPS #ifdef ; set up pull up resistors banksel WPUA ; bank 4 bsf WPUA, 2 ; enable pull-up for switch banksel OPTION_REG ; bank 1 ; enable (clear) the global weak pull-up bit bcf OPTION_REG, NOT_WPUEN #endif movlw movwf LED_RIGHT ; LEDs start moving Direction ; to right ; Clear the RAM clrf Delay 1 1/14/2022 Microprocessors I: Lecture 29 6

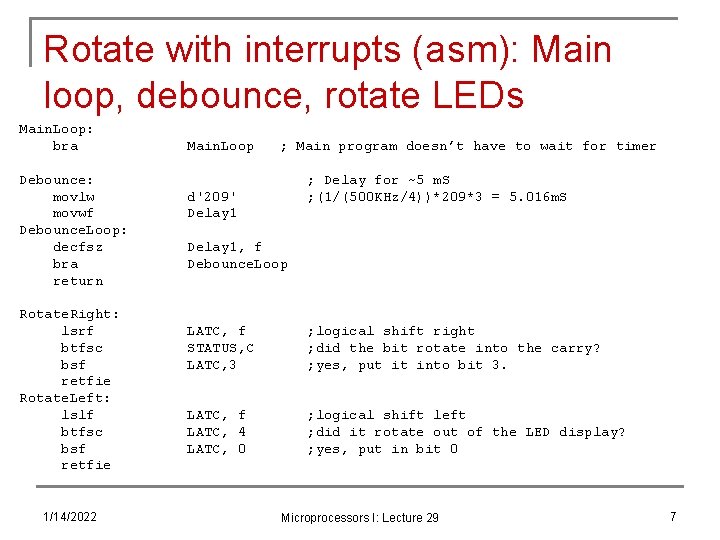

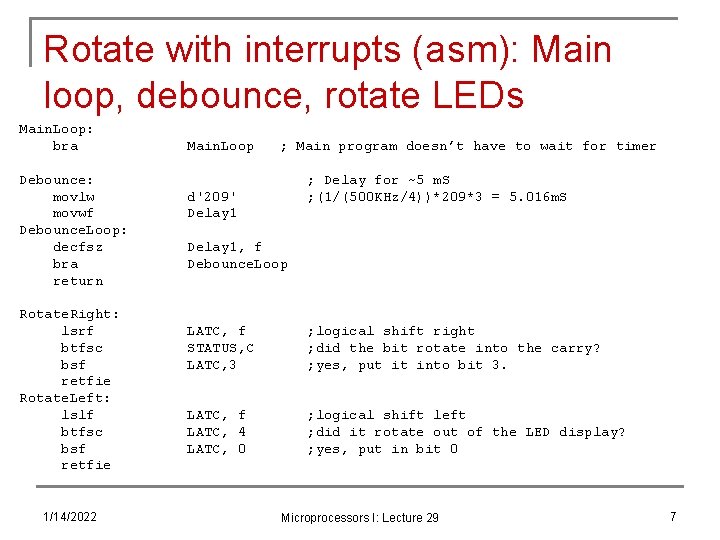

Rotate with interrupts (asm): Main loop, debounce, rotate LEDs Main. Loop: bra Debounce: movlw movwf Debounce. Loop: decfsz bra return Rotate. Right: lsrf btfsc bsf retfie Rotate. Left: lslf btfsc bsf retfie 1/14/2022 Main. Loop ; Main program doesn’t have to wait for timer ; Delay for ~5 m. S ; (1/(500 KHz/4))*209*3 = 5. 016 m. S d'209' Delay 1, f Debounce. Loop LATC, f STATUS, C LATC, 3 ; logical shift right ; did the bit rotate into the carry? ; yes, put it into bit 3. LATC, f LATC, 4 LATC, 0 ; logical shift left ; did it rotate out of the LED display? ; yes, put in bit 0 Microprocessors I: Lecture 29 7

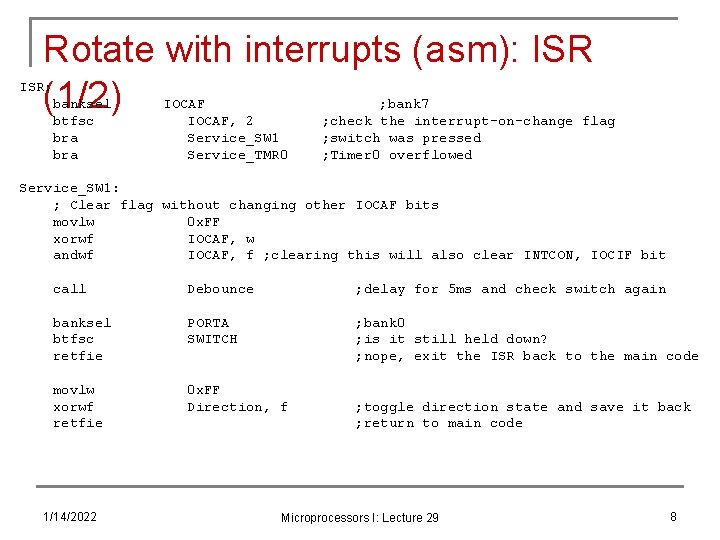

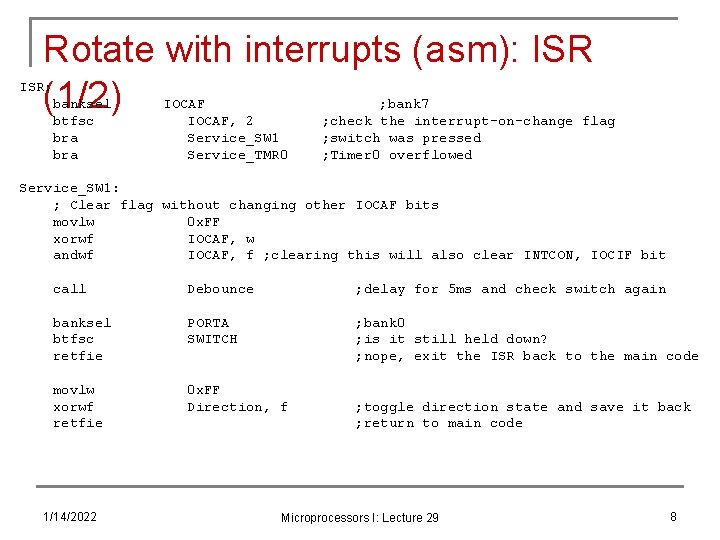

Rotate with interrupts (asm): ISR (1/2) ISR: banksel btfsc bra IOCAF, 2 Service_SW 1 Service_TMR 0 ; bank 7 ; check the interrupt-on-change flag ; switch was pressed ; Timer 0 overflowed Service_SW 1: ; Clear flag without changing other IOCAF bits movlw 0 x. FF xorwf IOCAF, w andwf IOCAF, f ; clearing this will also clear INTCON, IOCIF bit call Debounce ; delay for 5 ms and check switch again banksel btfsc retfie PORTA SWITCH ; bank 0 ; is it still held down? ; nope, exit the ISR back to the main code movlw xorwf retfie 0 x. FF Direction, f 1/14/2022 ; toggle direction state and save it back ; return to main code Microprocessors I: Lecture 29 8

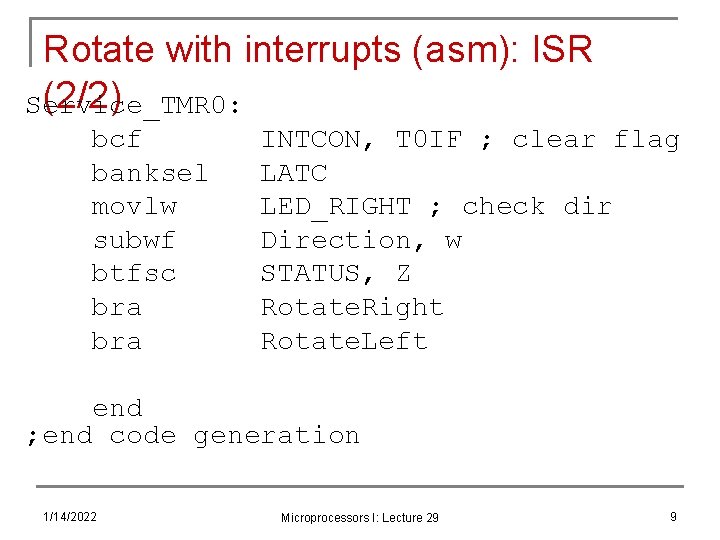

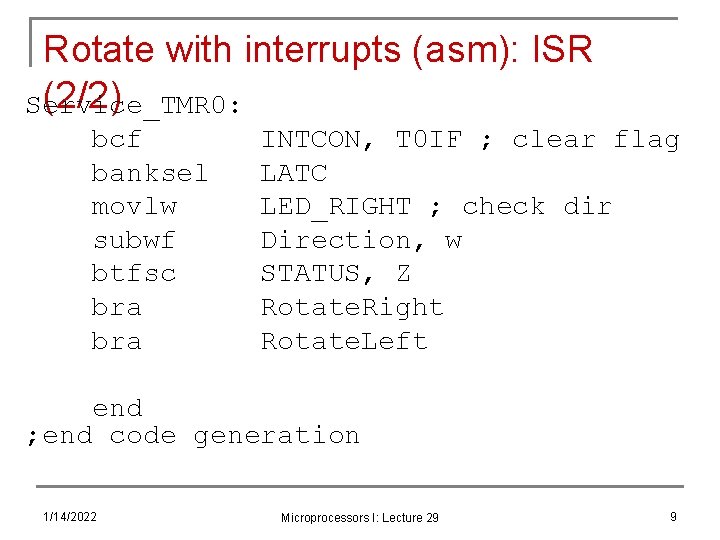

Rotate with interrupts (asm): ISR (2/2) Service_TMR 0: bcf banksel movlw subwf btfsc bra INTCON, T 0 IF ; clear flag LATC LED_RIGHT ; check dir Direction, w STATUS, Z Rotate. Right Rotate. Left end ; end code generation 1/14/2022 Microprocessors I: Lecture 29 9

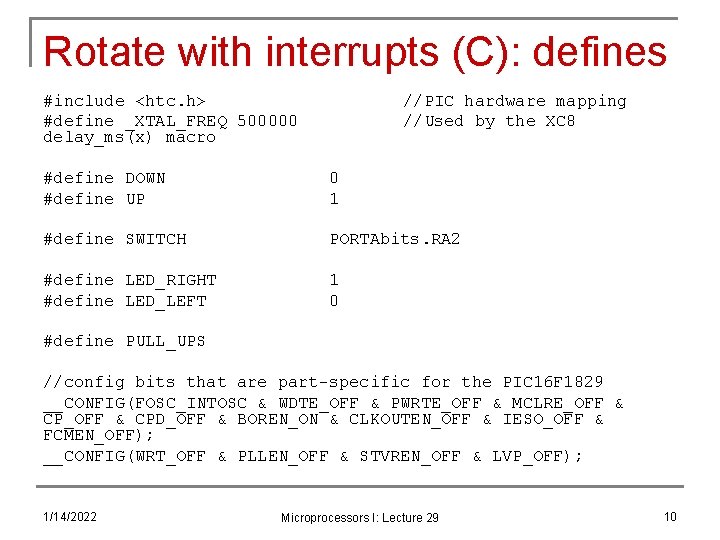

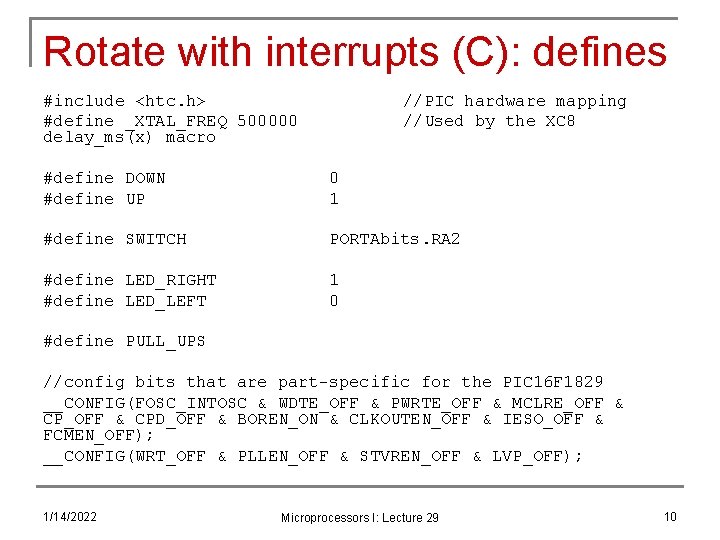

Rotate with interrupts (C): defines #include <htc. h> #define _XTAL_FREQ 500000 delay_ms(x) macro //PIC hardware mapping //Used by the XC 8 #define DOWN #define UP 0 1 #define SWITCH PORTAbits. RA 2 #define LED_RIGHT #define LED_LEFT 1 0 #define PULL_UPS //config bits that are part-specific for the PIC 16 F 1829 __CONFIG(FOSC_INTOSC & WDTE_OFF & PWRTE_OFF & MCLRE_OFF & CPD_OFF & BOREN_ON & CLKOUTEN_OFF & IESO_OFF & FCMEN_OFF); __CONFIG(WRT_OFF & PLLEN_OFF & STVREN_OFF & LVP_OFF); 1/14/2022 Microprocessors I: Lecture 29 10

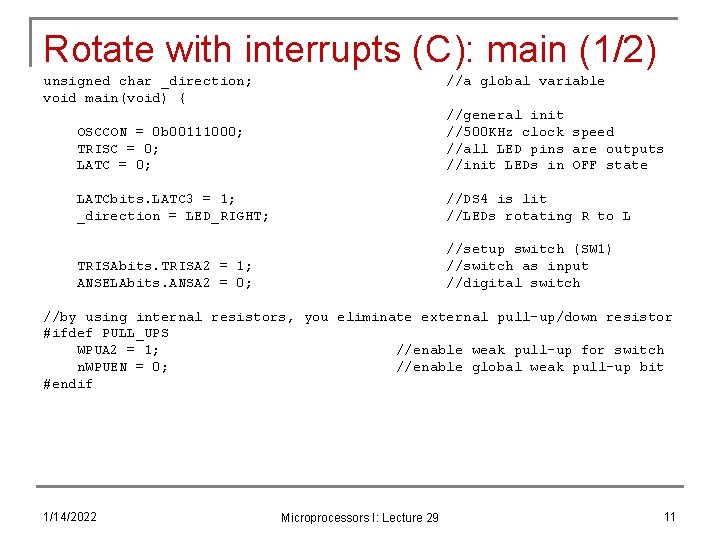

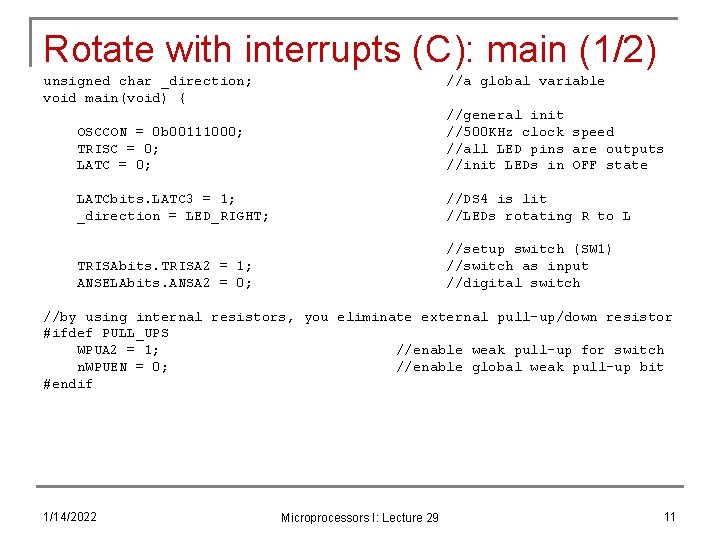

Rotate with interrupts (C): main (1/2) unsigned char _direction; void main(void) { //a global variable OSCCON = 0 b 00111000; TRISC = 0; LATC = 0; //general init //500 KHz clock speed //all LED pins are outputs //init LEDs in OFF state LATCbits. LATC 3 = 1; _direction = LED_RIGHT; //DS 4 is lit //LEDs rotating R to L TRISAbits. TRISA 2 = 1; ANSELAbits. ANSA 2 = 0; //setup switch (SW 1) //switch as input //digital switch //by using internal resistors, you eliminate external pull-up/down resistor #ifdef PULL_UPS WPUA 2 = 1; //enable weak pull-up for switch n. WPUEN = 0; //enable global weak pull-up bit #endif 1/14/2022 Microprocessors I: Lecture 29 11

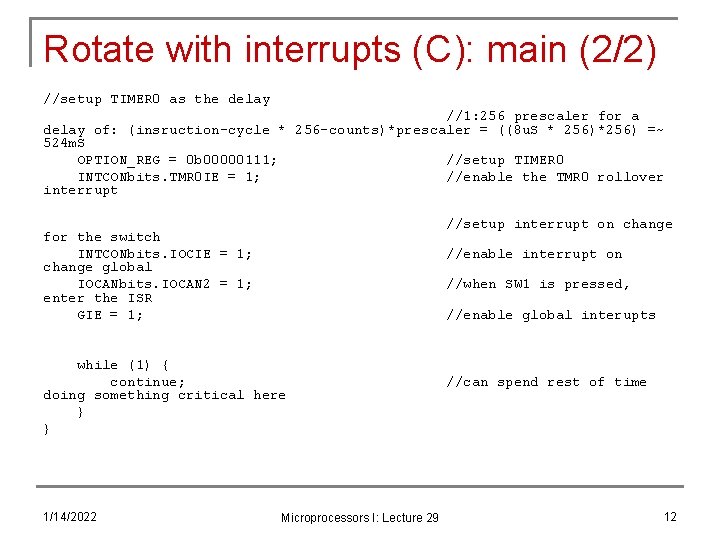

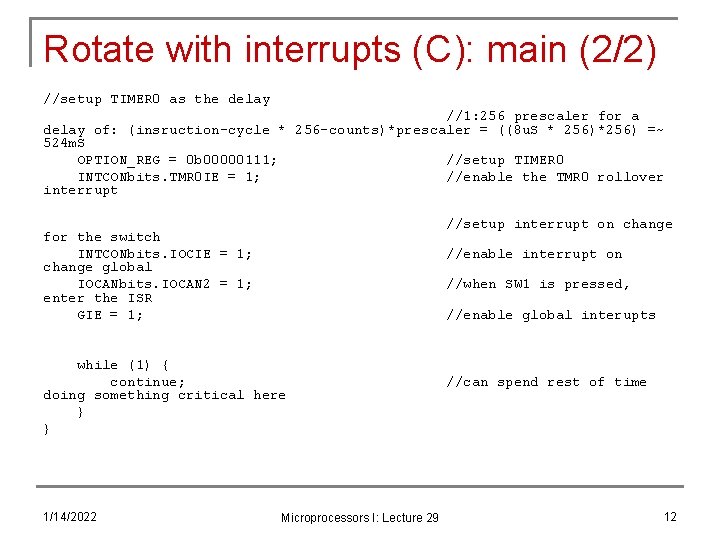

Rotate with interrupts (C): main (2/2) //setup TIMER 0 as the delay //1: 256 prescaler for a delay of: (insruction-cycle * 256 -counts)*prescaler = ((8 u. S * 256)*256) =~ 524 m. S OPTION_REG = 0 b 00000111; //setup TIMER 0 INTCONbits. TMR 0 IE = 1; //enable the TMR 0 rollover interrupt //setup interrupt on change for the switch INTCONbits. IOCIE = 1; change global IOCANbits. IOCAN 2 = 1; enter the ISR GIE = 1; //enable interrupt on //when SW 1 is pressed, //enable global interupts while (1) { continue; doing something critical here } } 1/14/2022 Microprocessors I: Lecture 29 //can spend rest of time 12

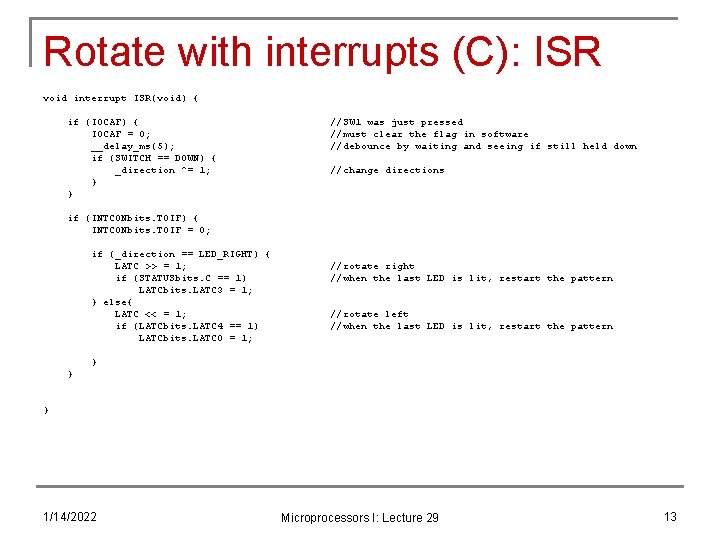

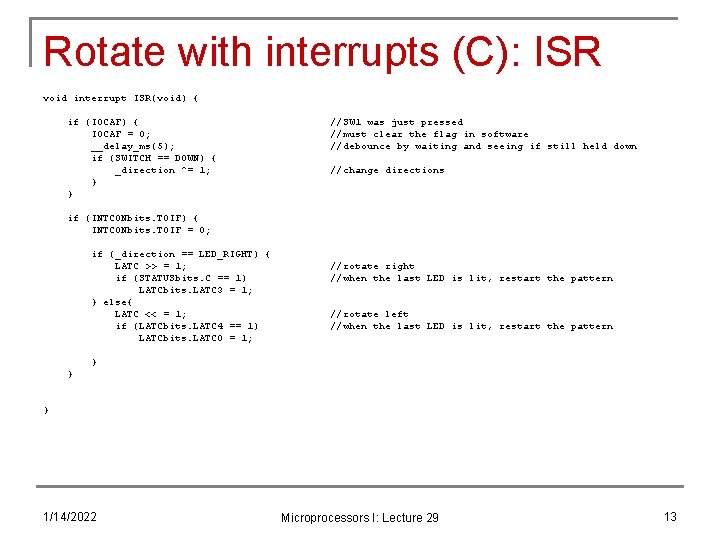

Rotate with interrupts (C): ISR void interrupt ISR(void) { if (IOCAF) { IOCAF = 0; __delay_ms(5); if (SWITCH == DOWN) { _direction ^= 1; } } //SW 1 was just pressed //must clear the flag in software //debounce by waiting and seeing if still held down //change directions if (INTCONbits. T 0 IF) { INTCONbits. T 0 IF = 0; if (_direction == LED_RIGHT) { LATC >> = 1; if (STATUSbits. C == 1) LATCbits. LATC 3 = 1; } else{ LATC << = 1; if (LATCbits. LATC 4 == 1) LATCbits. LATC 0 = 1; //rotate right //when the last LED is lit, restart the pattern //rotate left //when the last LED is lit, restart the pattern } } } 1/14/2022 Microprocessors I: Lecture 29 13

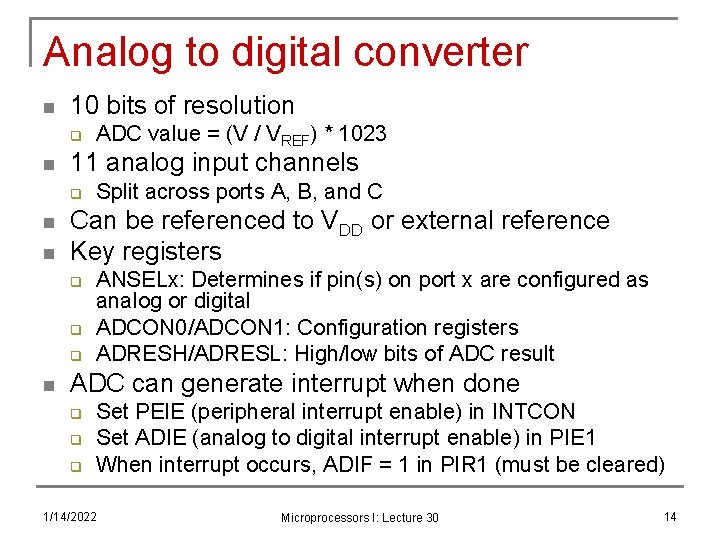

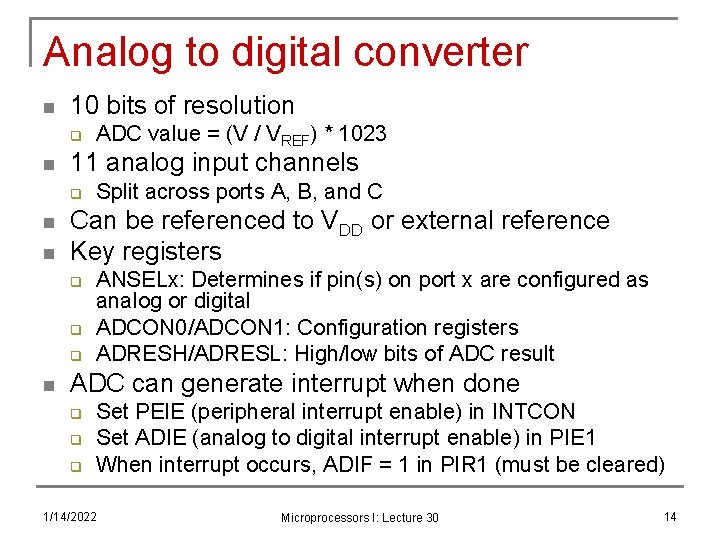

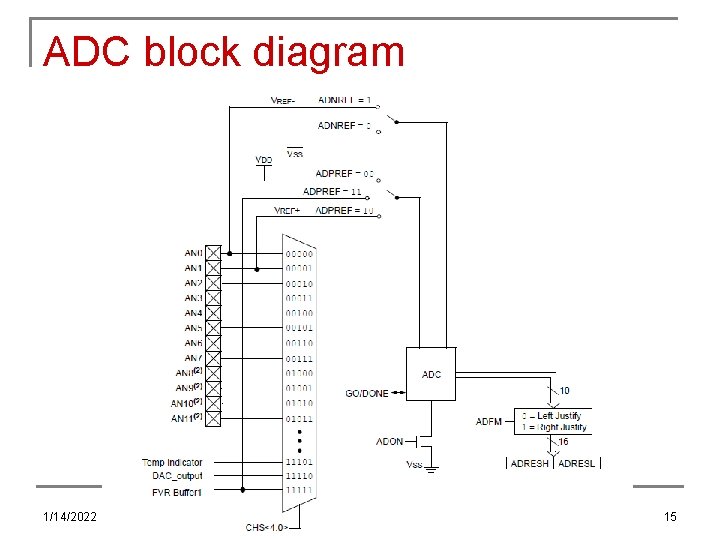

Analog to digital converter n 10 bits of resolution q n 11 analog input channels q n n Split across ports A, B, and C Can be referenced to VDD or external reference Key registers q q q n ADC value = (V / VREF) * 1023 ANSELx: Determines if pin(s) on port x are configured as analog or digital ADCON 0/ADCON 1: Configuration registers ADRESH/ADRESL: High/low bits of ADC result ADC can generate interrupt when done q q q Set PEIE (peripheral interrupt enable) in INTCON Set ADIE (analog to digital interrupt enable) in PIE 1 When interrupt occurs, ADIF = 1 in PIR 1 (must be cleared) 1/14/2022 Microprocessors I: Lecture 30 14

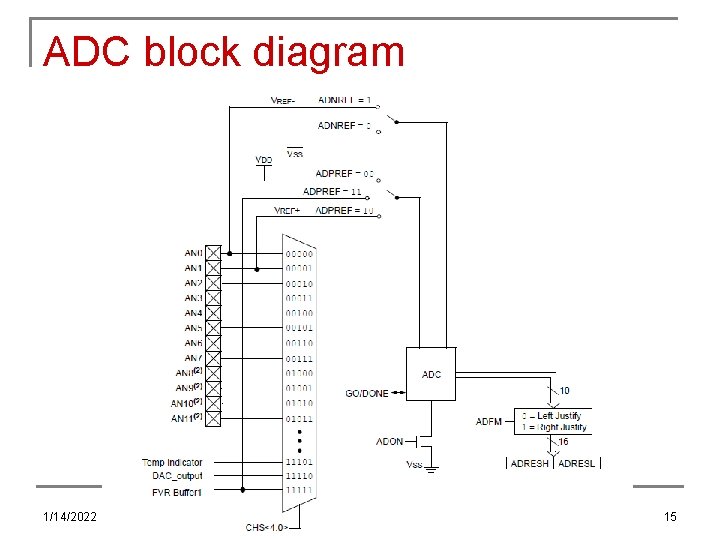

ADC block diagram 1/14/2022 Microprocessors I: Lecture 30 15

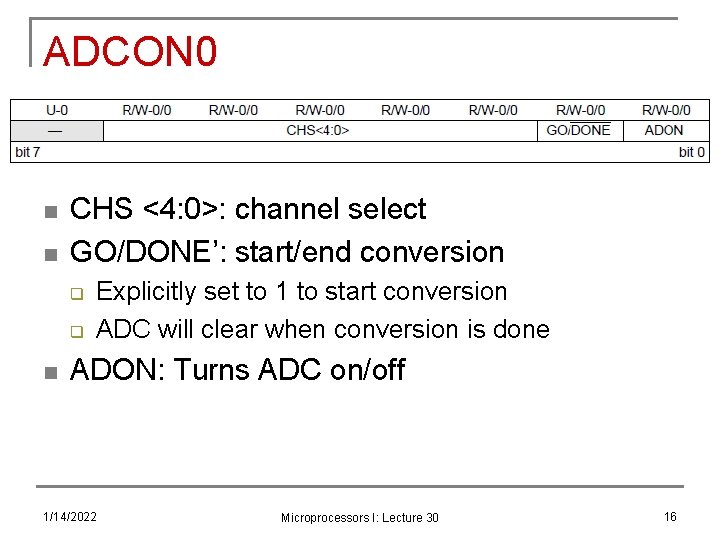

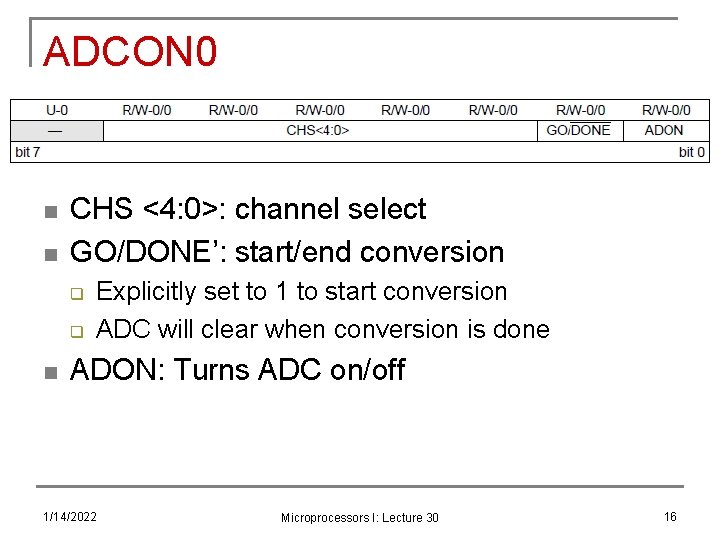

ADCON 0 n n CHS <4: 0>: channel select GO/DONE’: start/end conversion q q n Explicitly set to 1 to start conversion ADC will clear when conversion is done ADON: Turns ADC on/off 1/14/2022 Microprocessors I: Lecture 30 16

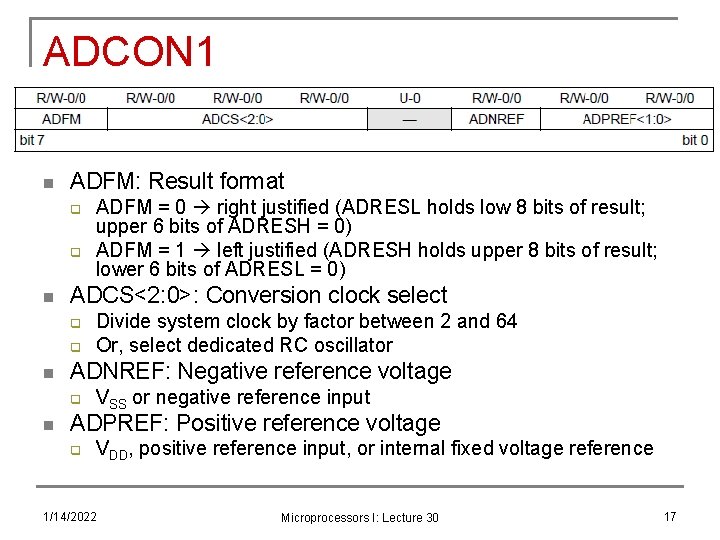

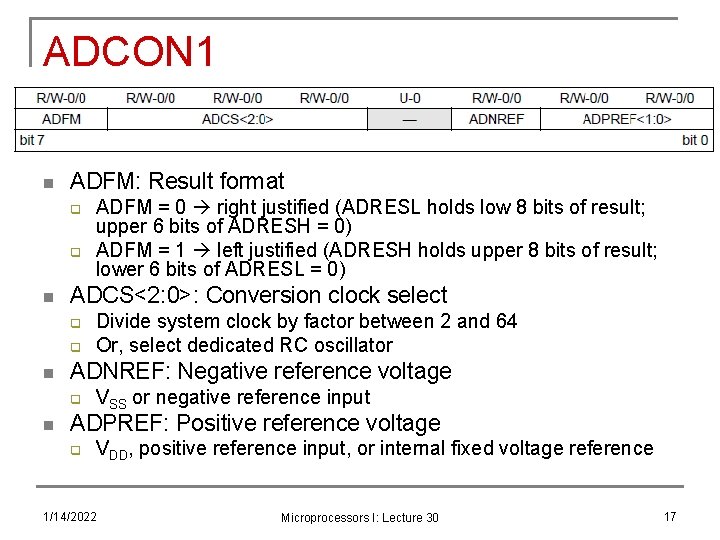

ADCON 1 n ADFM: Result format q q n ADCS<2: 0>: Conversion clock select q q n Divide system clock by factor between 2 and 64 Or, select dedicated RC oscillator ADNREF: Negative reference voltage q n ADFM = 0 right justified (ADRESL holds low 8 bits of result; upper 6 bits of ADRESH = 0) ADFM = 1 left justified (ADRESH holds upper 8 bits of result; lower 6 bits of ADRESL = 0) VSS or negative reference input ADPREF: Positive reference voltage q VDD, positive reference input, or internal fixed voltage reference 1/14/2022 Microprocessors I: Lecture 30 17

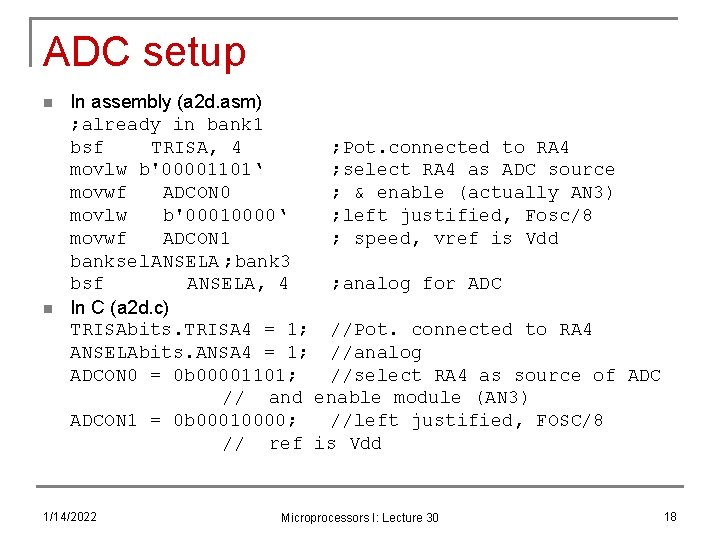

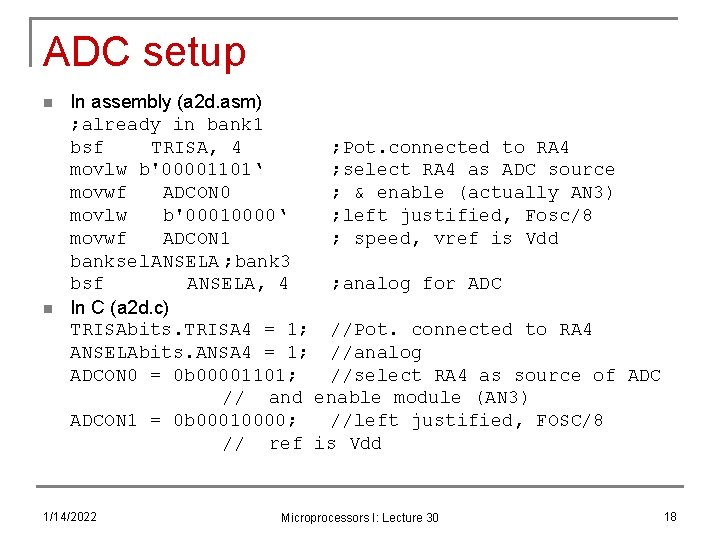

ADC setup n n In assembly (a 2 d. asm) ; already in bank 1 bsf TRISA, 4 ; Pot. connected to RA 4 movlw b'00001101‘ ; select RA 4 as ADC source movwf ADCON 0 ; & enable (actually AN 3) movlw b'00010000‘ ; left justified, Fosc/8 movwf ADCON 1 ; speed, vref is Vdd banksel. ANSELA ; bank 3 bsf ANSELA, 4 ; analog for ADC In C (a 2 d. c) TRISAbits. TRISA 4 = 1; //Pot. connected to RA 4 ANSELAbits. ANSA 4 = 1; //analog ADCON 0 = 0 b 00001101; //select RA 4 as source of ADC // and enable module (AN 3) ADCON 1 = 0 b 00010000; //left justified, FOSC/8 // ref is Vdd 1/14/2022 Microprocessors I: Lecture 30 18

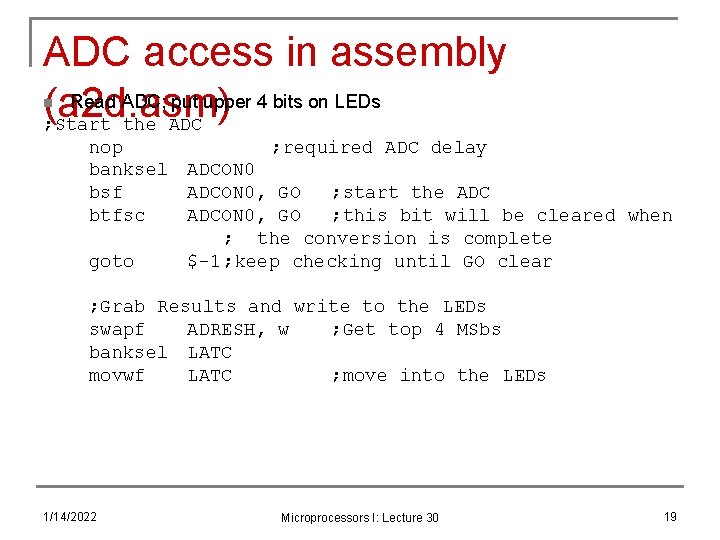

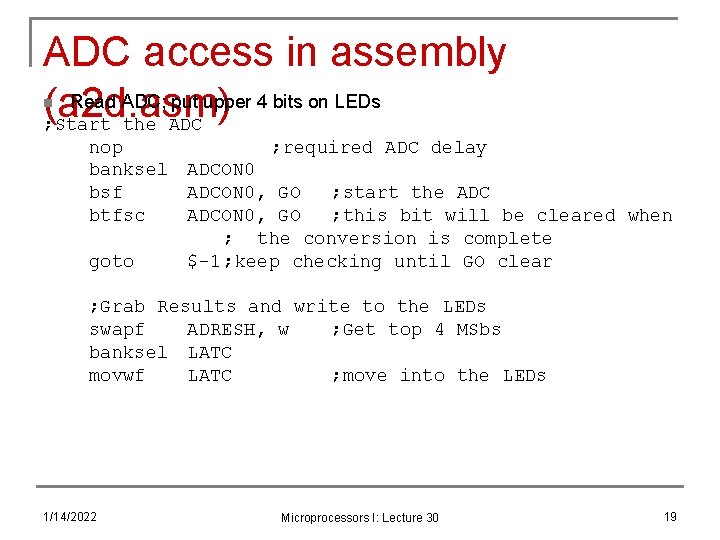

ADC access in assembly Read ADC; put upper 4 bits on LEDs (a 2 d. asm) ; Start the ADC n nop ; required ADC delay banksel ADCON 0 bsf ADCON 0, GO ; start the ADC btfsc ADCON 0, GO ; this bit will be cleared when ; the conversion is complete goto $-1; keep checking until GO clear ; Grab Results and write to the LEDs swapf ADRESH, w ; Get top 4 MSbs banksel LATC movwf LATC ; move into the LEDs 1/14/2022 Microprocessors I: Lecture 30 19

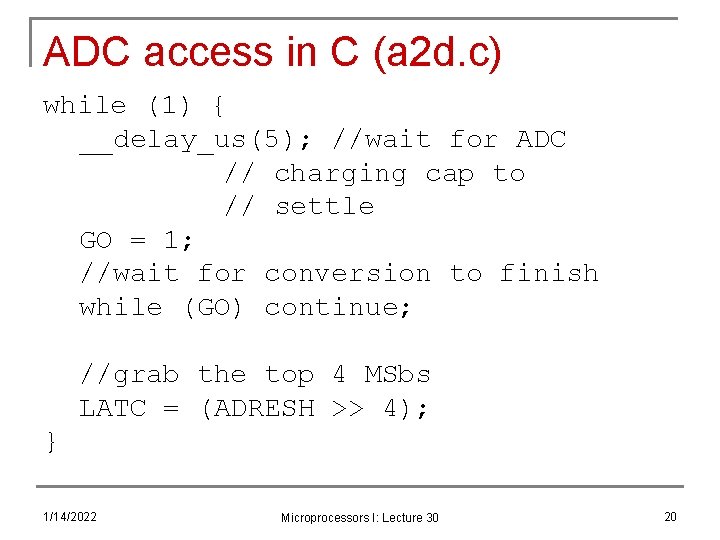

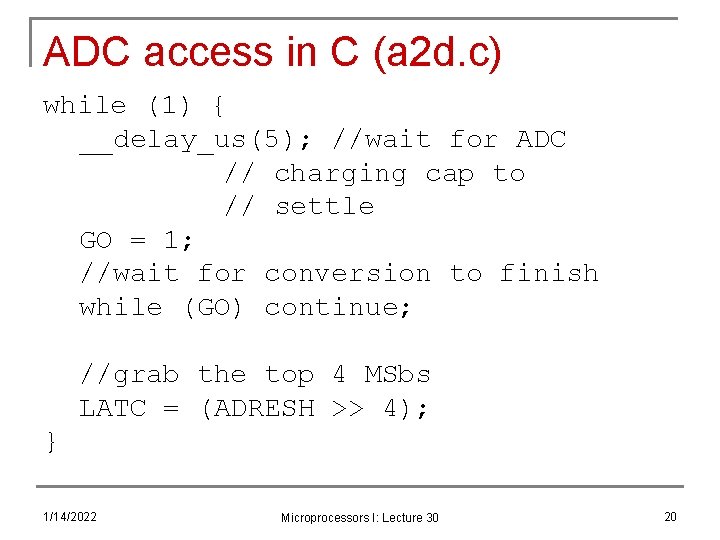

ADC access in C (a 2 d. c) while (1) { __delay_us(5); //wait for ADC // charging cap to // settle GO = 1; //wait for conversion to finish while (GO) continue; //grab the top 4 MSbs LATC = (ADRESH >> 4); } 1/14/2022 Microprocessors I: Lecture 30 20

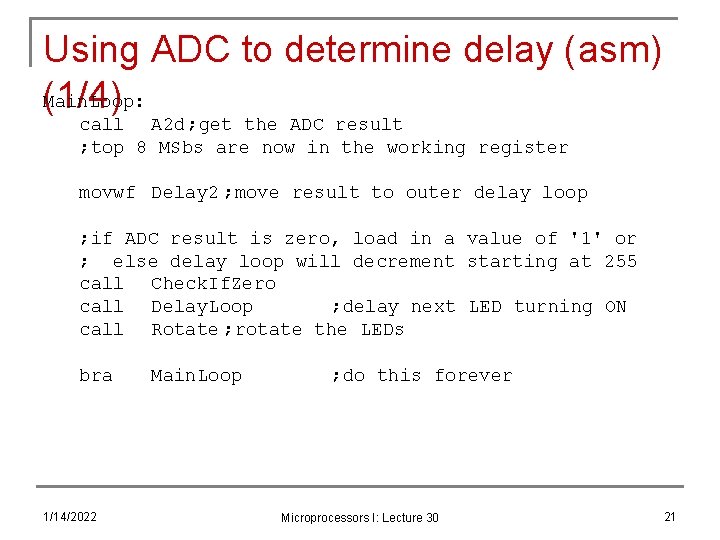

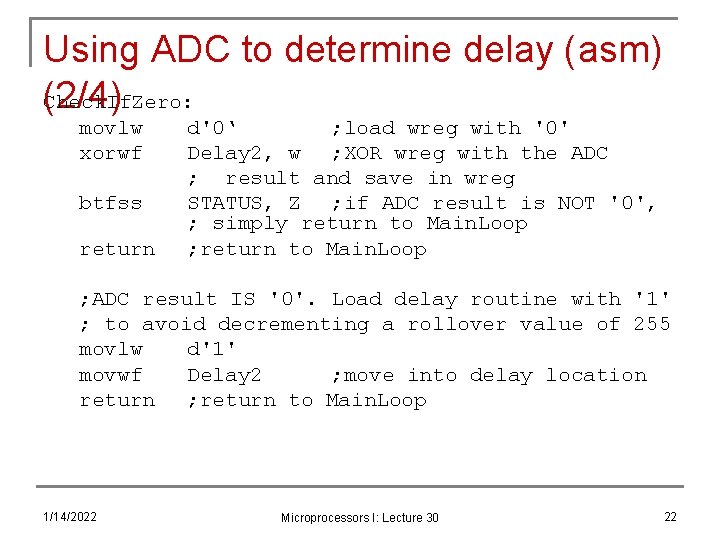

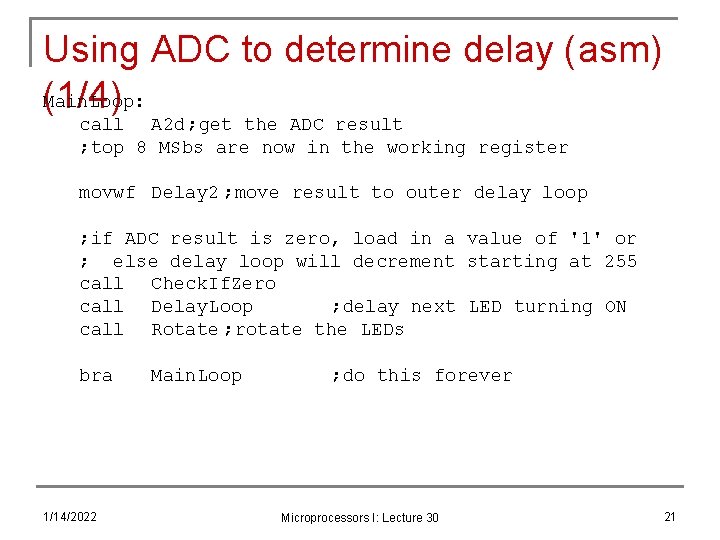

Using ADC to determine delay (asm) Main. Loop: (1/4) call A 2 d; get the ADC result ; top 8 MSbs are now in the working register movwf Delay 2 ; move result to outer delay loop ; if ADC result is zero, load in a value of '1' or ; else delay loop will decrement starting at 255 call Check. If. Zero call Delay. Loop ; delay next LED turning ON call Rotate ; rotate the LEDs bra 1/14/2022 Main. Loop ; do this forever Microprocessors I: Lecture 30 21

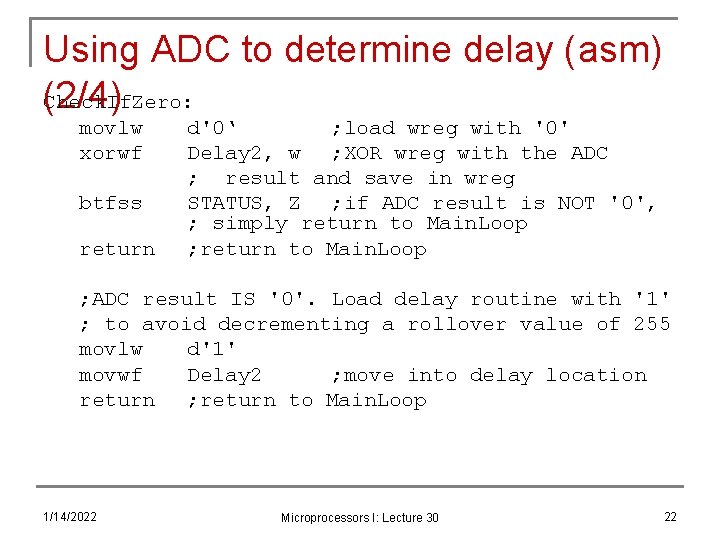

Using ADC to determine delay (asm) (2/4) Check. If. Zero: movlw xorwf btfss return d'0‘ ; load wreg with '0' Delay 2, w ; XOR wreg with the ADC ; result and save in wreg STATUS, Z ; if ADC result is NOT '0', ; simply return to Main. Loop ; ADC result IS '0'. Load delay routine with '1' ; to avoid decrementing a rollover value of 255 movlw d'1' movwf Delay 2 ; move into delay location return ; return to Main. Loop 1/14/2022 Microprocessors I: Lecture 30 22

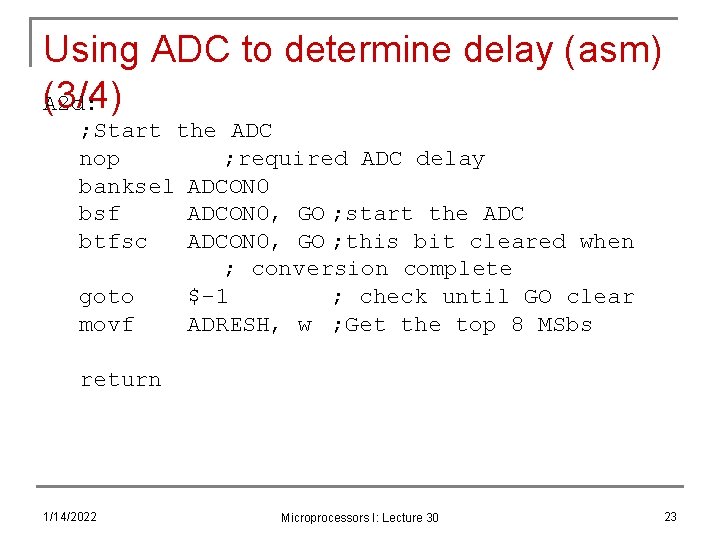

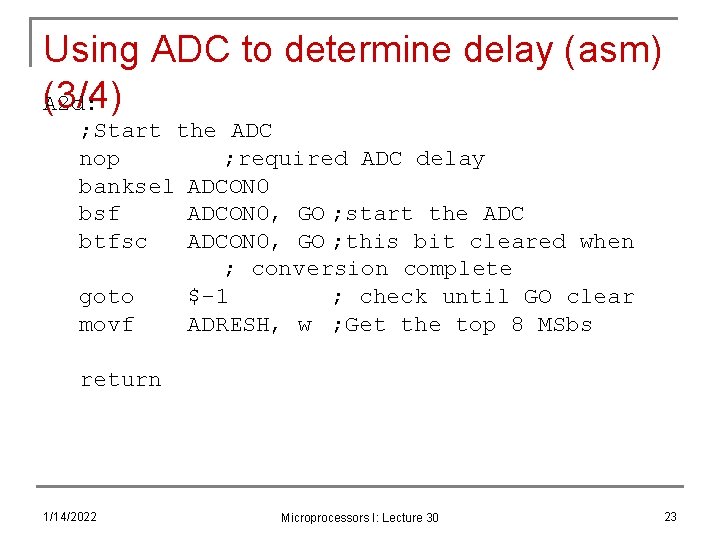

Using ADC to determine delay (asm) (3/4) A 2 d: ; Start the ADC nop ; required ADC delay banksel ADCON 0 bsf ADCON 0, GO ; start the ADC btfsc ADCON 0, GO ; this bit cleared when ; conversion complete goto $-1 ; check until GO clear movf ADRESH, w ; Get the top 8 MSbs return 1/14/2022 Microprocessors I: Lecture 30 23

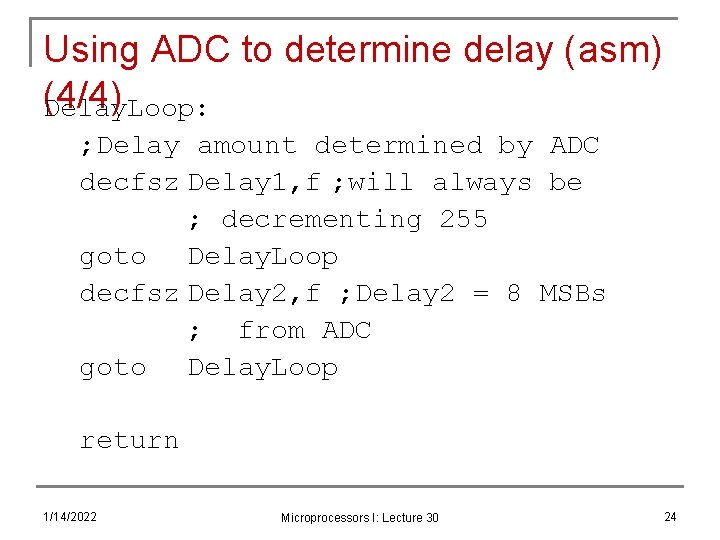

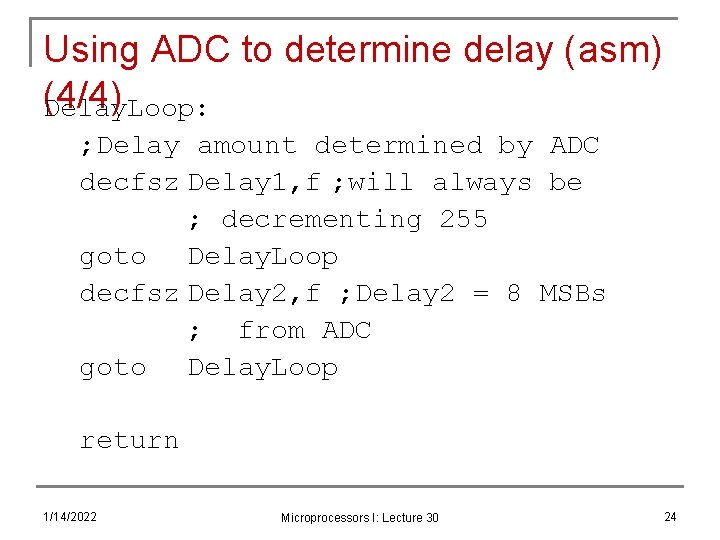

Using ADC to determine delay (asm) (4/4) Delay. Loop: ; Delay amount determined by ADC decfsz Delay 1, f ; will always be ; decrementing 255 goto Delay. Loop decfsz Delay 2, f ; Delay 2 = 8 MSBs ; from ADC goto Delay. Loop return 1/14/2022 Microprocessors I: Lecture 30 24

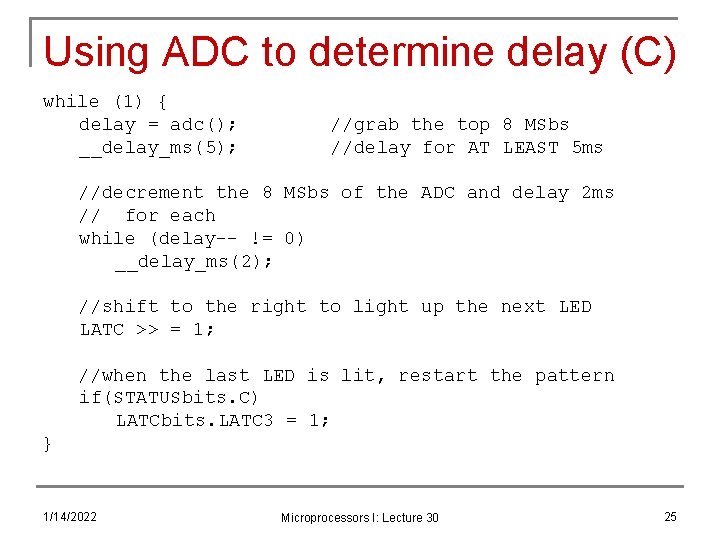

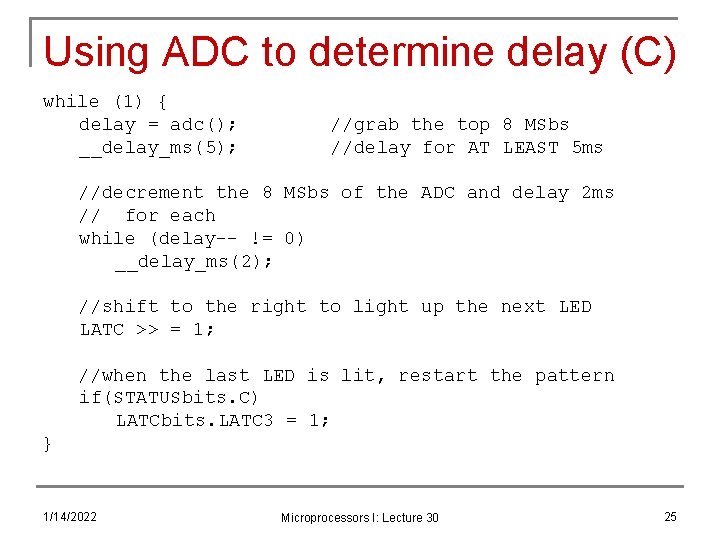

Using ADC to determine delay (C) while (1) { delay = adc(); __delay_ms(5); //grab the top 8 MSbs //delay for AT LEAST 5 ms //decrement the 8 MSbs of the ADC and delay 2 ms // for each while (delay-- != 0) __delay_ms(2); //shift to the right to light up the next LED LATC >> = 1; //when the last LED is lit, restart the pattern if(STATUSbits. C) LATCbits. LATC 3 = 1; } 1/14/2022 Microprocessors I: Lecture 30 25

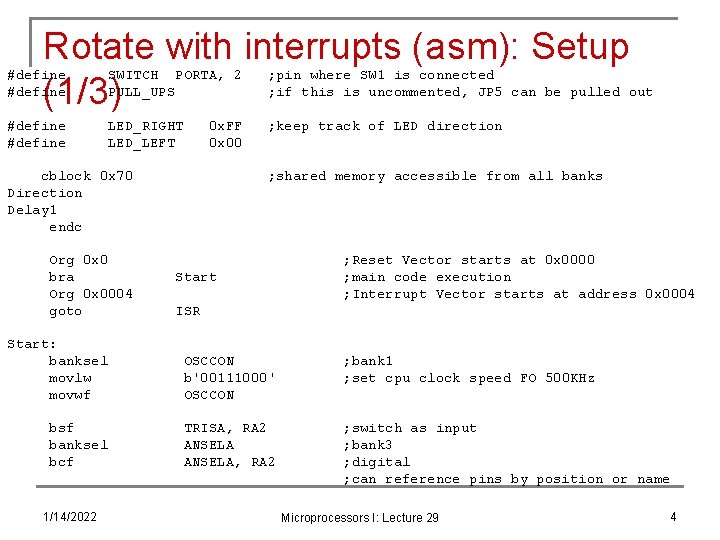

Final notes n Next time: q q Example problems Last lecture of new material n q n Will be in office during class hours 4/25 & 4/27 Friday, 4/29 will be Exam 3 Preview Reminders: q q HW 7 due today by 1: 00 PM HW 8: Working with PICkits—groups of up to 4 (3 preferred) n n n Cannot check out kit without a group before 4/22 Due 4/29 by 1: 00 PM Will get extra points if HW submitted and PICkit returned early q q q 10% by 11: 00 AM, Friday, 4/22 5% by 1: 00 PM, Monday, 4/25 Exam 3: Saturday, 5/7, 8 -11 AM, Olney 150 n n 1/14/2022 Q & A session during exam week? Doodle poll to be posted Microprocessors I: Lecture 29 26