15 745 Register Allocation CS 745 Register Allocation

- Slides: 33

15 -745 Register Allocation CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 1

Intro to Global Register Allocation Problem: • Allocation of variables (pseudo-registers) to hardware registers in a procedure One of the most important optimizations • Memory accesses are more costly than register accesses – True even with caches – True even with CISC architectures • Important for other optimizations – E. g. , redundancy elimination assumes old values are kept in registers • When it does not work well, the performance impact is noticeable. CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 2

Terminology Allocation • decision to keep a pseudo-register in a hardware register • prior to register allocation, we assume an infinite set of registers – (aka “temps” or “pseudo-registers”). Spilling • a pseudo-register is spilled to memory, if not kept in a hardware register Assignment • decision to keep a pseudo-register in a specific hardware register CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 3

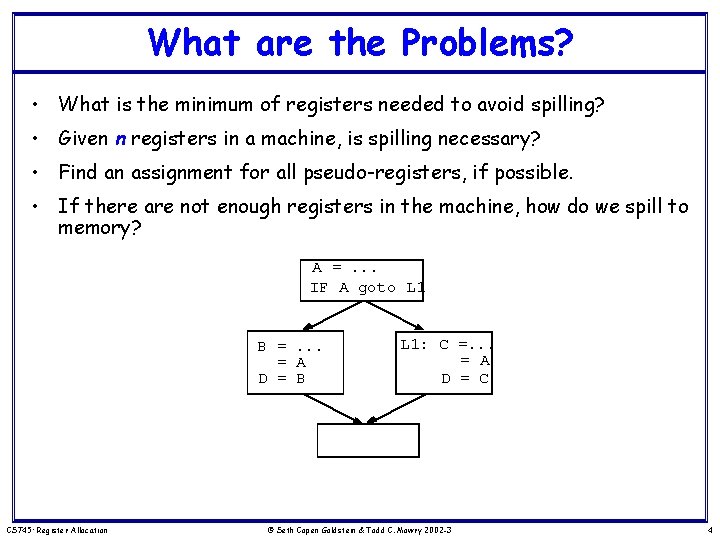

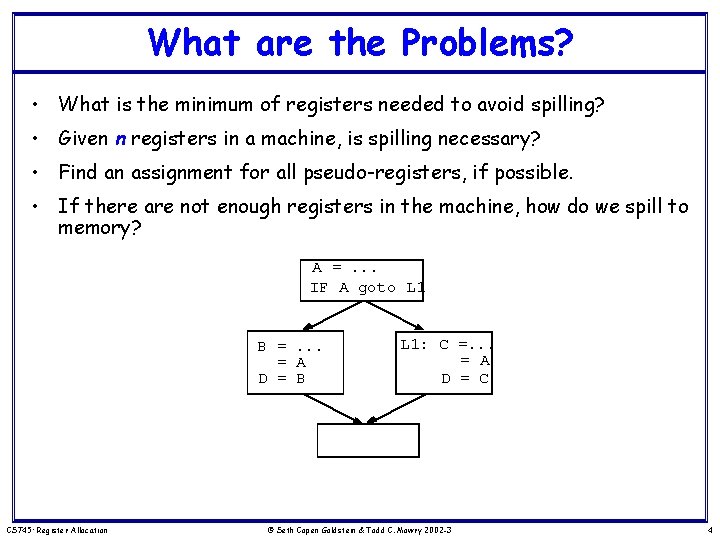

What are the Problems? • What is the minimum of registers needed to avoid spilling? • Given n registers in a machine, is spilling necessary? • Find an assignment for all pseudo-registers, if possible. • If there are not enough registers in the machine, how do we spill to memory? A =. . . IF A goto L 1 B =. . . = A D = B CS 745: Register Allocation L 1: C =. . . = A D = C © Seth Copen Goldstein & Todd C. Mowry 2002 -3 4

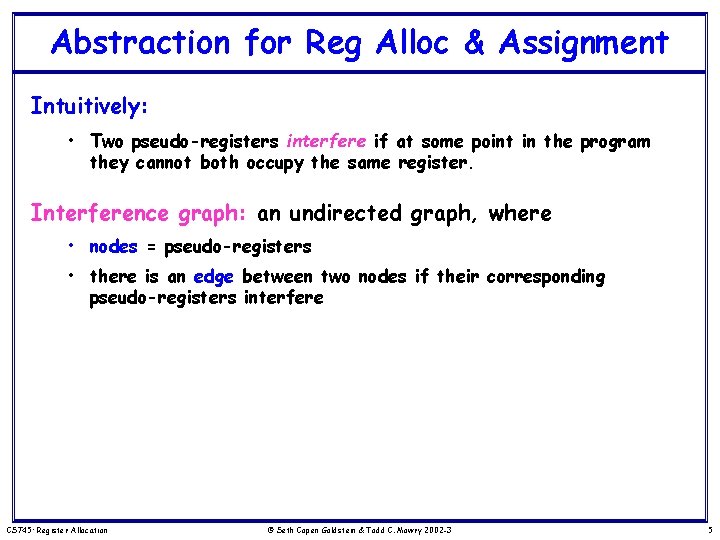

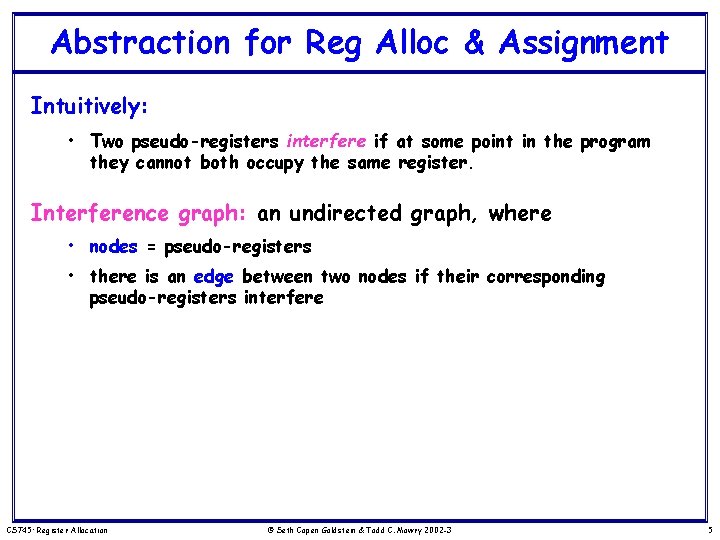

Abstraction for Reg Alloc & Assignment Intuitively: • Two pseudo-registers interfere if at some point in the program they cannot both occupy the same register. Interference graph: an undirected graph, where • nodes = pseudo-registers • there is an edge between two nodes if their corresponding pseudo-registers interfere CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 5

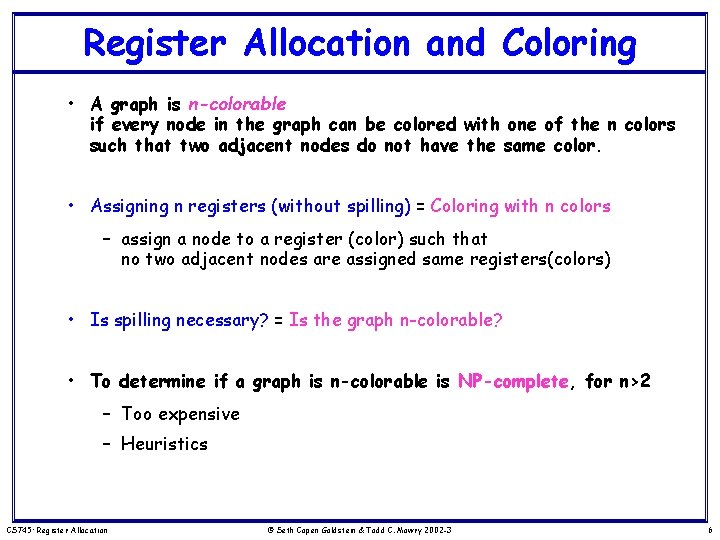

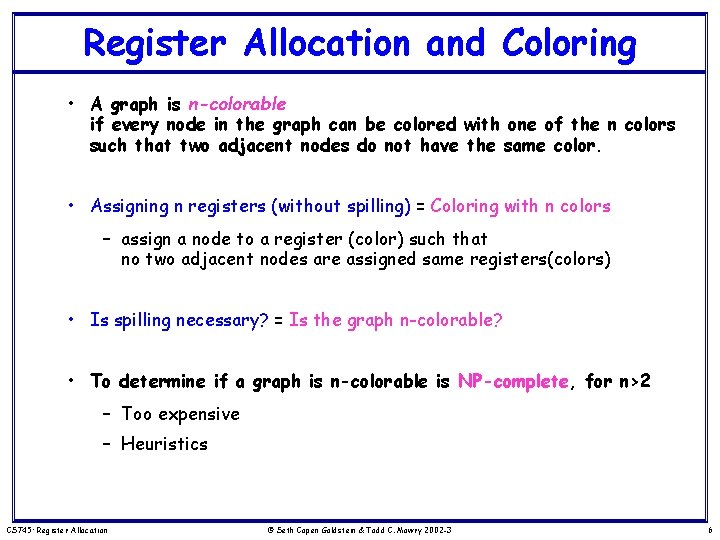

Register Allocation and Coloring • A graph is n-colorable if every node in the graph can be colored with one of the n colors such that two adjacent nodes do not have the same color. • Assigning n registers (without spilling) = Coloring with n colors – assign a node to a register (color) such that no two adjacent nodes are assigned same registers(colors) • Is spilling necessary? = Is the graph n-colorable? • To determine if a graph is n-colorable is NP-complete, for n>2 – Too expensive – Heuristics CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 6

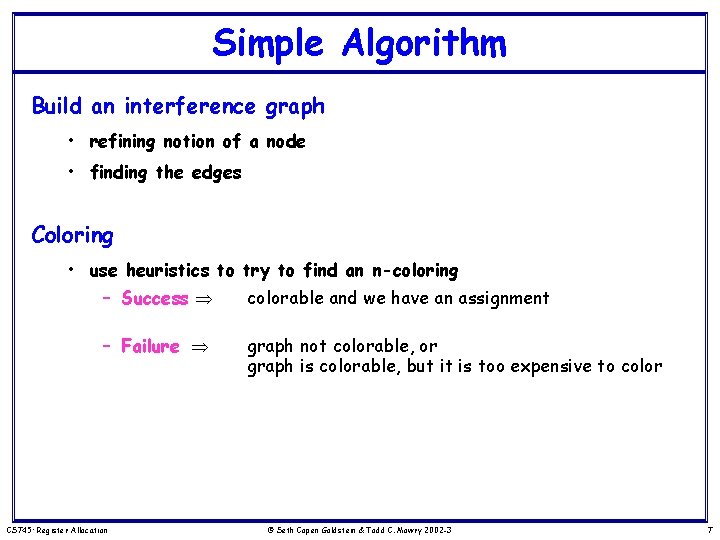

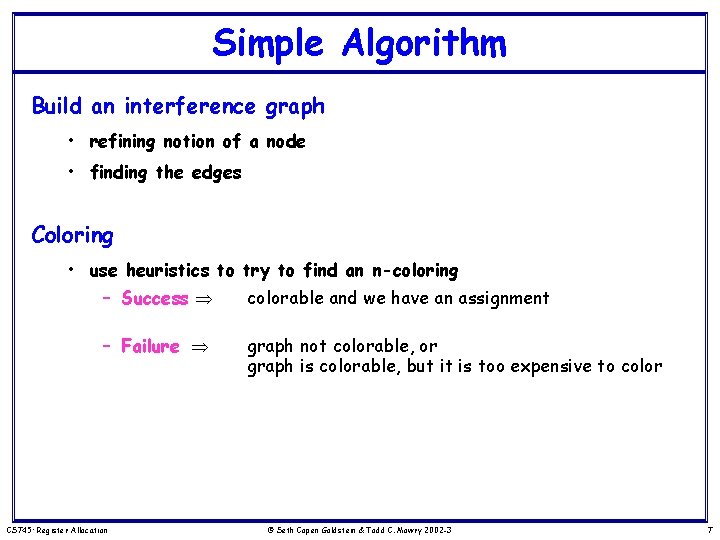

Simple Algorithm Build an interference graph • refining notion of a node • finding the edges Coloring • use heuristics to try to find an n-coloring – Success colorable and we have an assignment – Failure CS 745: Register Allocation graph not colorable, or graph is colorable, but it is too expensive to color © Seth Copen Goldstein & Todd C. Mowry 2002 -3 7

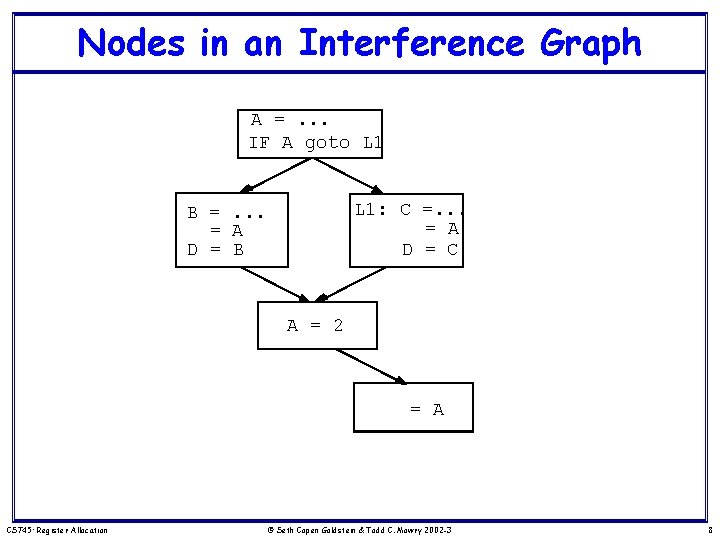

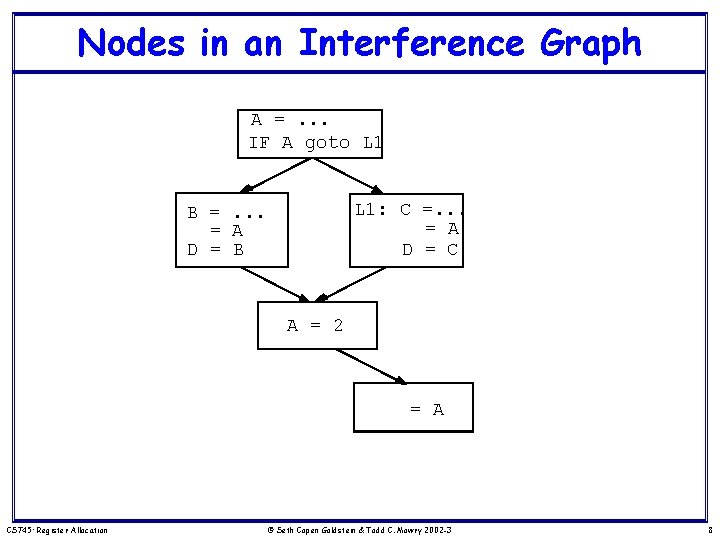

Nodes in an Interference Graph A =. . . IF A goto L 1: C =. . . = A D = C B =. . . = A D = B A = 2 = A CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 8

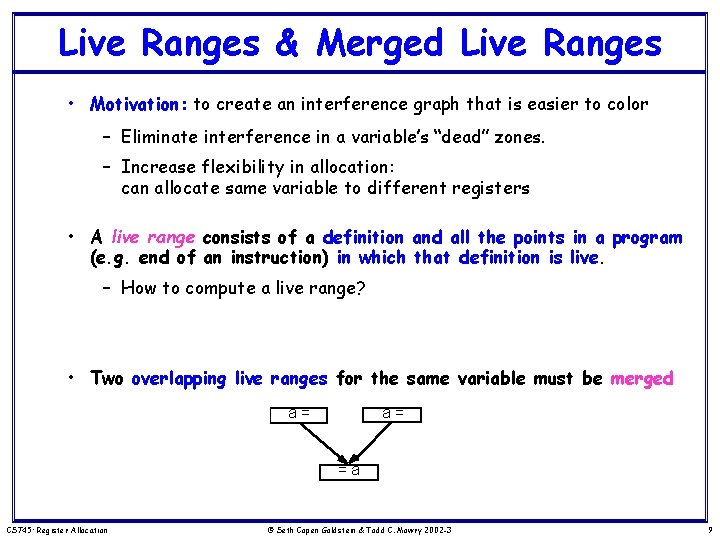

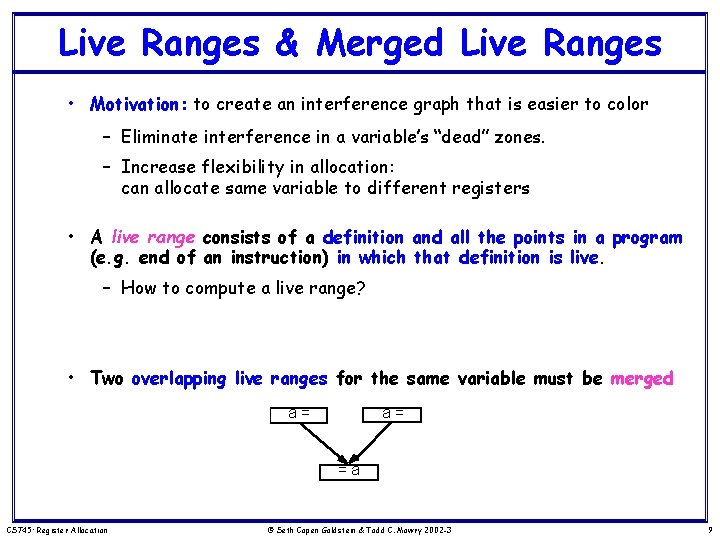

Live Ranges & Merged Live Ranges • Motivation: to create an interference graph that is easier to color – Eliminate interference in a variable’s “dead” zones. – Increase flexibility in allocation: can allocate same variable to different registers • A live range consists of a definition and all the points in a program (e. g. end of an instruction) in which that definition is live. – How to compute a live range? • Two overlapping live ranges for the same variable must be merged a= a= =a CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 9

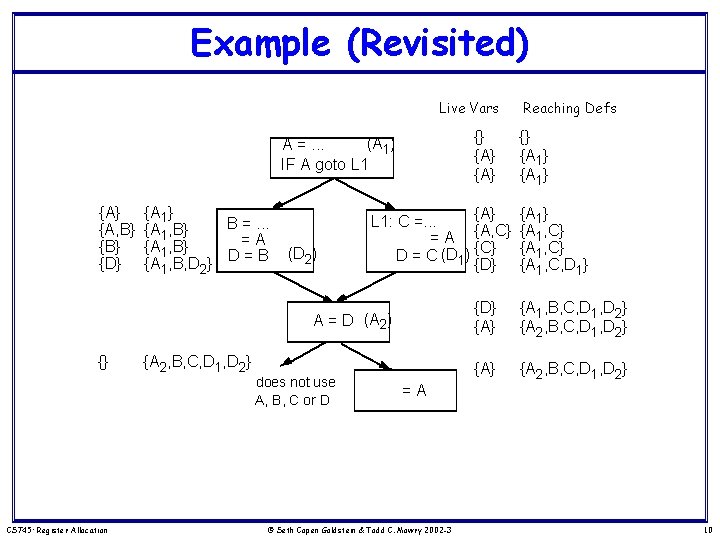

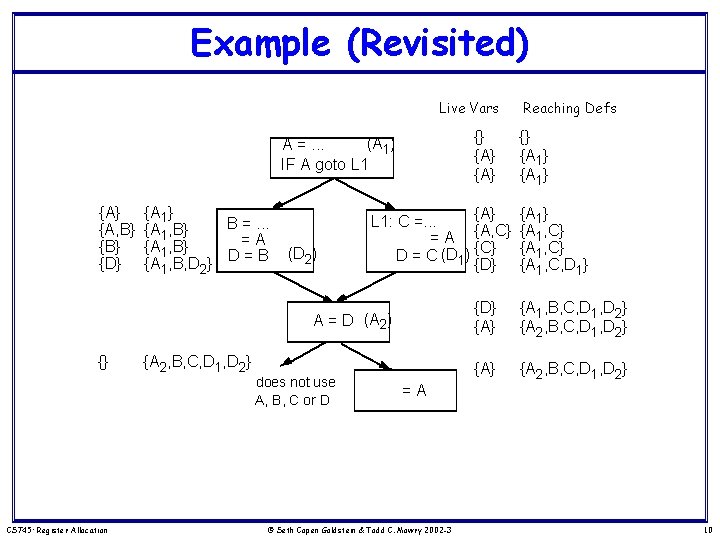

Example (Revisited) Live Vars {} {A} (A 1) A =. . . IF A goto L 1 {A} {A, B} {D} {A 1} B =. . . {A 1, B} =A {A 1, B} {A 1 , B, D 2} D = B (D 2) {A} L 1: C =. . . = A {A, C} {C} D = C (D 1) {D} A = D (A 2) {} CS 745: Register Allocation {A 2 , B, C, D 1 , D 2} does not use A, B, C or D =A © Seth Copen Goldstein & Todd C. Mowry 2002 -3 Reaching Defs {} {A 1} {A 1, C} {A 1 , C, D 1} {D} {A 1 , B, C, D 1 , D 2} {A 2 , B, C, D 1 , D 2} 10

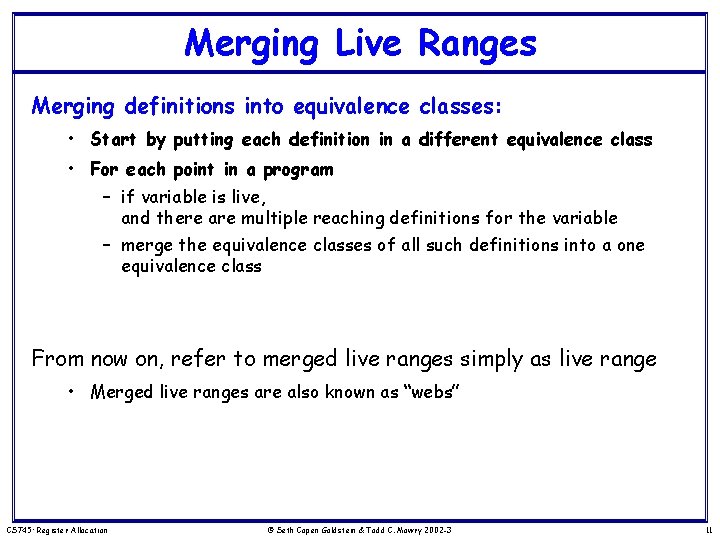

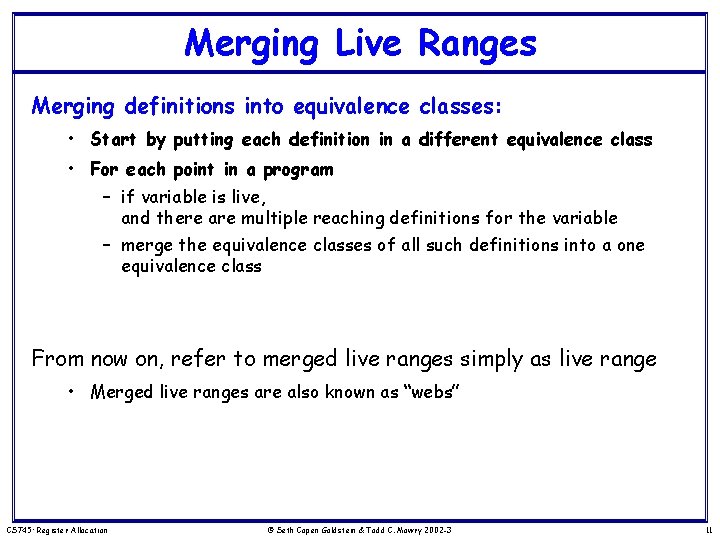

Merging Live Ranges Merging definitions into equivalence classes: • Start by putting each definition in a different equivalence class • For each point in a program – if variable is live, and there are multiple reaching definitions for the variable – merge the equivalence classes of all such definitions into a one equivalence class From now on, refer to merged live ranges simply as live range • Merged live ranges are also known as “webs” CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 11

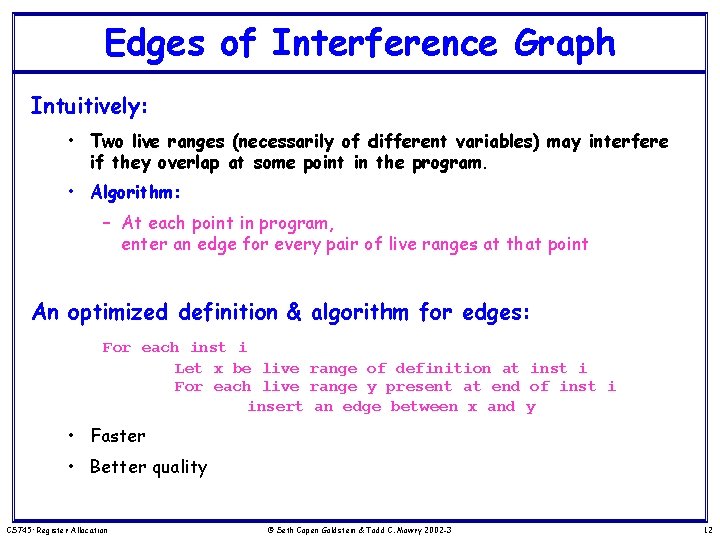

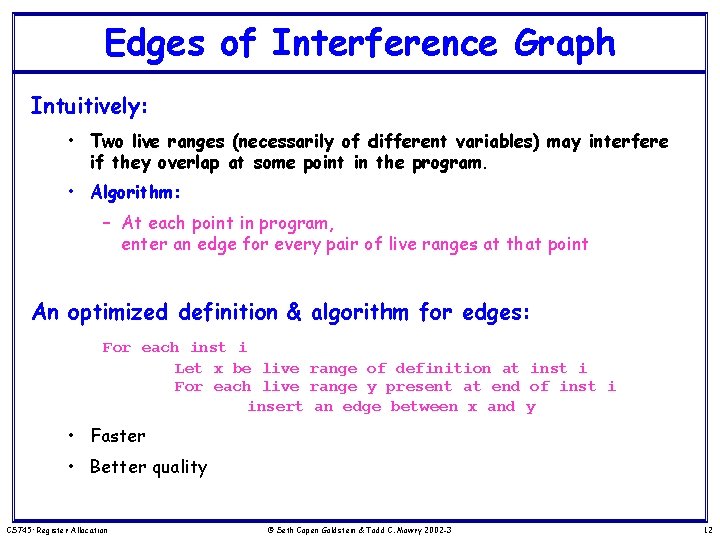

Edges of Interference Graph Intuitively: • Two live ranges (necessarily of different variables) may interfere if they overlap at some point in the program. • Algorithm: – At each point in program, enter an edge for every pair of live ranges at that point An optimized definition & algorithm for edges: For each inst i Let x be live range of definition at inst i For each live range y present at end of inst i insert an edge between x and y • Faster • Better quality CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 12

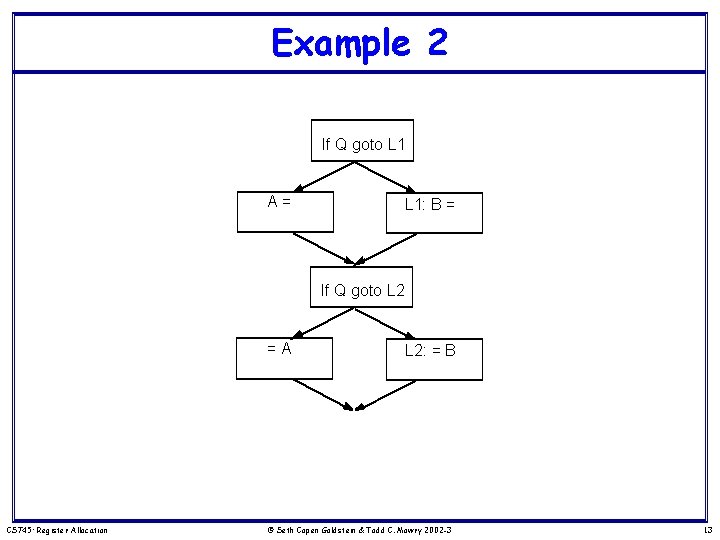

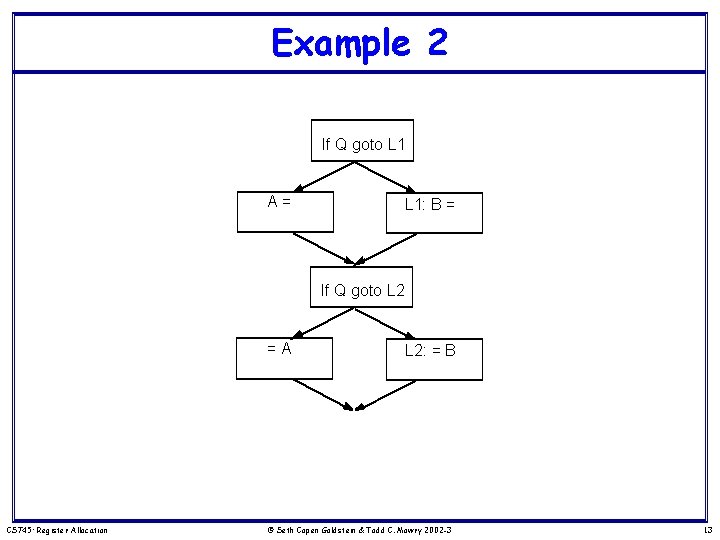

Example 2 If Q goto L 1 A= L 1: B = If Q goto L 2 =A CS 745: Register Allocation L 2: = B © Seth Copen Goldstein & Todd C. Mowry 2002 -3 13

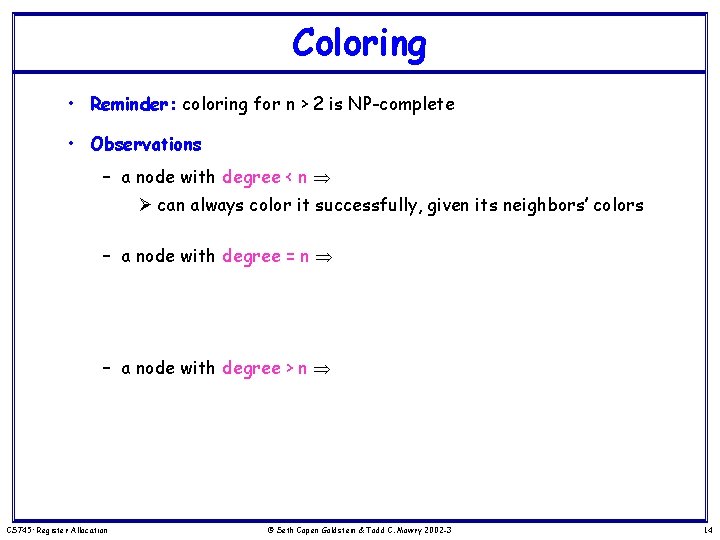

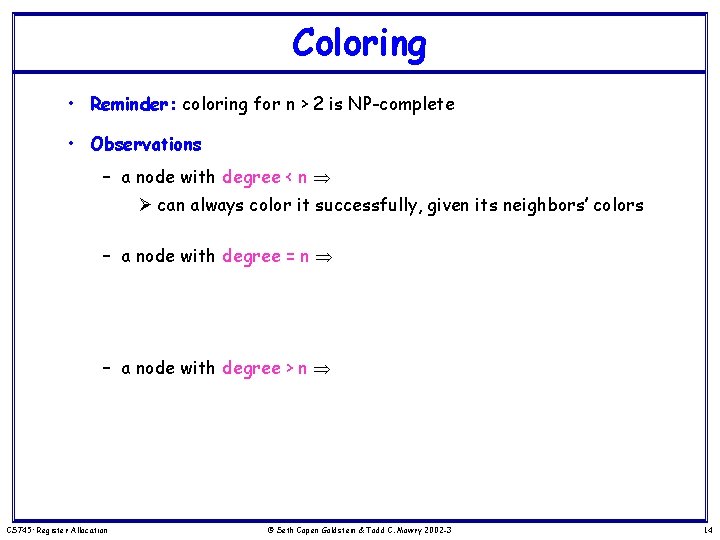

Coloring • Reminder: coloring for n > 2 is NP-complete • Observations – a node with degree < n Ø can always color it successfully, given its neighbors’ colors – a node with degree = n – a node with degree > n CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 14

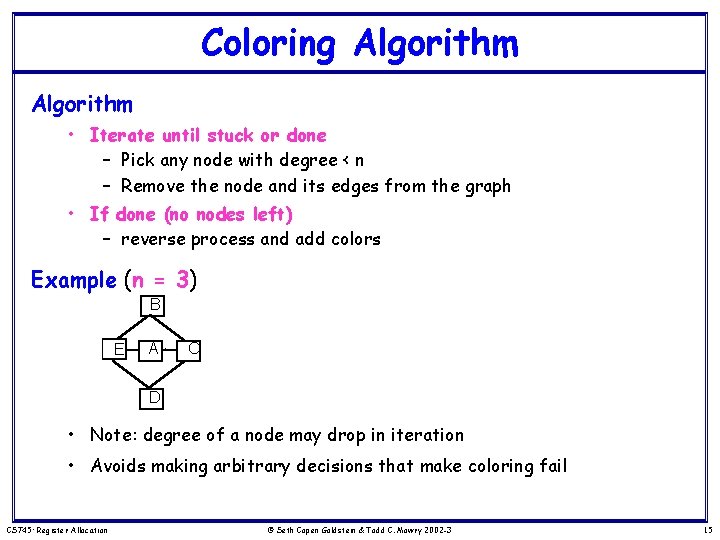

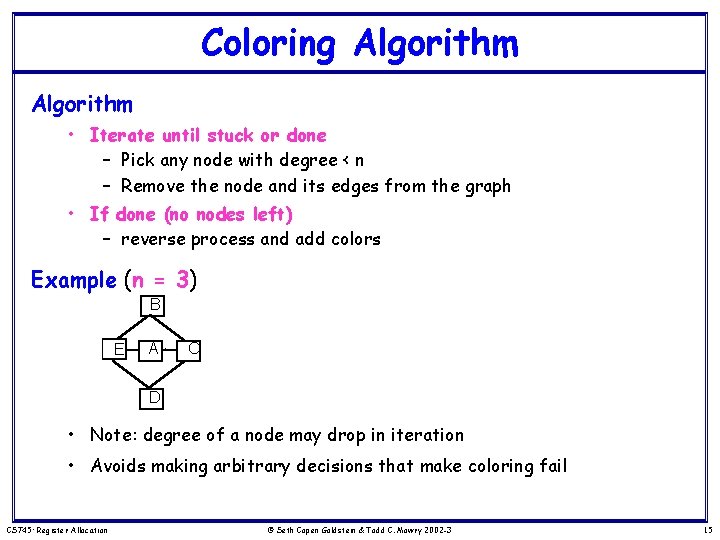

Coloring Algorithm • Iterate until stuck or done – Pick any node with degree < n – Remove the node and its edges from the graph • If done (no nodes left) – reverse process and add colors Example (n = 3) B E A C D • Note: degree of a node may drop in iteration • Avoids making arbitrary decisions that make coloring fail CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 15

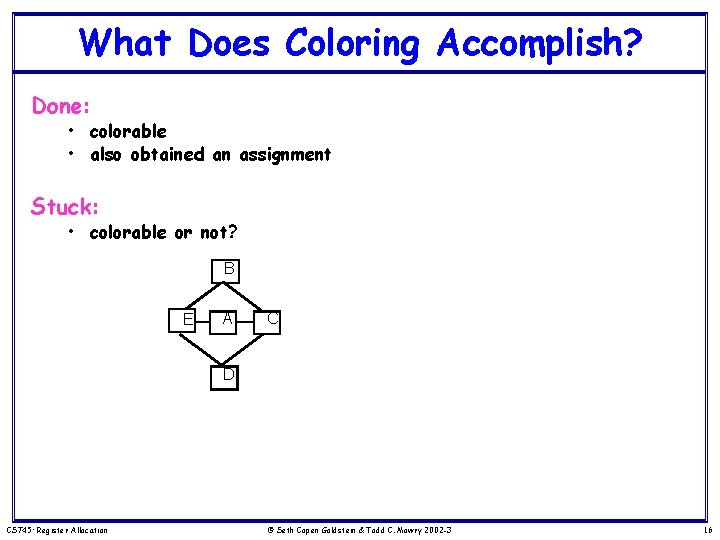

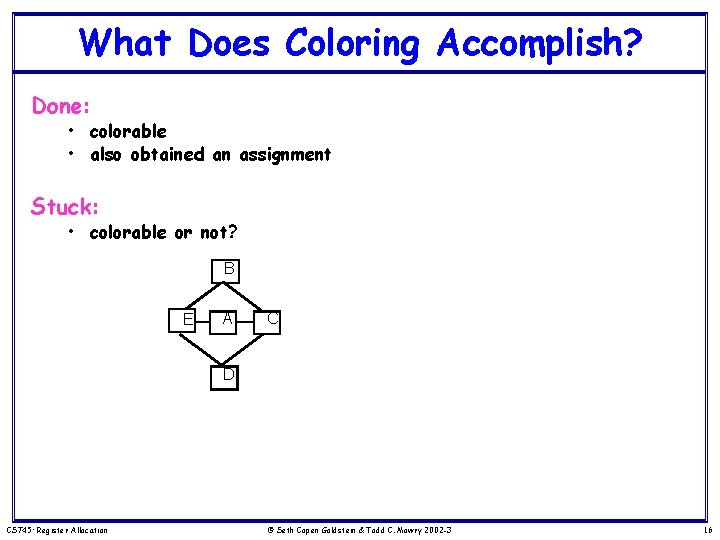

What Does Coloring Accomplish? Done: • colorable • also obtained an assignment Stuck: • colorable or not? B E A C D CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 16

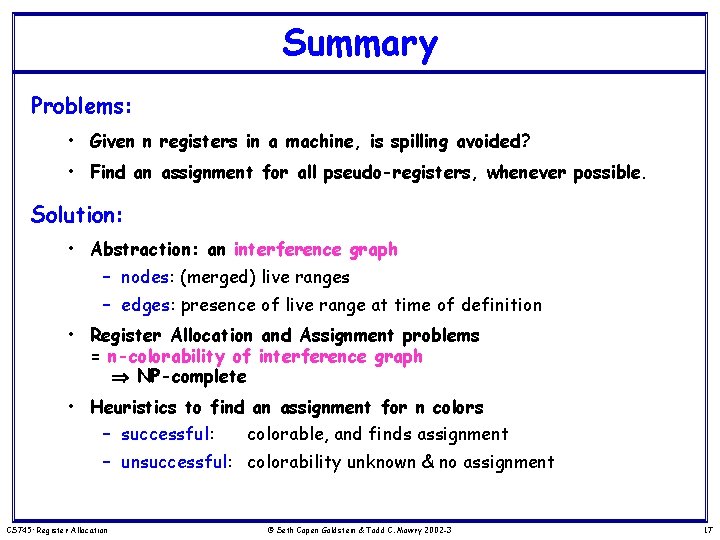

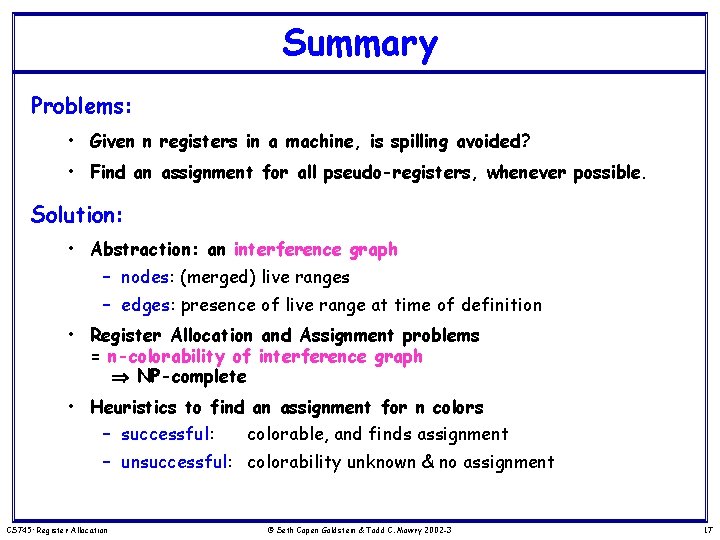

Summary Problems: • Given n registers in a machine, is spilling avoided? • Find an assignment for all pseudo-registers, whenever possible. Solution: • Abstraction: an interference graph – nodes: (merged) live ranges – edges: presence of live range at time of definition • Register Allocation and Assignment problems = n-colorability of interference graph NP-complete • Heuristics to find an assignment for n colors – successful: colorable, and finds assignment – unsuccessful: colorability unknown & no assignment CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 17

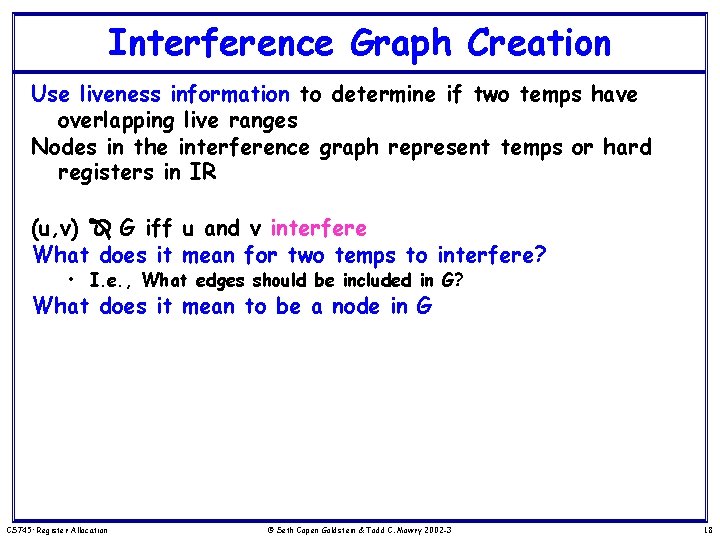

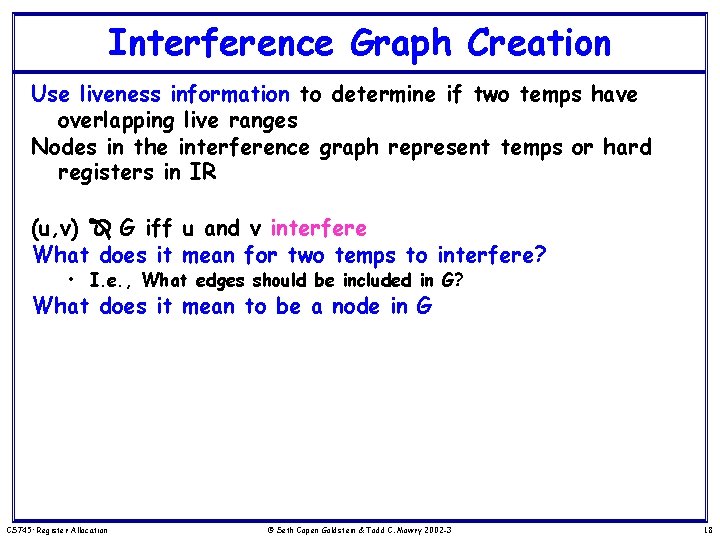

Interference Graph Creation Use liveness information to determine if two temps have overlapping live ranges Nodes in the interference graph represent temps or hard registers in IR (u, v) G iff u and v interfere What does it mean for two temps to interfere? • I. e. , What edges should be included in G? What does it mean to be a node in G CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 18

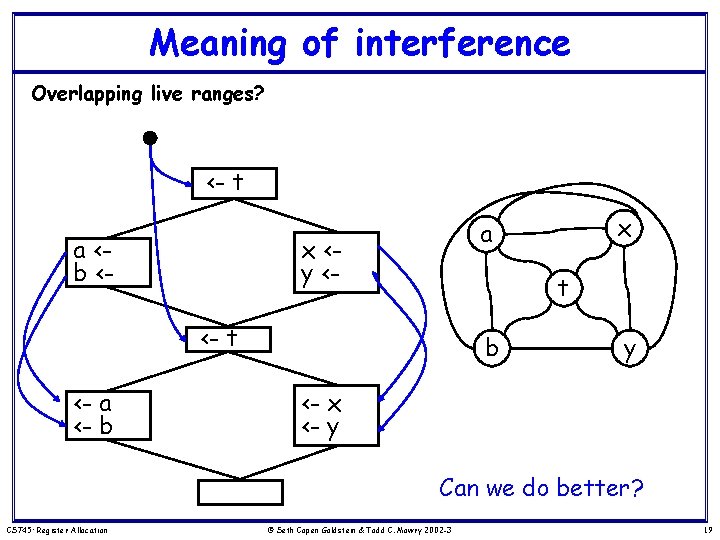

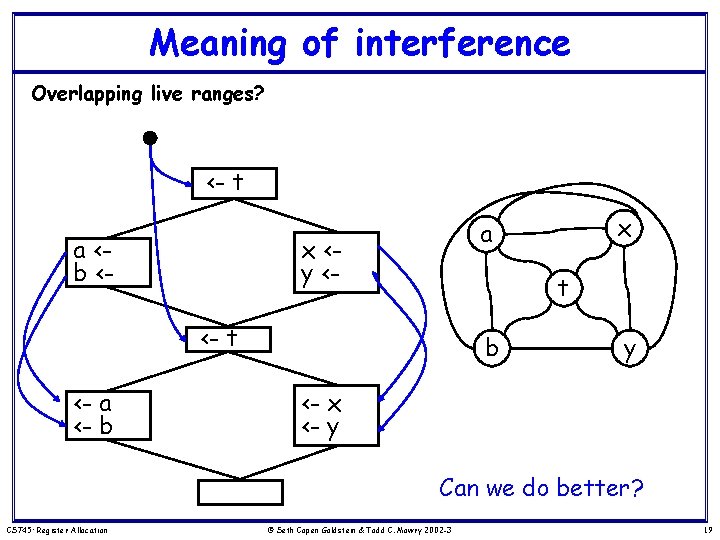

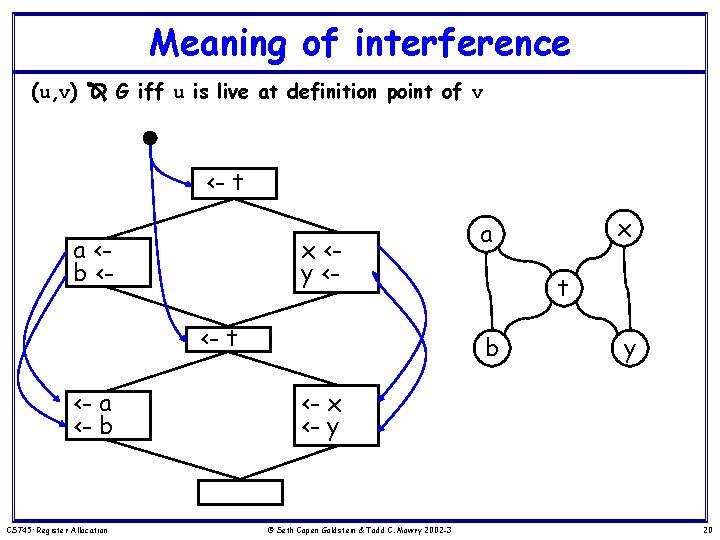

Meaning of interference Overlapping live ranges? <- t a <b <- x <y <- t <- a <- b x a b y <- x <- y Can we do better? CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 19

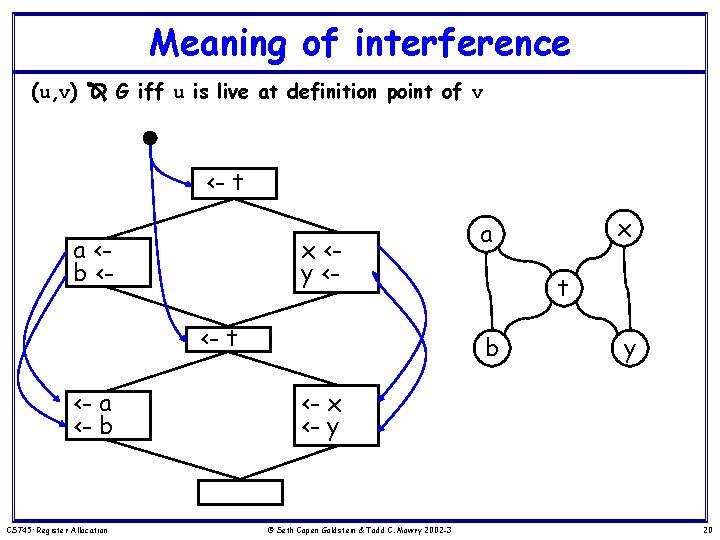

Meaning of interference (u, v) G iff u is live at definition point of v <- t a <b <- x <y <<- t <- a <- b CS 745: Register Allocation x a t b y <- x <- y © Seth Copen Goldstein & Todd C. Mowry 2002 -3 20

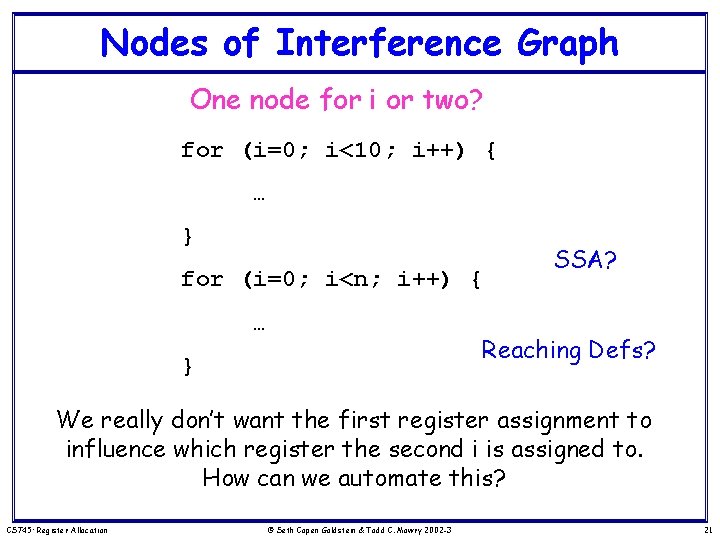

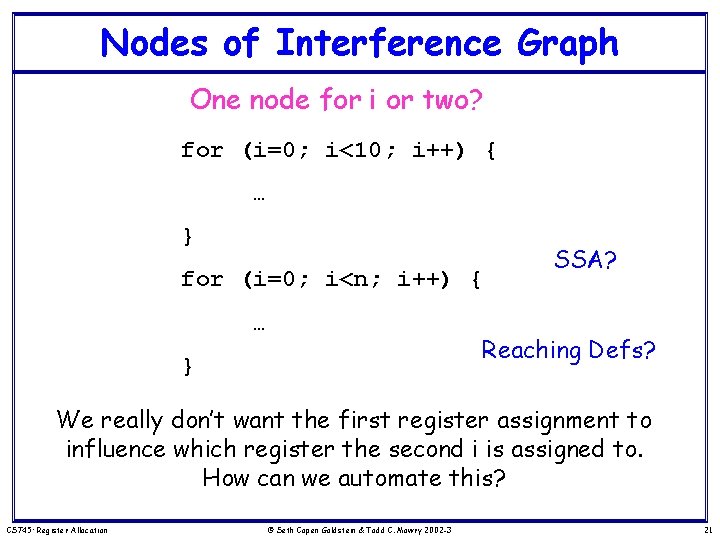

Nodes of Interference Graph One node for i or two? for (i=0; i<10; i++) { … } for (i=0; i<n; i++) { … SSA? Reaching Defs? } We really don’t want the first register assignment to influence which register the second i is assigned to. How can we automate this? CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 21

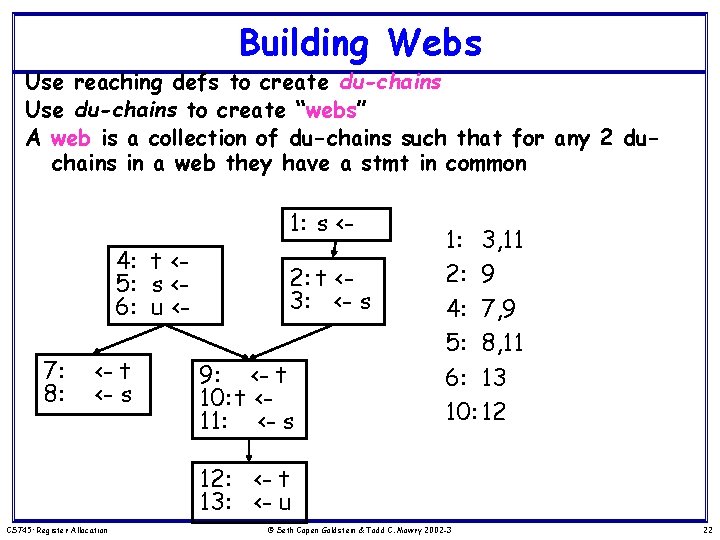

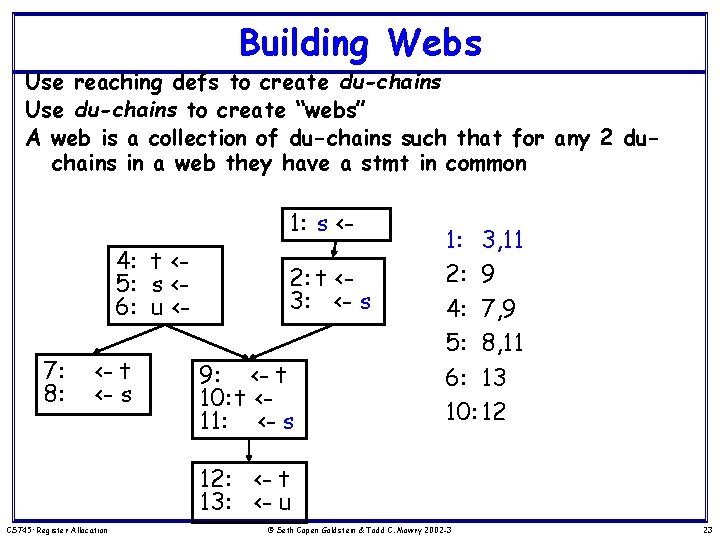

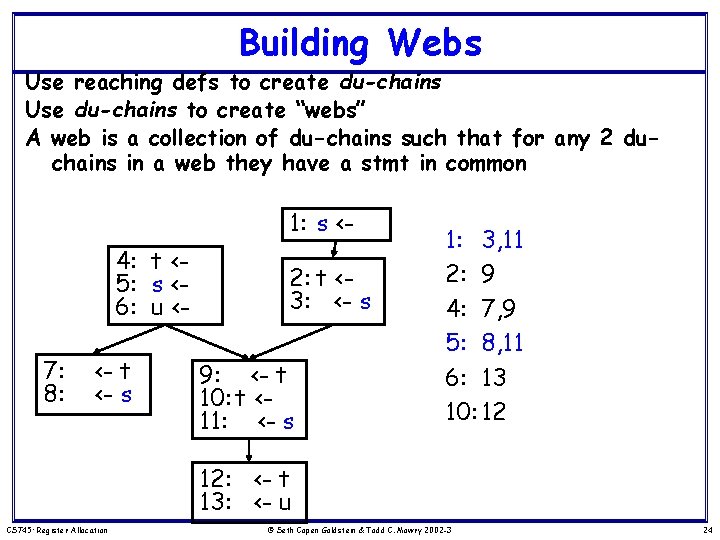

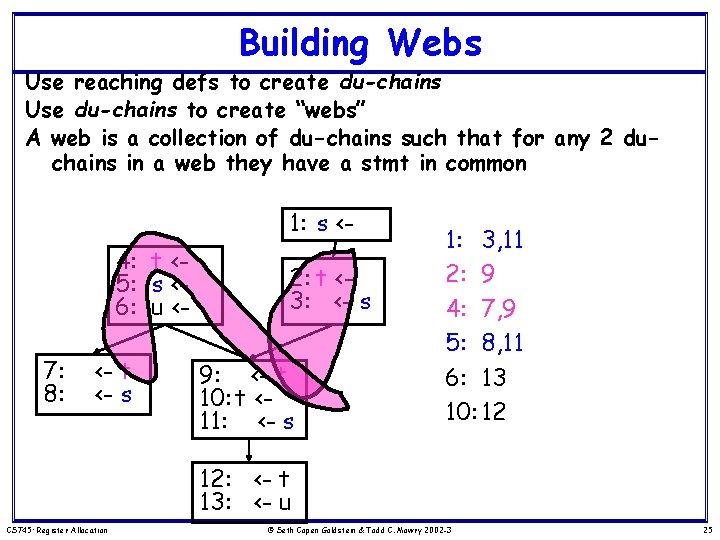

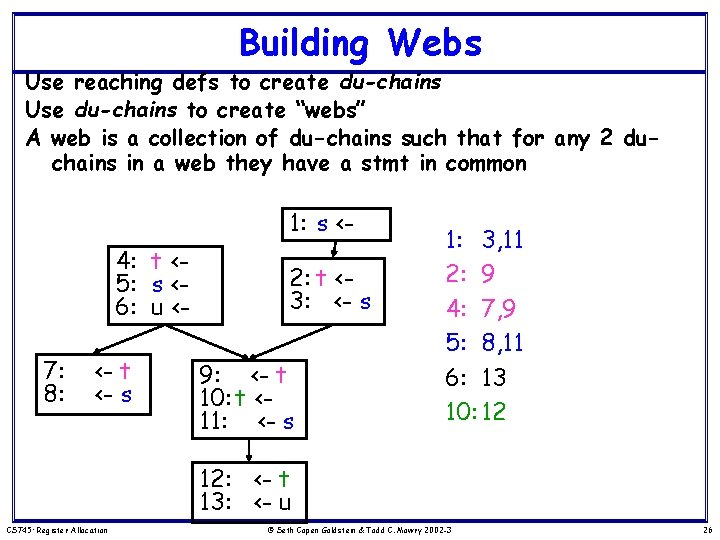

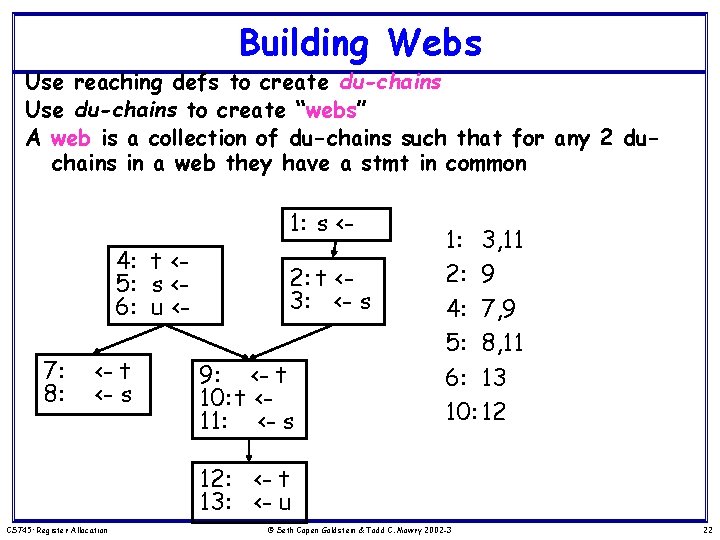

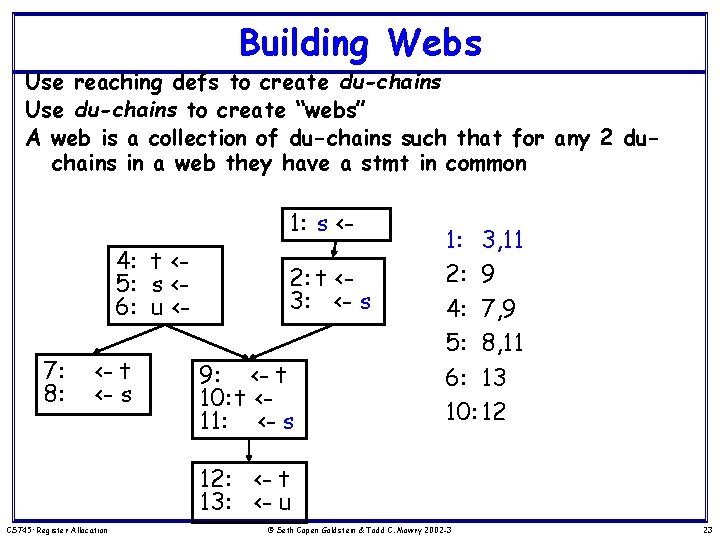

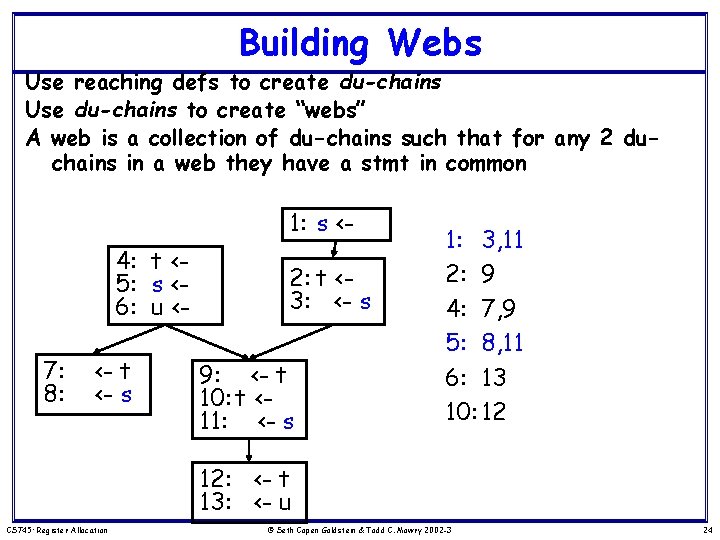

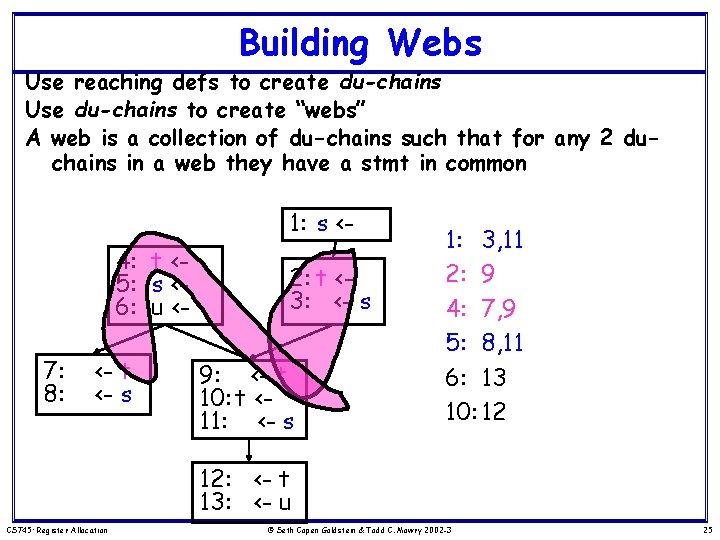

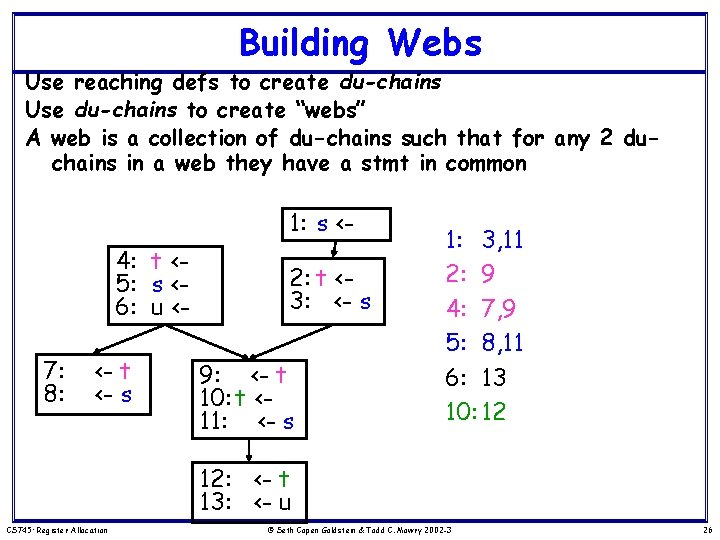

Building Webs Use reaching defs to create du-chains Use du-chains to create “webs” A web is a collection of du-chains such that for any 2 duchains in a web they have a stmt in common 1: s <4: t <5: s <6: u <7: 8: <- t <- s 2: t <3: <- s 9: <- t 10: t <11: <- s 1: 3, 11 2: 9 4: 7, 9 5: 8, 11 6: 13 10: 12 12: <- t 13: <- u CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 22

Building Webs Use reaching defs to create du-chains Use du-chains to create “webs” A web is a collection of du-chains such that for any 2 duchains in a web they have a stmt in common 1: s <4: t <5: s <6: u <7: 8: <- t <- s 2: t <3: <- s 9: <- t 10: t <11: <- s 1: 3, 11 2: 9 4: 7, 9 5: 8, 11 6: 13 10: 12 12: <- t 13: <- u CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 23

Building Webs Use reaching defs to create du-chains Use du-chains to create “webs” A web is a collection of du-chains such that for any 2 duchains in a web they have a stmt in common 1: s <4: t <5: s <6: u <7: 8: <- t <- s 2: t <3: <- s 9: <- t 10: t <11: <- s 1: 3, 11 2: 9 4: 7, 9 5: 8, 11 6: 13 10: 12 12: <- t 13: <- u CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 24

Building Webs Use reaching defs to create du-chains Use du-chains to create “webs” A web is a collection of du-chains such that for any 2 duchains in a web they have a stmt in common 1: s <4: t <5: s <6: u <7: 8: <- t <- s 2: t <3: <- s 9: <- t 10: t <11: <- s 1: 3, 11 2: 9 4: 7, 9 5: 8, 11 6: 13 10: 12 12: <- t 13: <- u CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 25

Building Webs Use reaching defs to create du-chains Use du-chains to create “webs” A web is a collection of du-chains such that for any 2 duchains in a web they have a stmt in common 1: s <4: t <5: s <6: u <7: 8: <- t <- s 2: t <3: <- s 9: <- t 10: t <11: <- s 1: 3, 11 2: 9 4: 7, 9 5: 8, 11 6: 13 10: 12 12: <- t 13: <- u CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 26

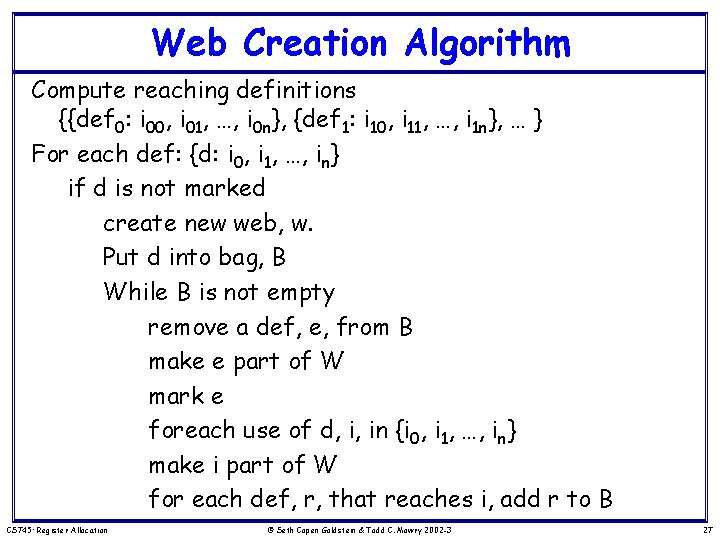

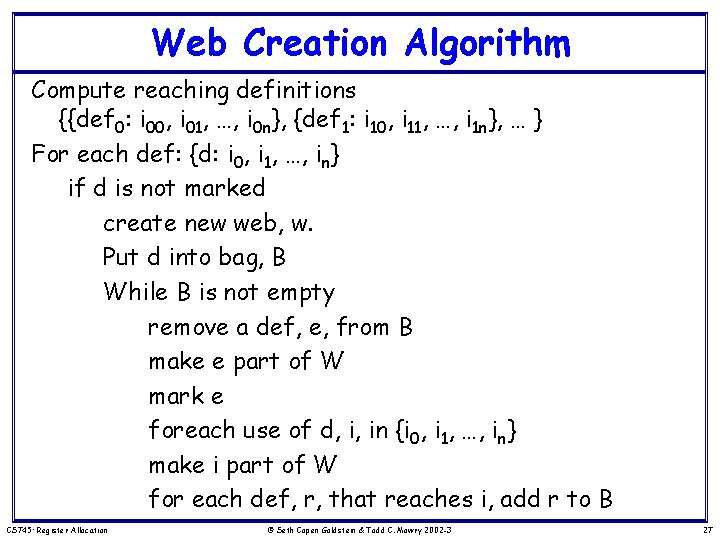

Web Creation Algorithm Compute reaching definitions {{def 0: i 00, i 01, …, i 0 n}, {def 1: i 10, i 11, …, i 1 n}, … } For each def: {d: i 0, i 1, …, in} if d is not marked create new web, w. Put d into bag, B While B is not empty remove a def, e, from B make e part of W mark e foreach use of d, i, in {i 0, i 1, …, in} make i part of W for each def, r, that reaches i, add r to B CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 27

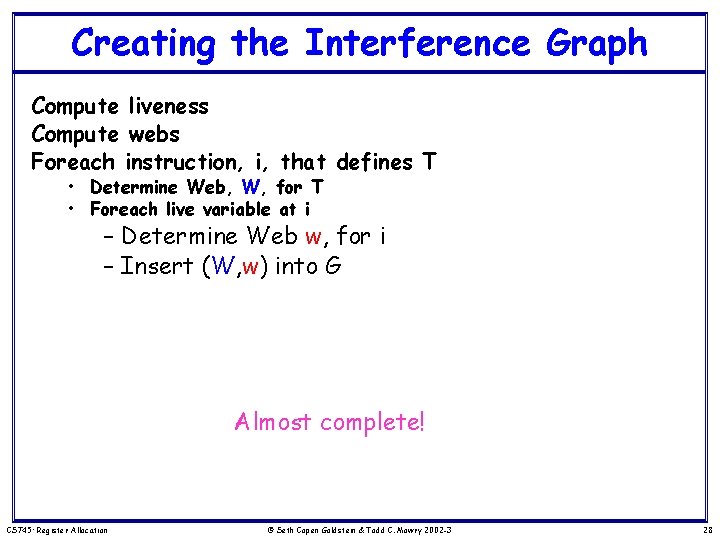

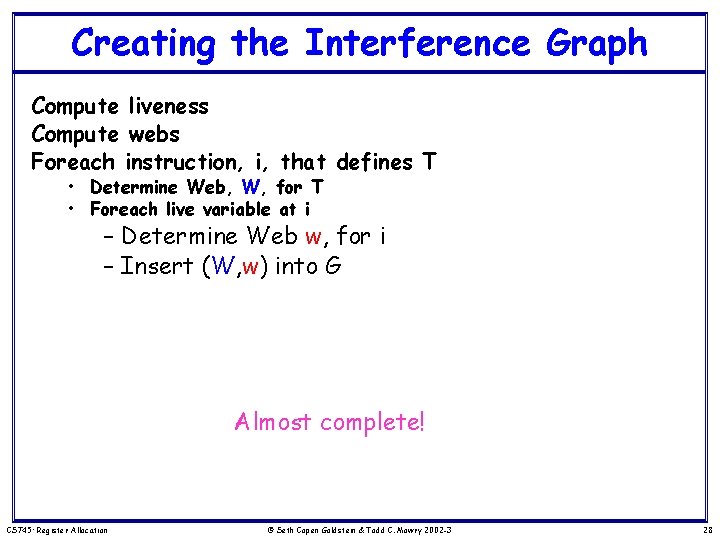

Creating the Interference Graph Compute liveness Compute webs Foreach instruction, i, that defines T • Determine Web, W, for T • Foreach live variable at i – Determine Web w, for i – Insert (W, w) into G Almost complete! CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 28

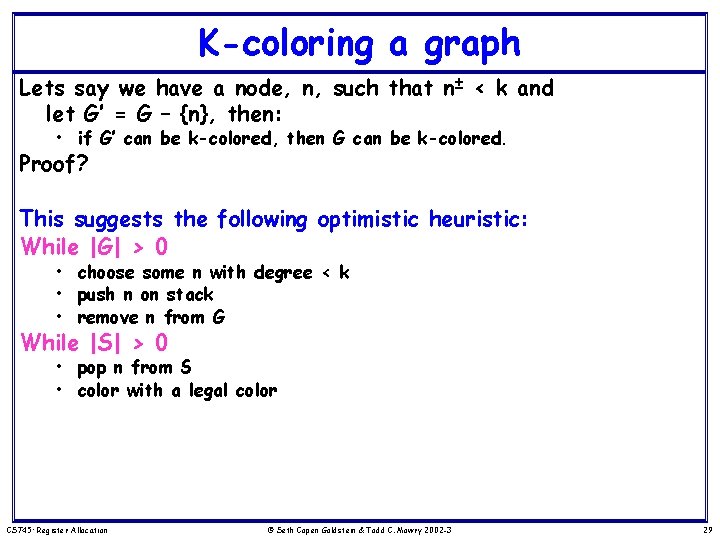

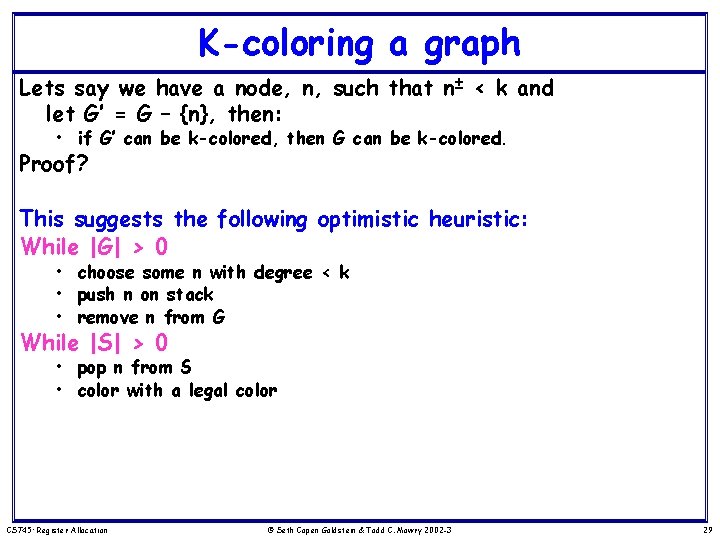

K-coloring a graph Lets say we have a node, n, such that n± < k and let G’ = G – {n}, then: • if G’ can be k-colored, then G can be k-colored. Proof? This suggests the following optimistic heuristic: While |G| > 0 • choose some n with degree < k • push n on stack • remove n from G While |S| > 0 • pop n from S • color with a legal color CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 29

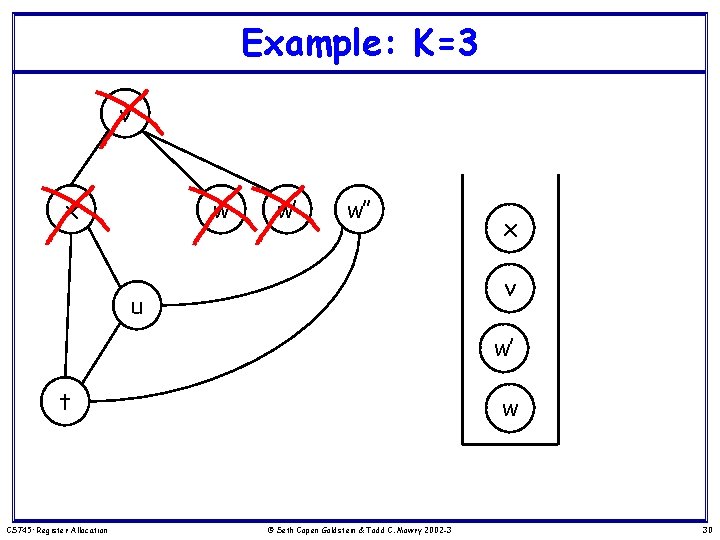

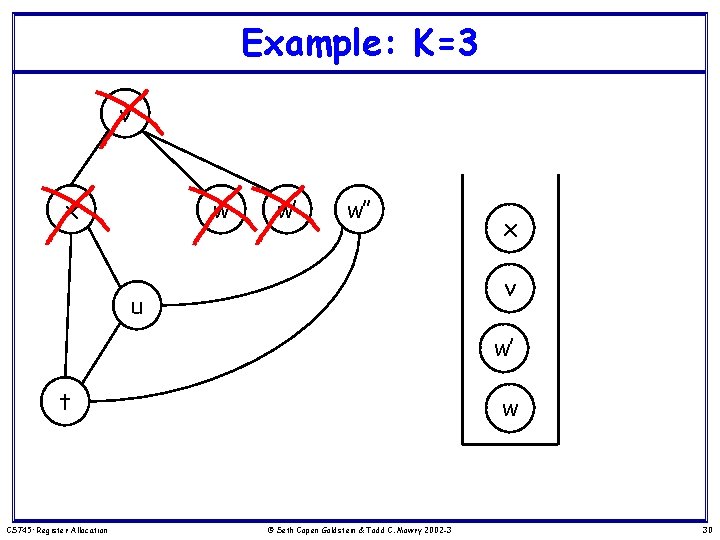

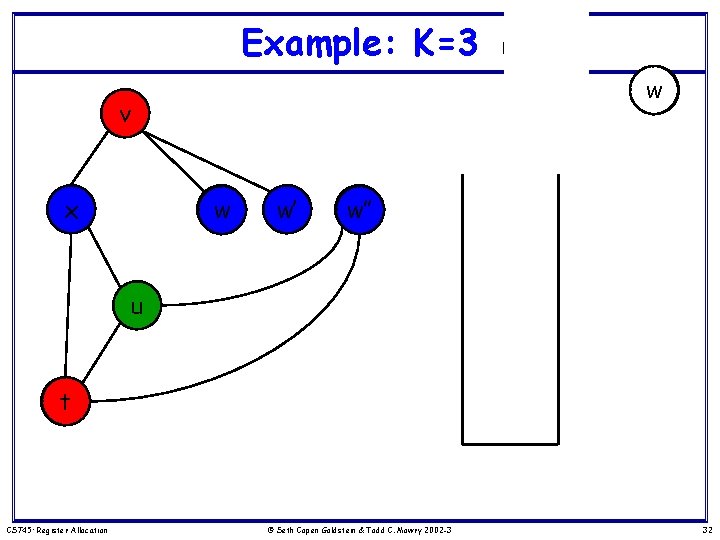

Example: K=3 v x w w’ w’’ x v u w’ t CS 745: Register Allocation w © Seth Copen Goldstein & Todd C. Mowry 2002 -3 30

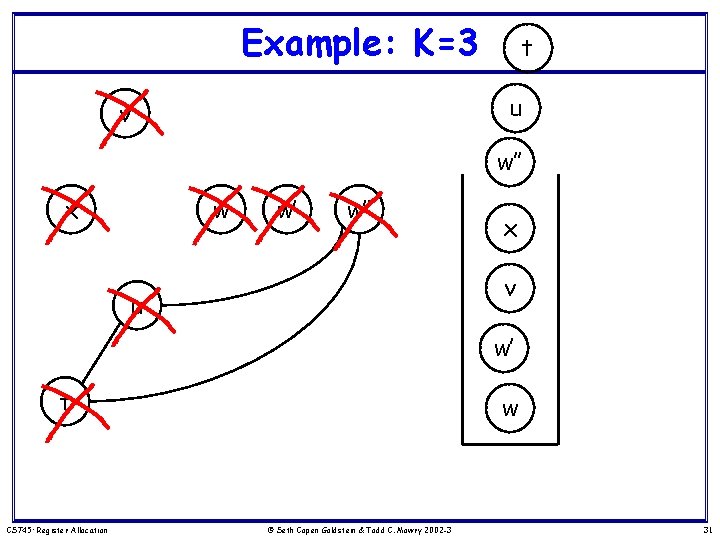

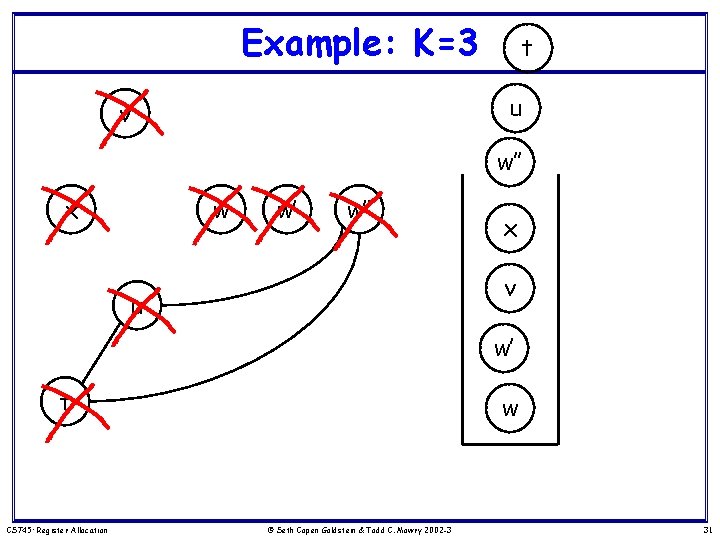

Example: K=3 t u v w’’ x w w’ w’’ x v u w’ t CS 745: Register Allocation w © Seth Copen Goldstein & Todd C. Mowry 2002 -3 31

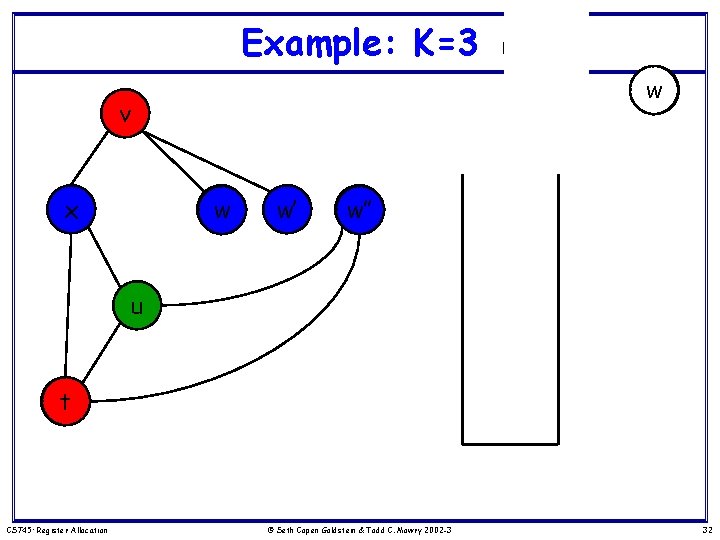

Example: K=3 t u v w’’ w’ w x u vt w’’ x w w’ w’’ x v u w’ t CS 745: Register Allocation w © Seth Copen Goldstein & Todd C. Mowry 2002 -3 32

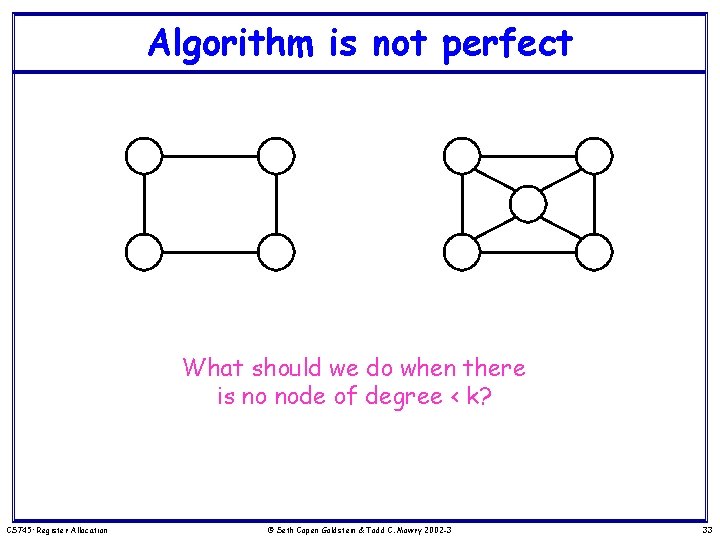

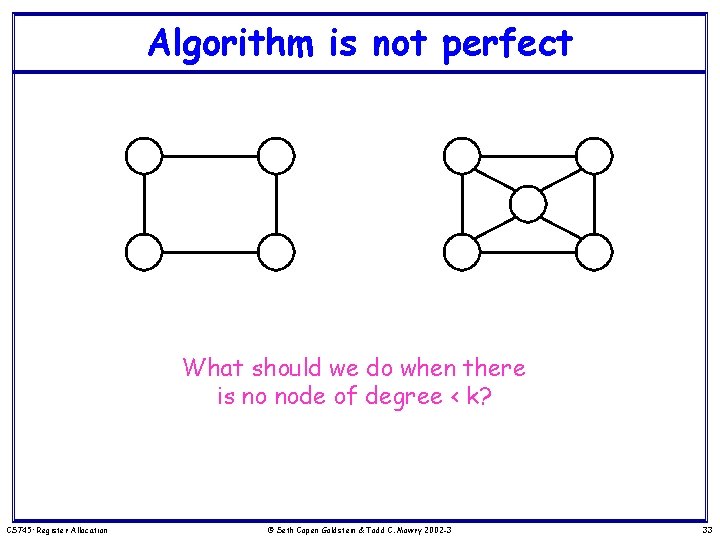

Algorithm is not perfect What should we do when there is no node of degree < k? CS 745: Register Allocation © Seth Copen Goldstein & Todd C. Mowry 2002 -3 33