15 441 Computer Networks Switching Professor Hui Zhang

- Slides: 32

15 -441 Computer Networks Switching Professor Hui Zhang hzhang@cs. cmu. edu 1

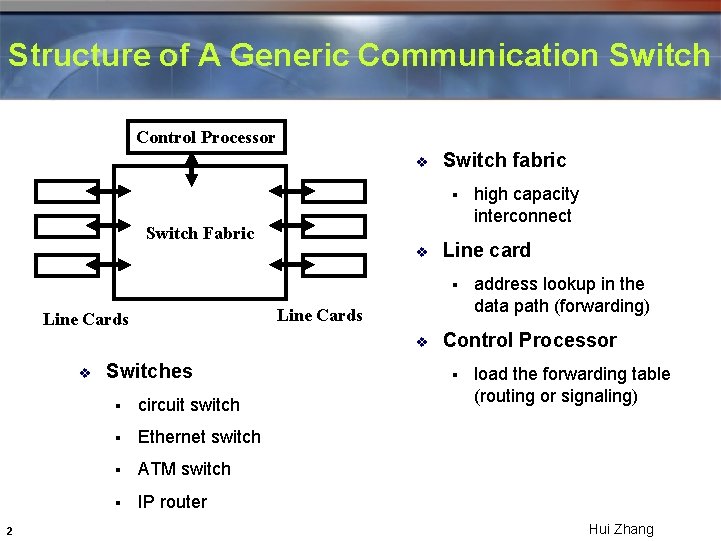

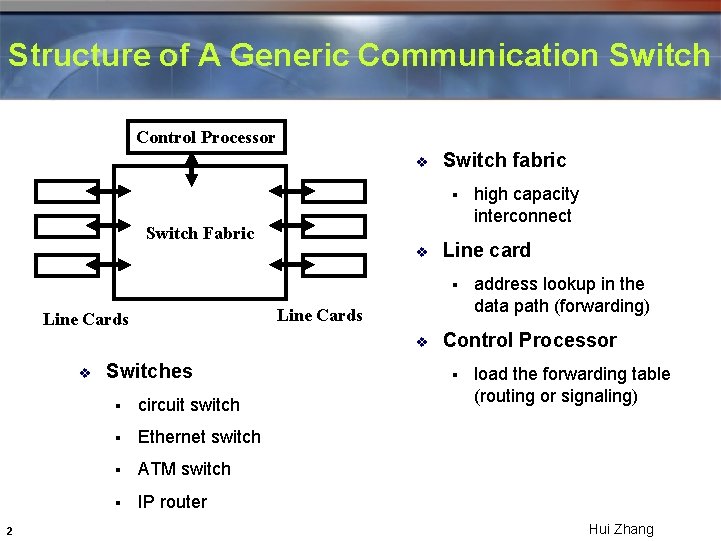

Structure of A Generic Communication Switch Control Processor v Switch fabric § Switch Fabric v Line card § Line Cards v v 2 Switches § circuit switch § Ethernet switch § ATM switch § IP router high capacity interconnect address lookup in the data path (forwarding) Control Processor § load the forwarding table (routing or signaling) Hui Zhang

Switches/Routers v Control plane: how forwarding tables are computed – Router: routing protocols – Ethernet switch: learning and spanning tree v 3 Data plane: how each packet is processed? § Header lookup and forward the packet to right output port § Manage buffer and bandwidth resource Hui Zhang

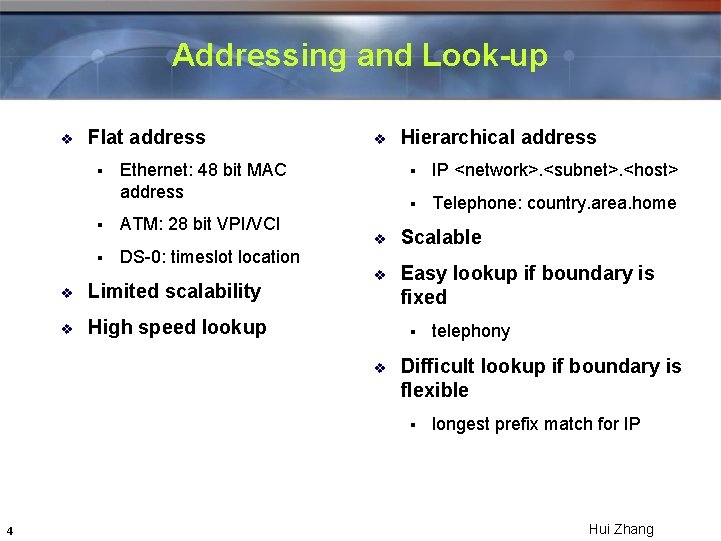

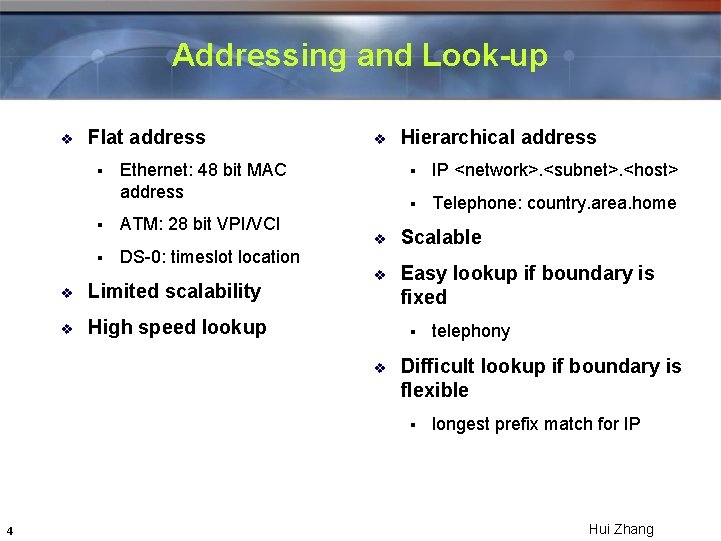

Addressing and Look-up v Flat address § v Ethernet: 48 bit MAC address § ATM: 28 bit VPI/VCI § DS-0: timeslot location v Limited scalability v High speed lookup Hierarchical address § IP <network>. <subnet>. <host> § Telephone: country. area. home v Scalable v Easy lookup if boundary is fixed § v Difficult lookup if boundary is flexible § 4 telephony longest prefix match for IP Hui Zhang

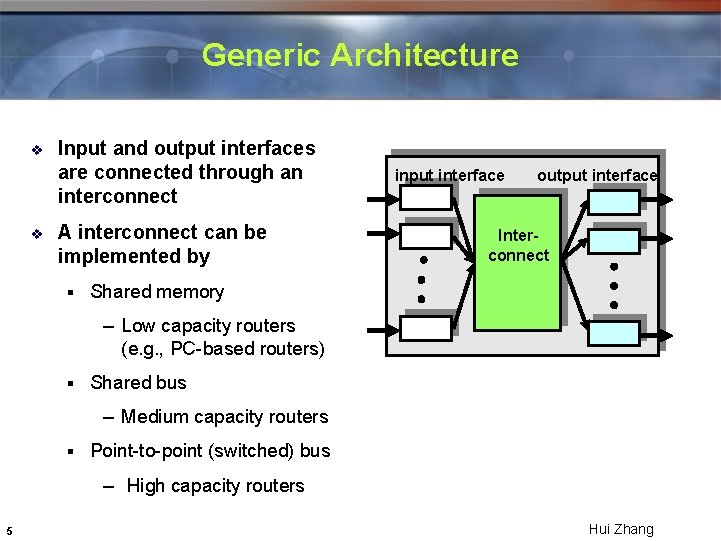

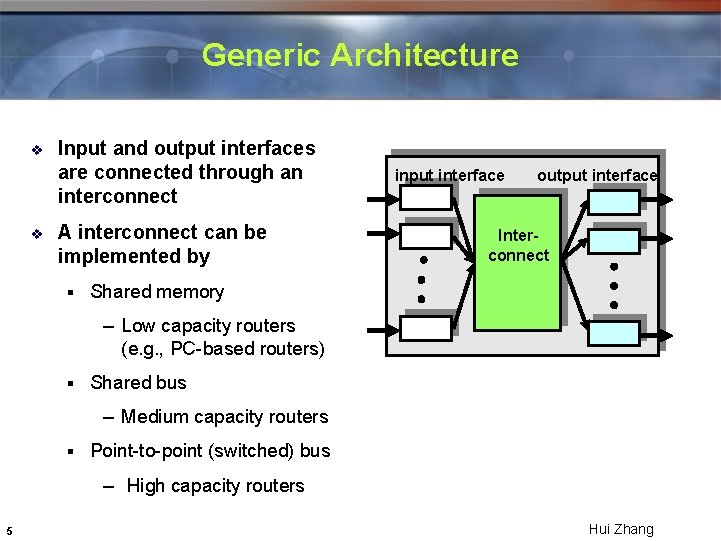

Generic Architecture v v Input and output interfaces are connected through an interconnect A interconnect can be implemented by § input interface output interface Interconnect Shared memory – Low capacity routers (e. g. , PC-based routers) § Shared bus – Medium capacity routers § Point-to-point (switched) bus – High capacity routers 5 Hui Zhang

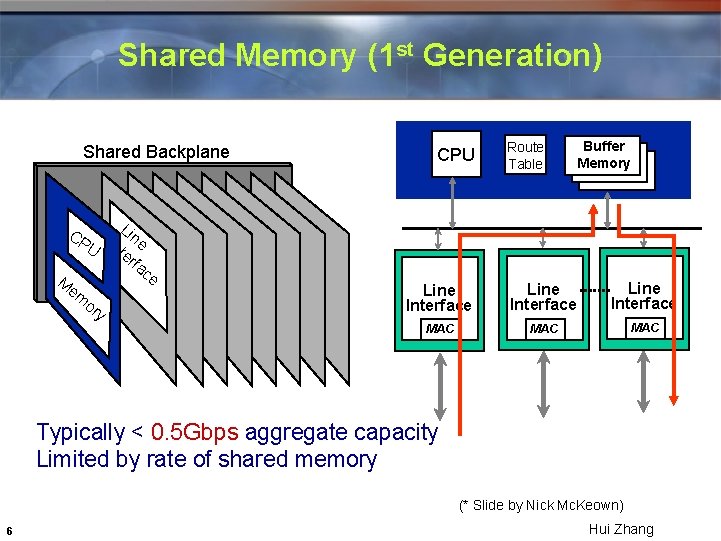

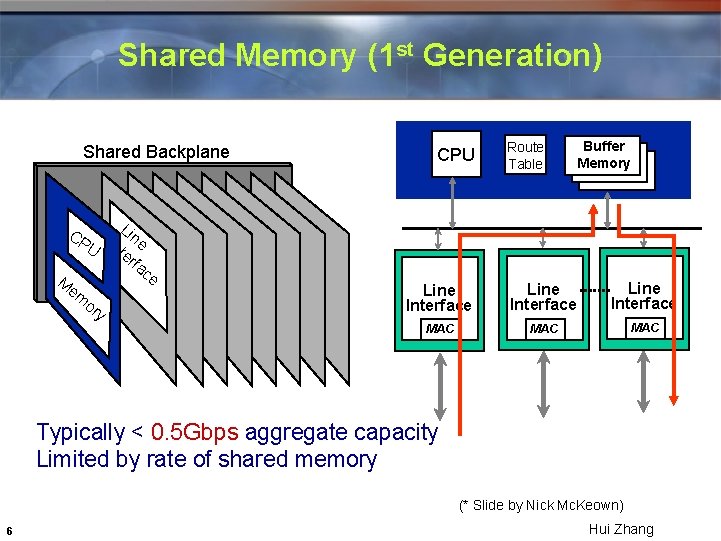

Shared Memory (1 st Generation) Shared Backplane CP M em Li ne I n U te rfa ce or y CPU Route Table Buffer Memory Line Interface MAC MAC Typically < 0. 5 Gbps aggregate capacity Limited by rate of shared memory (* Slide by Nick Mc. Keown) 6 Hui Zhang

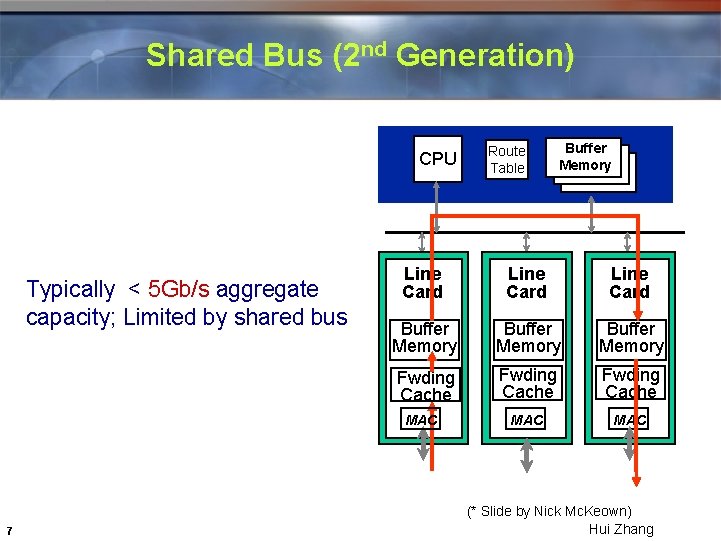

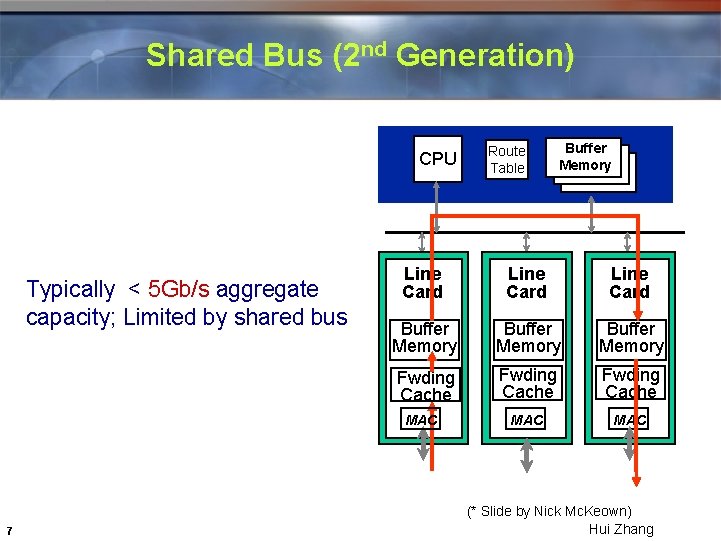

Shared Bus (2 nd Generation) CPU Typically < 5 Gb/s aggregate capacity; Limited by shared bus Buffer Memory Line Card Buffer Memory Fwding Cache MAC MAC 7 Route Table (* Slide by Nick Mc. Keown) Hui Zhang

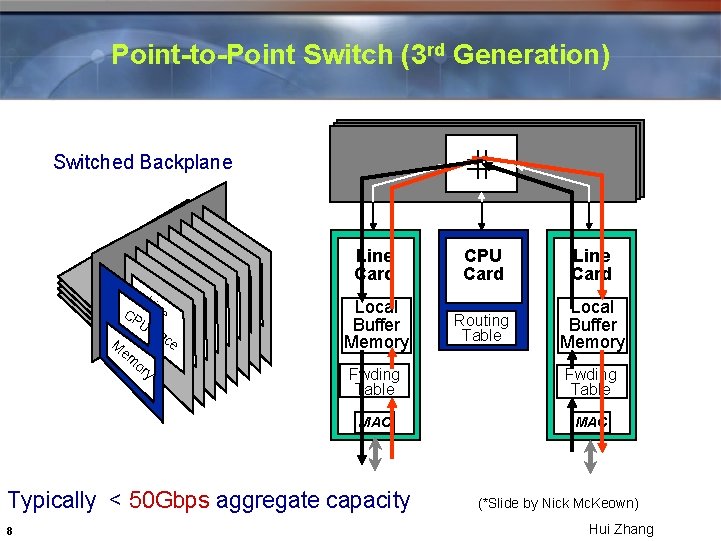

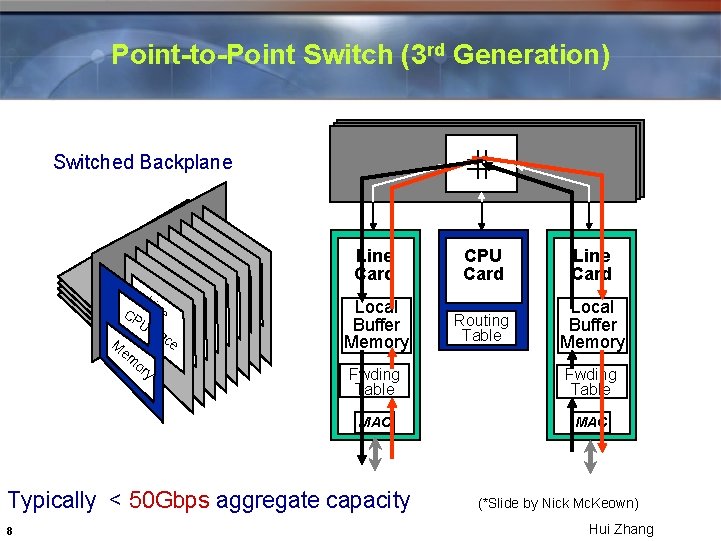

Point-to-Point Switch (3 rd Generation) Switched Backplane Li I CPnt ne Uerf ac e M em or y Line Card CPU Card Line Card Local Buffer Memory Routing Table Local Buffer Memory Fwding Table MAC Typically < 50 Gbps aggregate capacity 8 (*Slide by Nick Mc. Keown) Hui Zhang

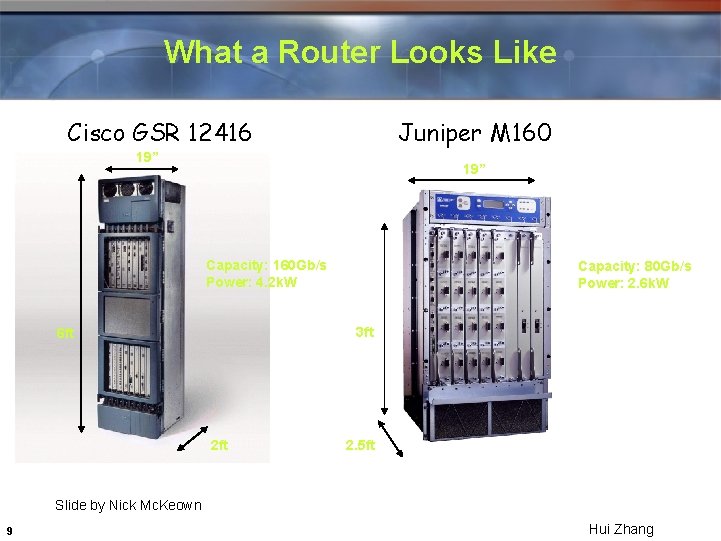

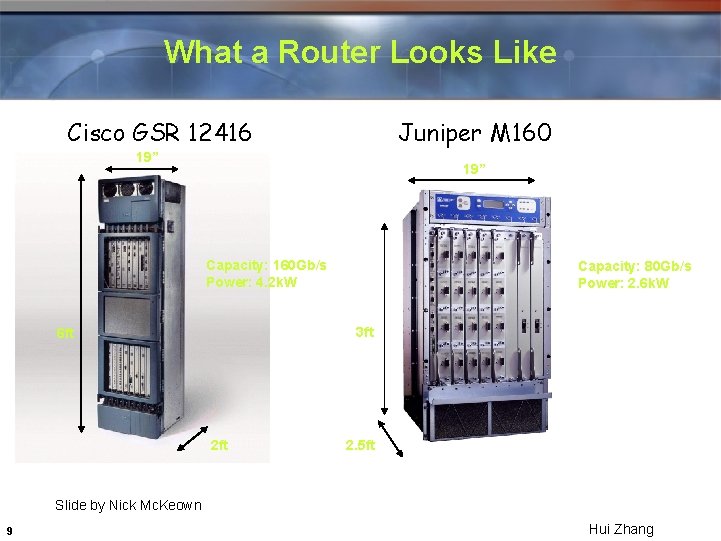

What a Router Looks Like Cisco GSR 12416 Juniper M 160 19” Capacity: 160 Gb/s Power: 4. 2 k. W Capacity: 80 Gb/s Power: 2. 6 k. W 3 ft 6 ft 2. 5 ft Slide by Nick Mc. Keown 9 Hui Zhang

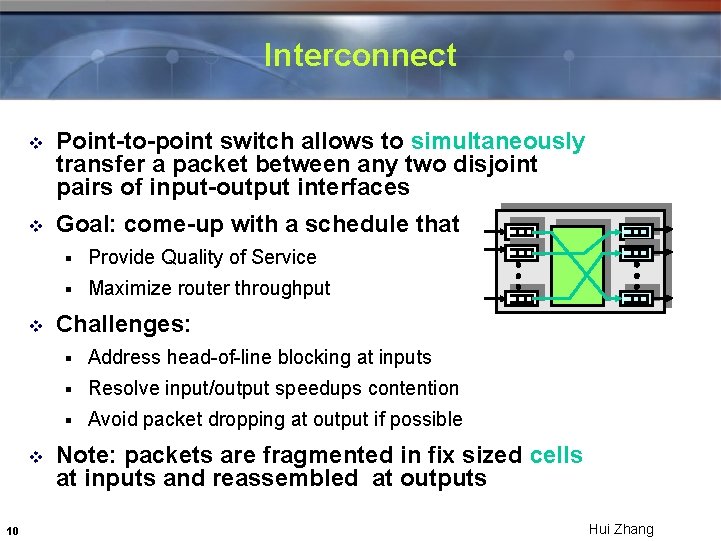

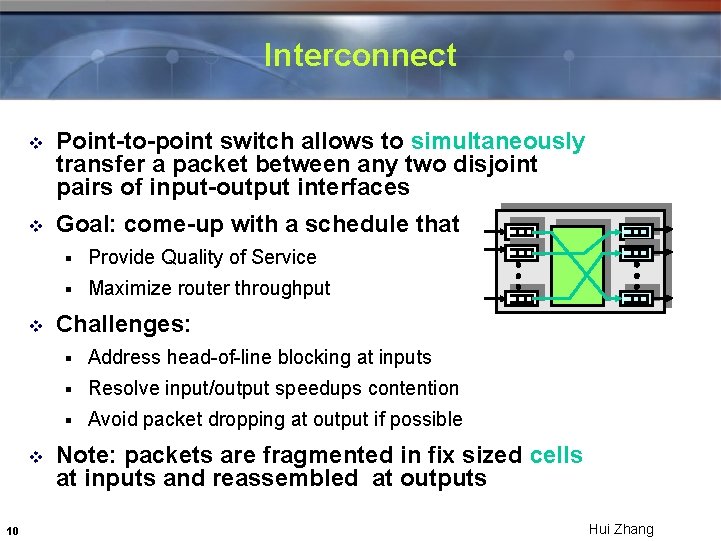

Interconnect v Point-to-point switch allows to simultaneously transfer a packet between any two disjoint pairs of input-output interfaces v Goal: come-up with a schedule that v v 10 § Provide Quality of Service § Maximize router throughput Challenges: § Address head-of-line blocking at inputs § Resolve input/output speedups contention § Avoid packet dropping at output if possible Note: packets are fragmented in fix sized cells at inputs and reassembled at outputs Hui Zhang

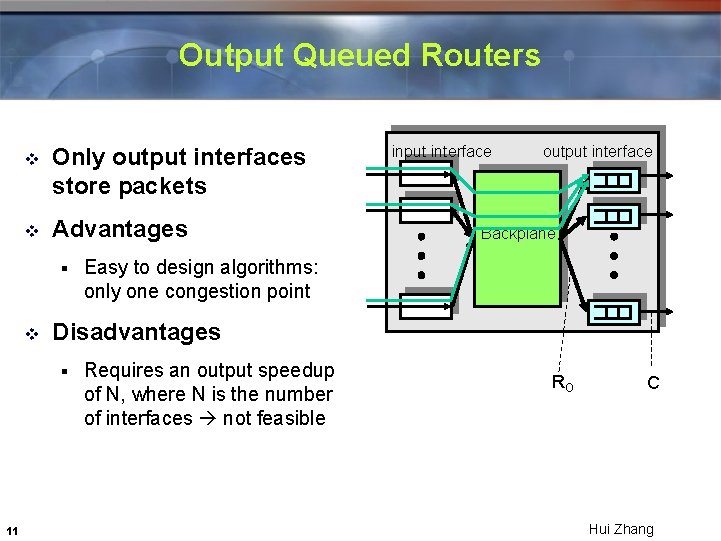

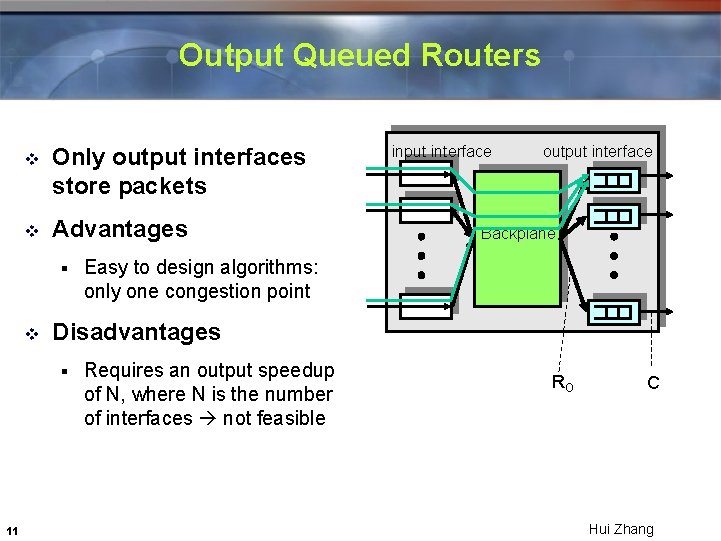

Output Queued Routers v Only output interfaces store packets v Advantages § v output interface Backplane Easy to design algorithms: only one congestion point Disadvantages § 11 input interface Requires an output speedup of N, where N is the number of interfaces not feasible RO C Hui Zhang

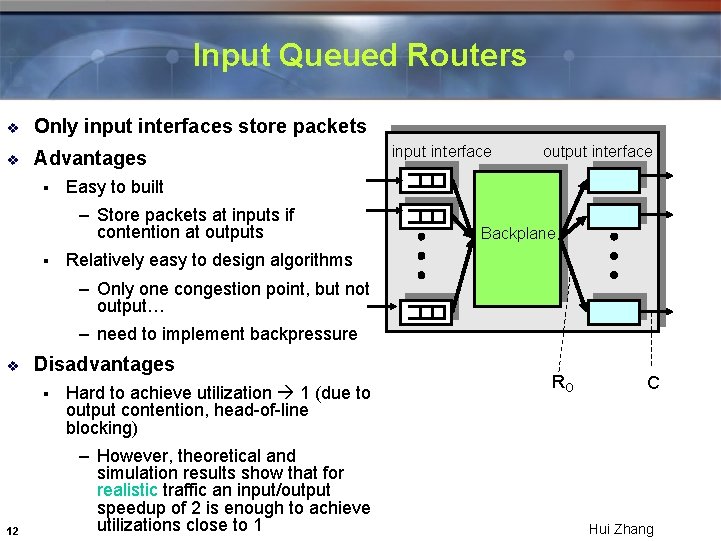

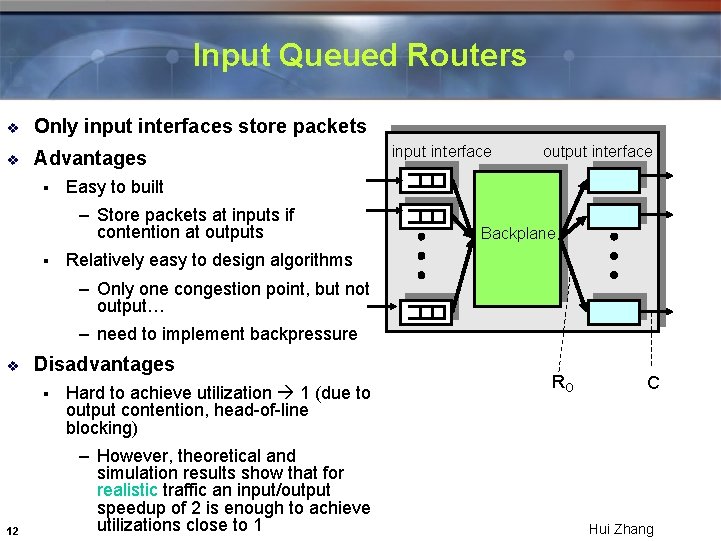

Input Queued Routers v Only input interfaces store packets v Advantages § output interface Easy to built – Store packets at inputs if contention at outputs § input interface Backplane Relatively easy to design algorithms – Only one congestion point, but not output… – need to implement backpressure v Disadvantages § 12 Hard to achieve utilization 1 (due to output contention, head-of-line blocking) – However, theoretical and simulation results show that for realistic traffic an input/output speedup of 2 is enough to achieve utilizations close to 1 RO C Hui Zhang

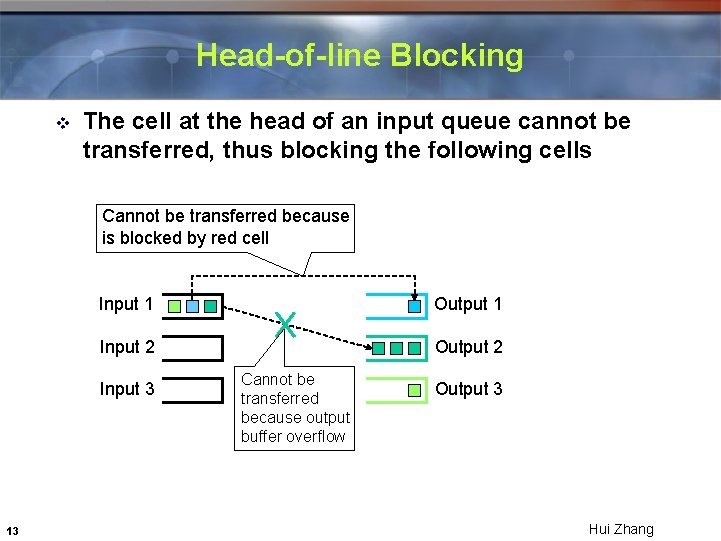

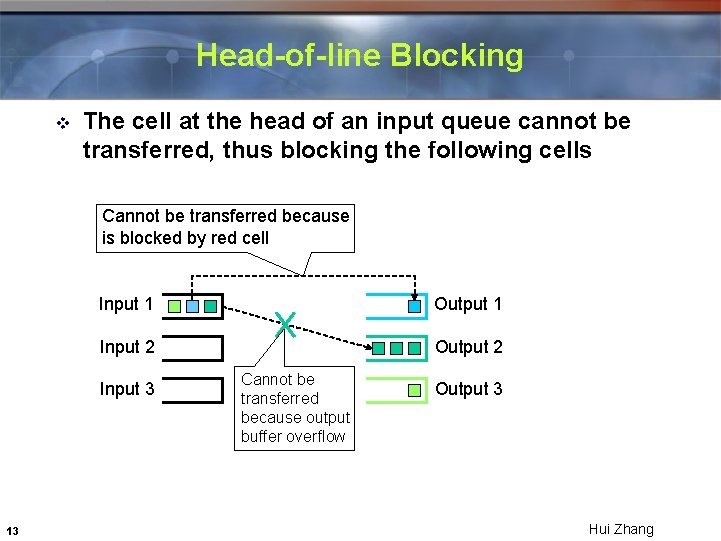

Head-of-line Blocking v The cell at the head of an input queue cannot be transferred, thus blocking the following cells Cannot be transferred because is blocked by red cell Input 1 Output 1 Input 2 Output 2 Input 3 13 Cannot be transferred because output buffer overflow Output 3 Hui Zhang

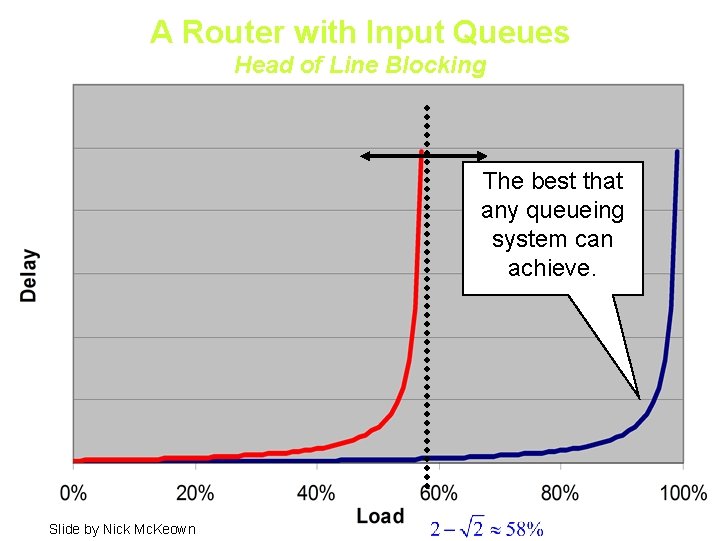

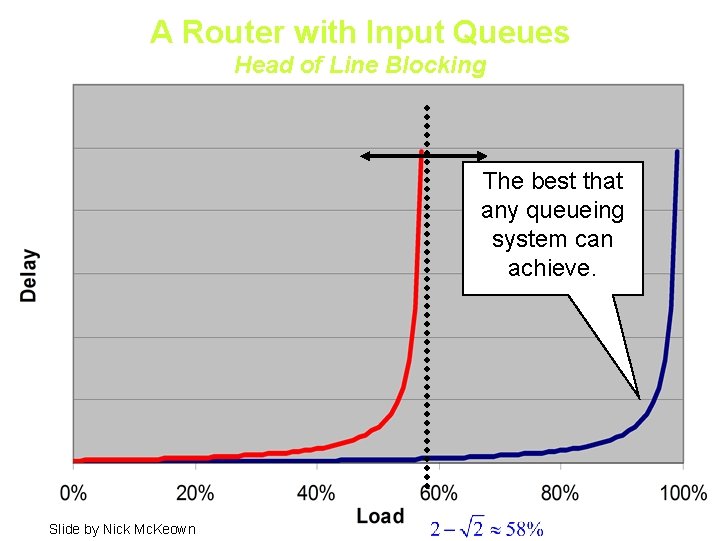

A Router with Input Queues Head of Line Blocking The best that any queueing system can achieve. 14 Slide by Nick Mc. Keown Hui Zhang

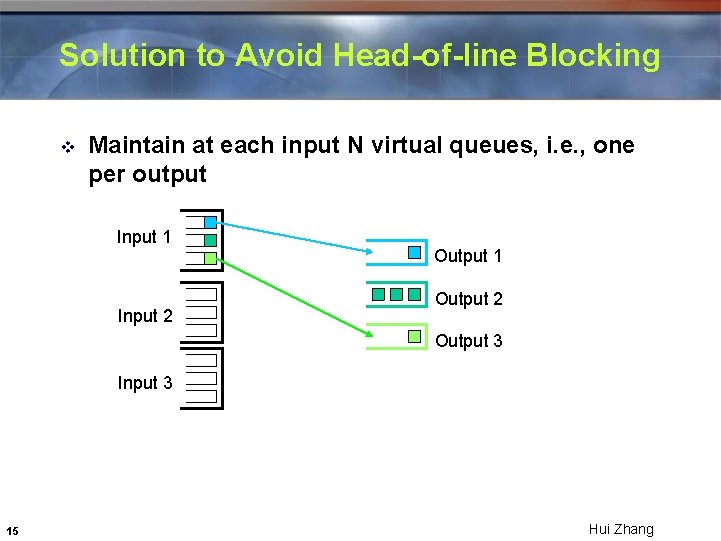

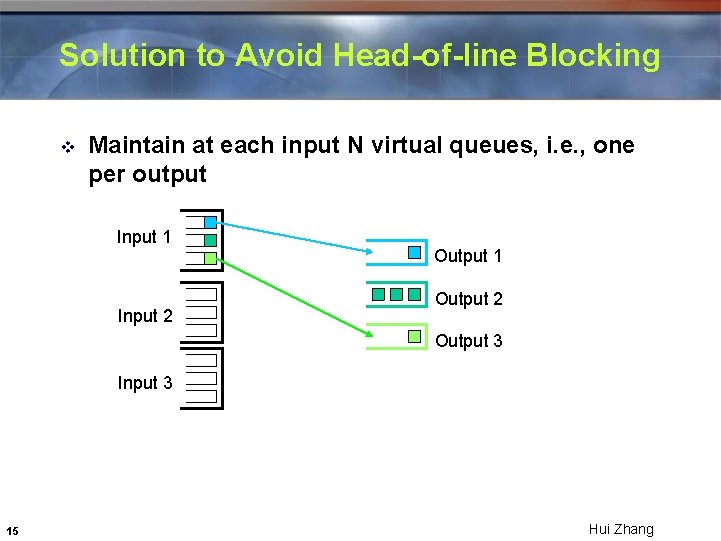

Solution to Avoid Head-of-line Blocking v Maintain at each input N virtual queues, i. e. , one per output Input 1 Input 2 Output 1 Output 2 Output 3 Input 3 15 Hui Zhang

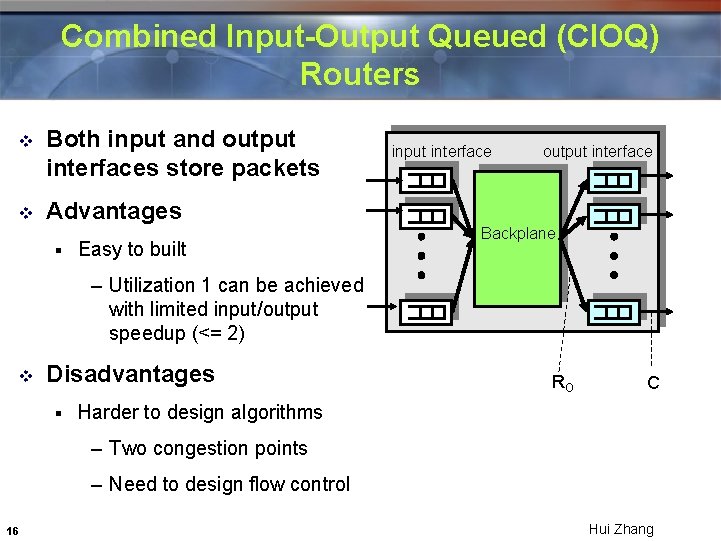

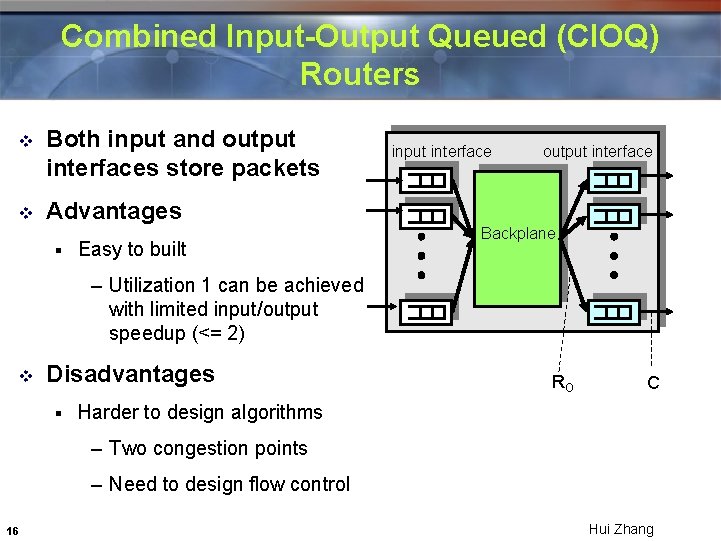

Combined Input-Output Queued (CIOQ) Routers v Both input and output interfaces store packets v Advantages § Easy to built input interface output interface Backplane – Utilization 1 can be achieved with limited input/output speedup (<= 2) v Disadvantages § RO C Harder to design algorithms – Two congestion points – Need to design flow control 16 Hui Zhang

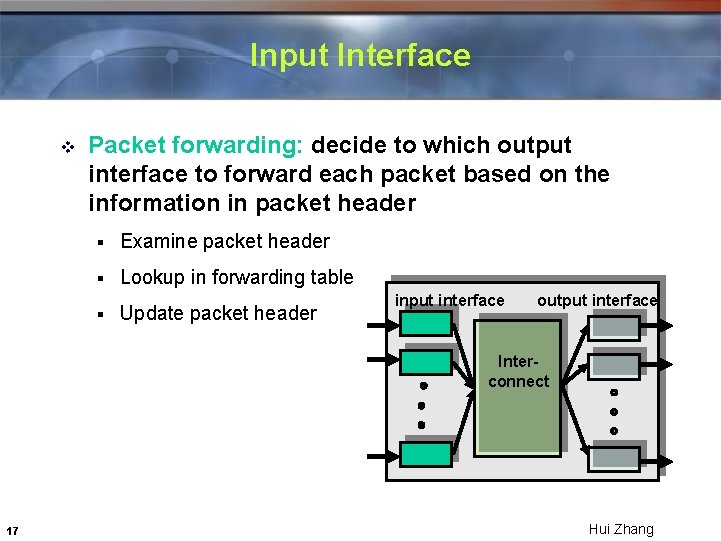

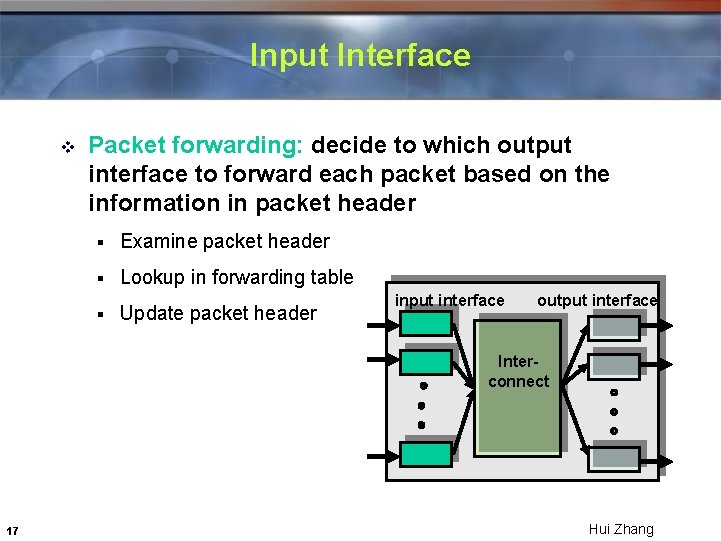

Input Interface v Packet forwarding: decide to which output interface to forward each packet based on the information in packet header § Examine packet header § Lookup in forwarding table § Update packet header input interface output interface Interconnect 17 Hui Zhang

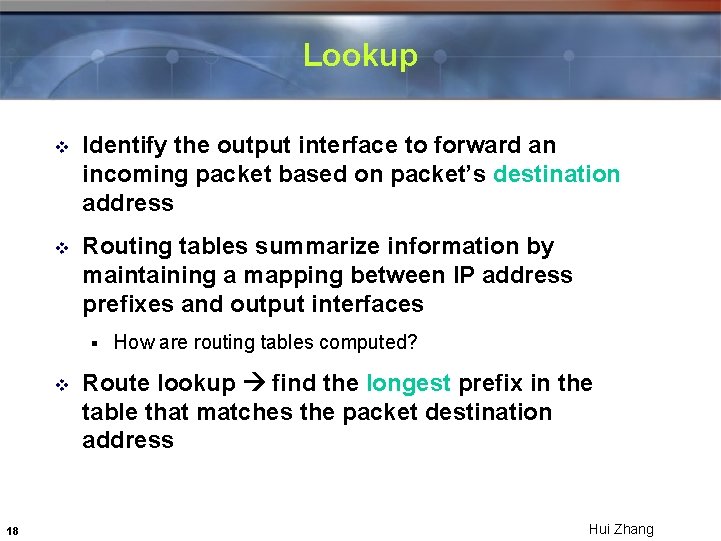

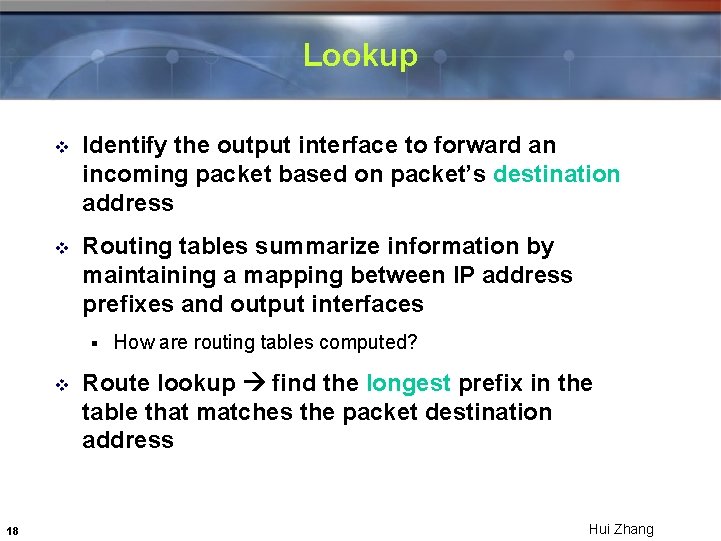

Lookup v Identify the output interface to forward an incoming packet based on packet’s destination address v Routing tables summarize information by maintaining a mapping between IP address prefixes and output interfaces § v 18 How are routing tables computed? Route lookup find the longest prefix in the table that matches the packet destination address Hui Zhang

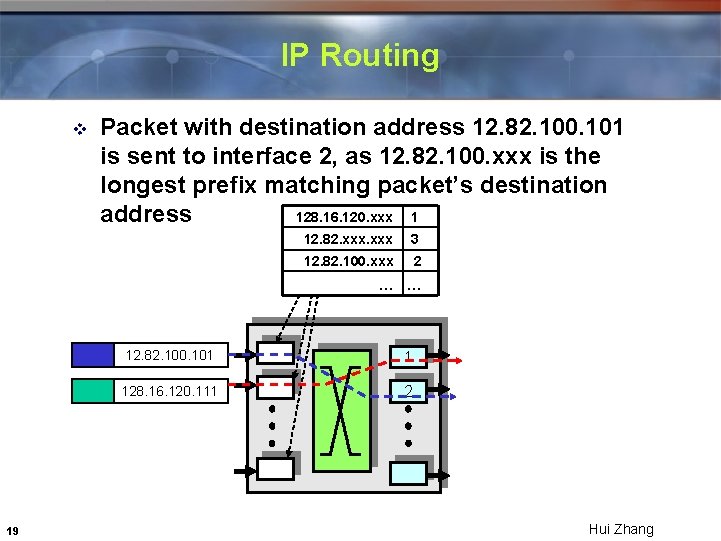

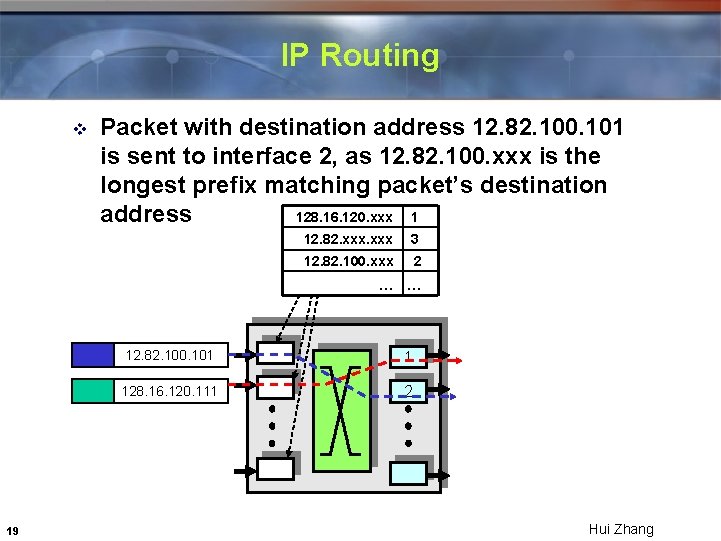

IP Routing v 19 Packet with destination address 12. 82. 100. 101 is sent to interface 2, as 12. 82. 100. xxx is the longest prefix matching packet’s destination address 128. 16. 120. xxx 1 12. 82. xxx 3 12. 82. 100. xxx 2 … … 12. 82. 100. 101 1 128. 16. 120. 111 2 Hui Zhang

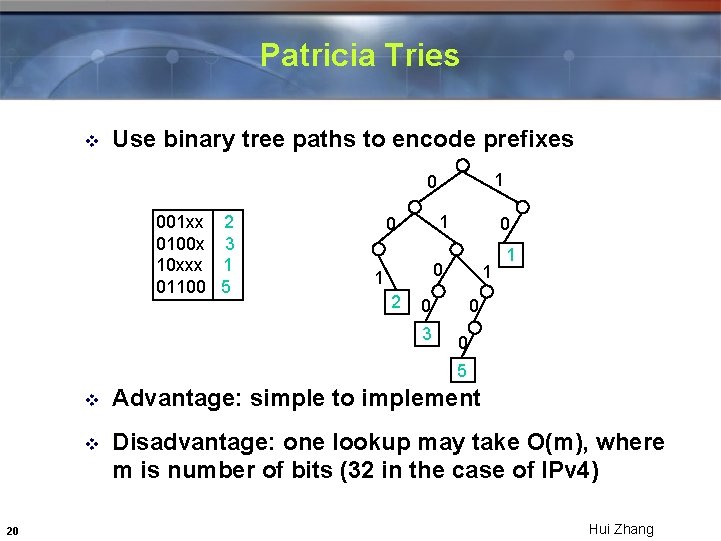

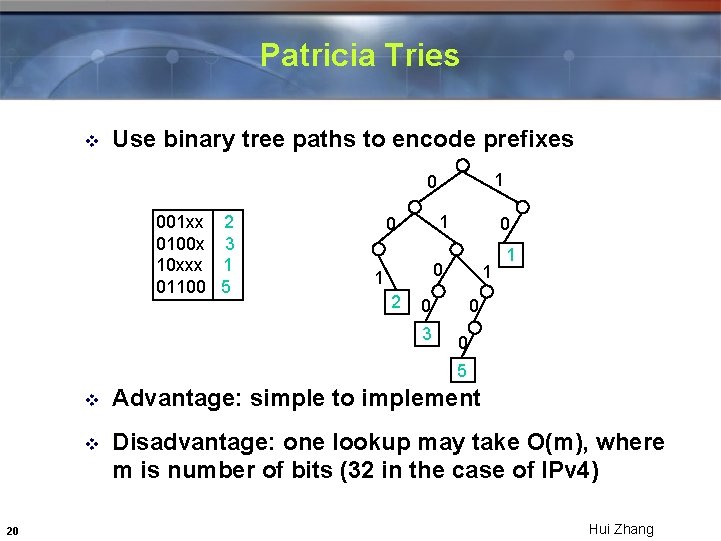

Patricia Tries v Use binary tree paths to encode prefixes 1 0 001 xx 2 0100 x 3 10 xxx 1 01100 5 1 0 0 0 1 2 1 0 3 1 0 0 5 20 v Advantage: simple to implement v Disadvantage: one lookup may take O(m), where m is number of bits (32 in the case of IPv 4) Hui Zhang

Addressing and Look-up v Flat address § v Ethernet: 48 bit MAC address § ATM: 28 bit VPI/VCI § DS-0: timeslot location v Limited scalability v High speed lookup Hierarchical address § IP <network>. <subnet>. <host> § Telephone: country. area. home v Scalable v Easy lookup if boundary is fixed § v Difficult lookup if boundary is flexible § 21 telephony longest prefix match for IP Hui Zhang

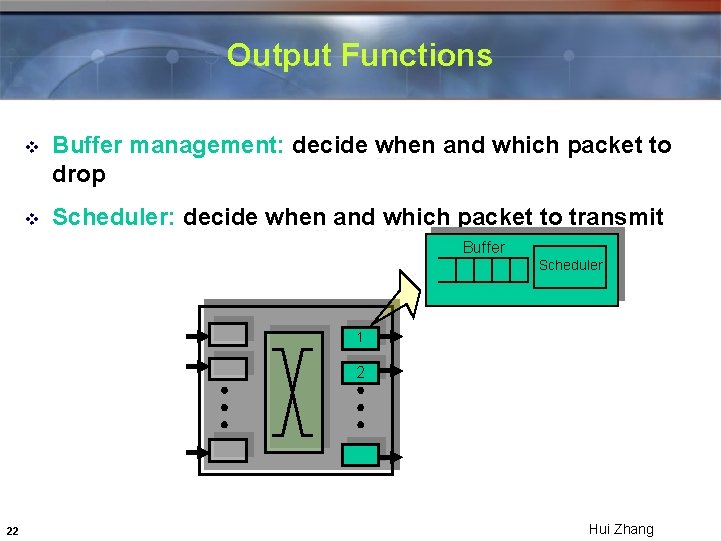

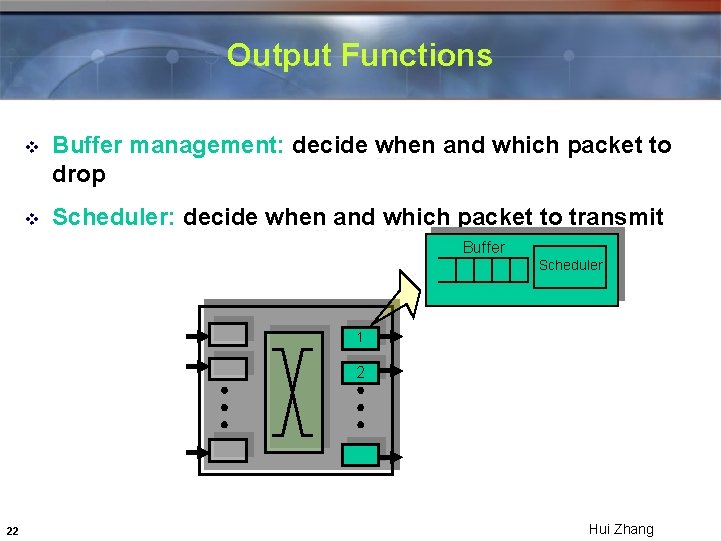

Output Functions v Buffer management: decide when and which packet to drop v Scheduler: decide when and which packet to transmit Buffer Scheduler 1 2 22 Hui Zhang

Example: FIFO router 23 v Most of today’s routers v Drop-tail buffer management: when buffer is full drop the incoming packet v First-In-First-Out (FIFO) Scheduling: schedule packets in the same order they arrive Hui Zhang

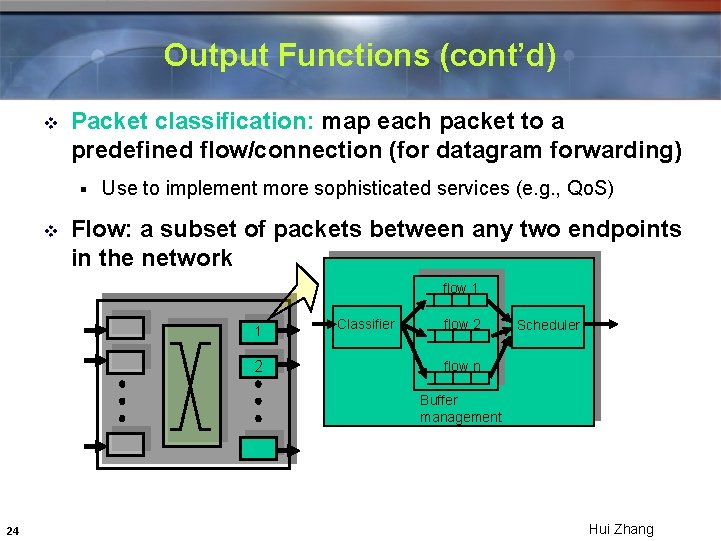

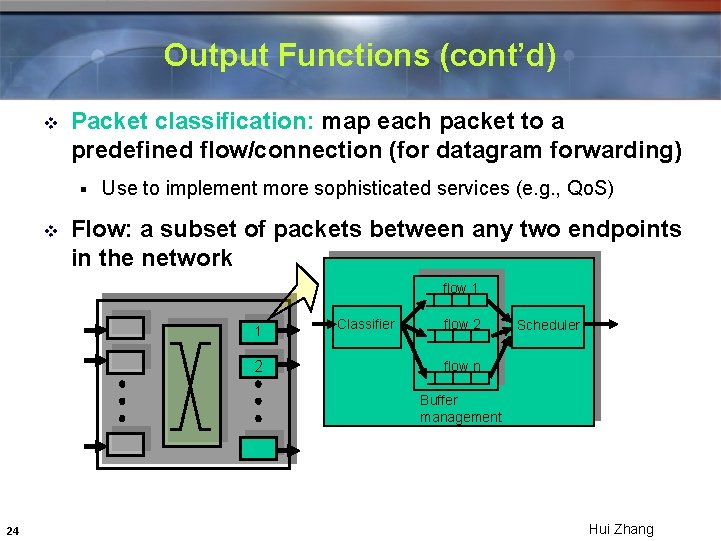

Output Functions (cont’d) v Packet classification: map each packet to a predefined flow/connection (for datagram forwarding) § v Use to implement more sophisticated services (e. g. , Qo. S) Flow: a subset of packets between any two endpoints in the network flow 1 1 2 Classifier flow 2 Scheduler flow n Buffer management 24 Hui Zhang

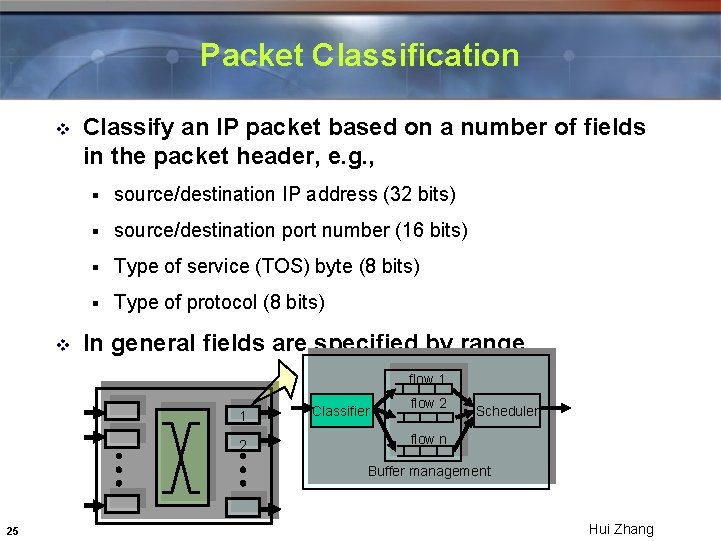

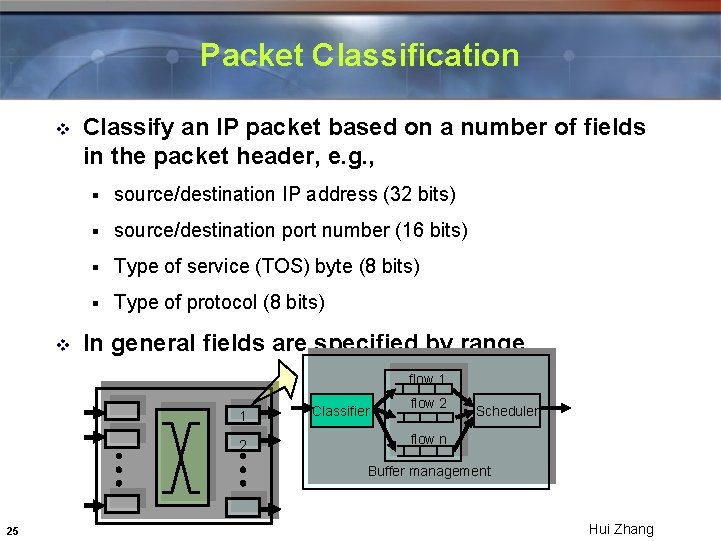

Packet Classification v v Classify an IP packet based on a number of fields in the packet header, e. g. , § source/destination IP address (32 bits) § source/destination port number (16 bits) § Type of service (TOS) byte (8 bits) § Type of protocol (8 bits) In general fields are specified by range flow 1 1 2 Classifier flow 2 Scheduler flow n Buffer management 25 Hui Zhang

Example of Classification Rules v Access-control in firewalls § v Policy-based routing § v Route IP telephony traffic from X to Y via ATM Differentiate quality of service § 26 Deny all e-mail traffic from ISP-X to Y Ensure that no more than 50 Mbps are injected from ISP-X Hui Zhang

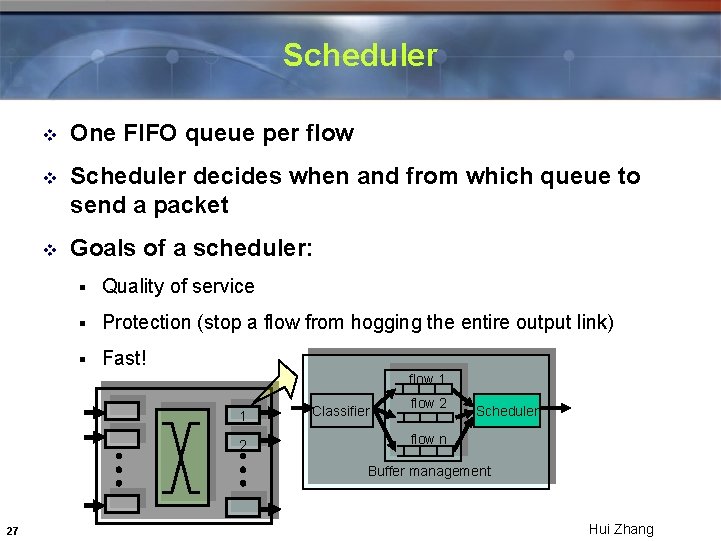

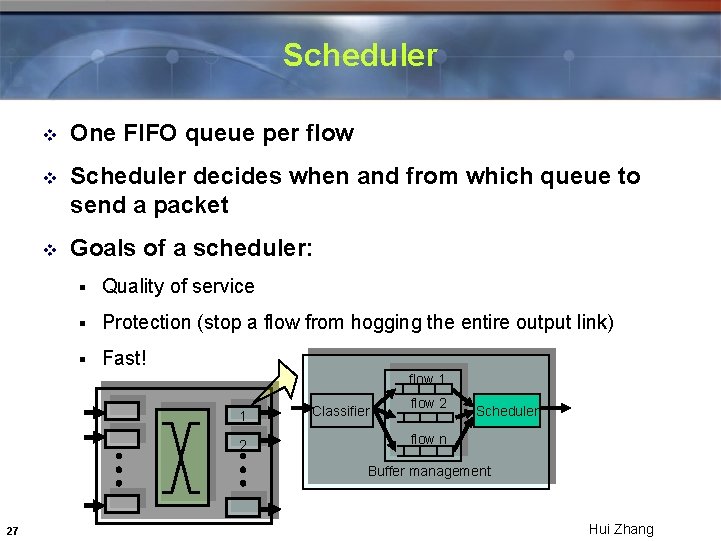

Scheduler v One FIFO queue per flow v Scheduler decides when and from which queue to send a packet v Goals of a scheduler: § Quality of service § Protection (stop a flow from hogging the entire output link) § Fast! flow 1 1 2 Classifier flow 2 Scheduler flow n Buffer management 27 Hui Zhang

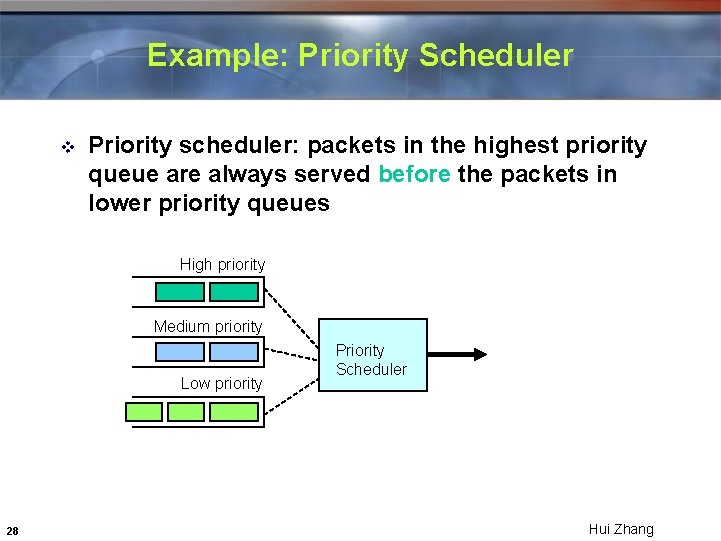

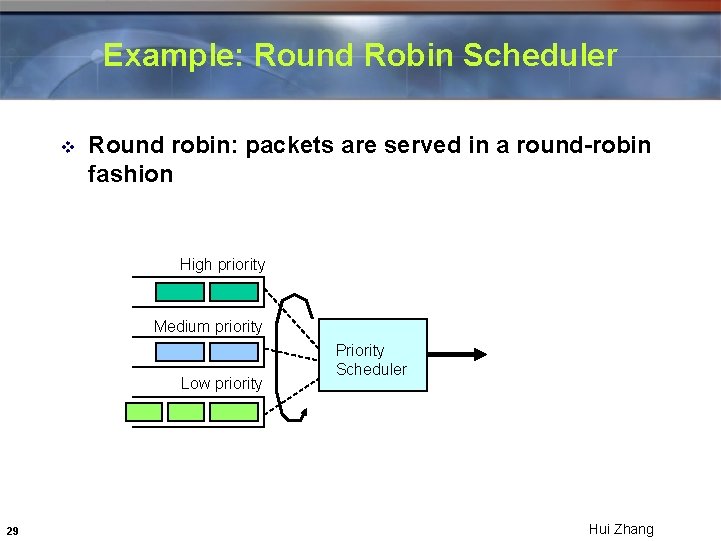

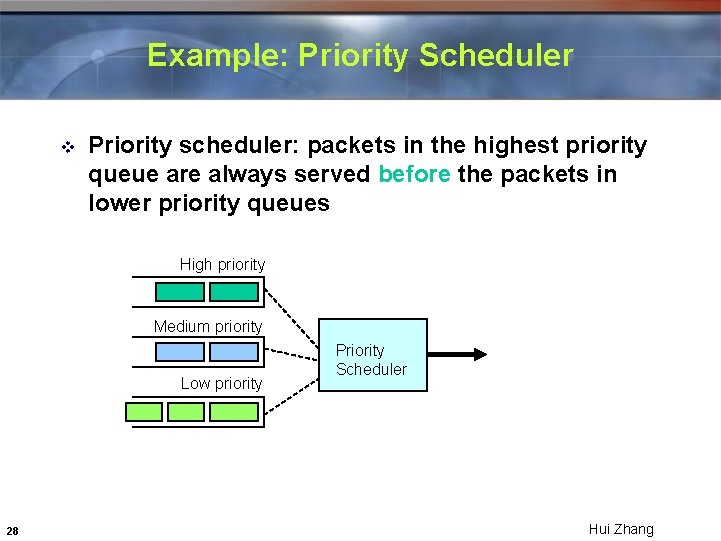

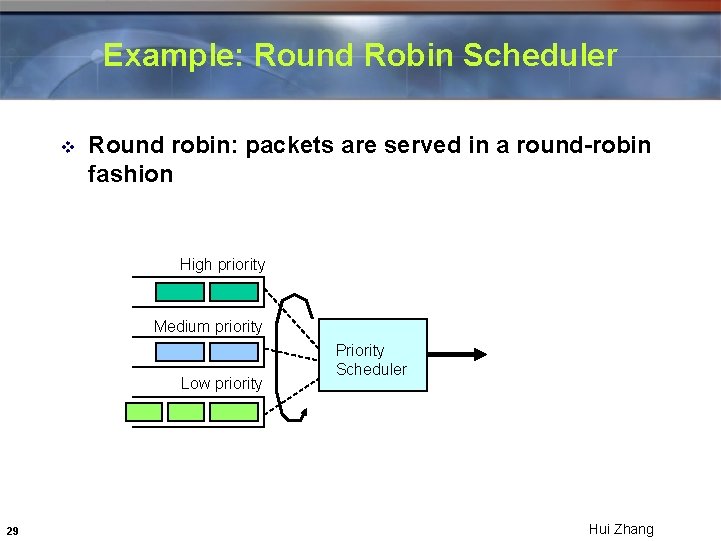

Example: Priority Scheduler v Priority scheduler: packets in the highest priority queue are always served before the packets in lower priority queues High priority Medium priority Low priority 28 Priority Scheduler Hui Zhang

Example: Round Robin Scheduler v Round robin: packets are served in a round-robin fashion High priority Medium priority Low priority 29 Priority Scheduler Hui Zhang

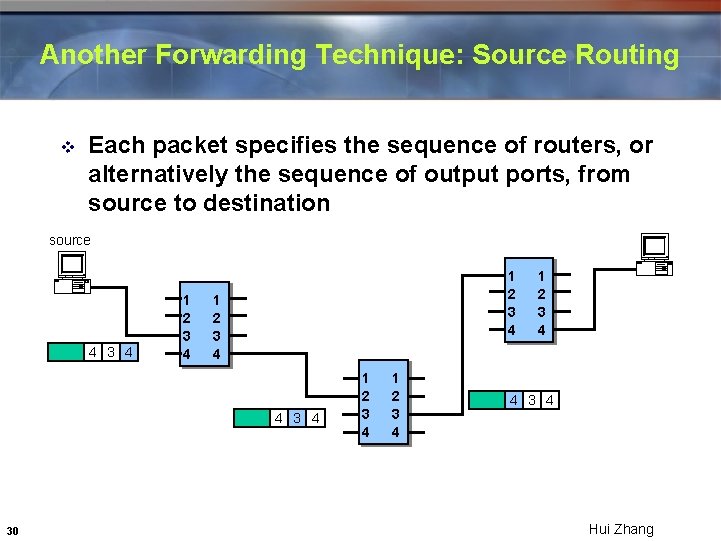

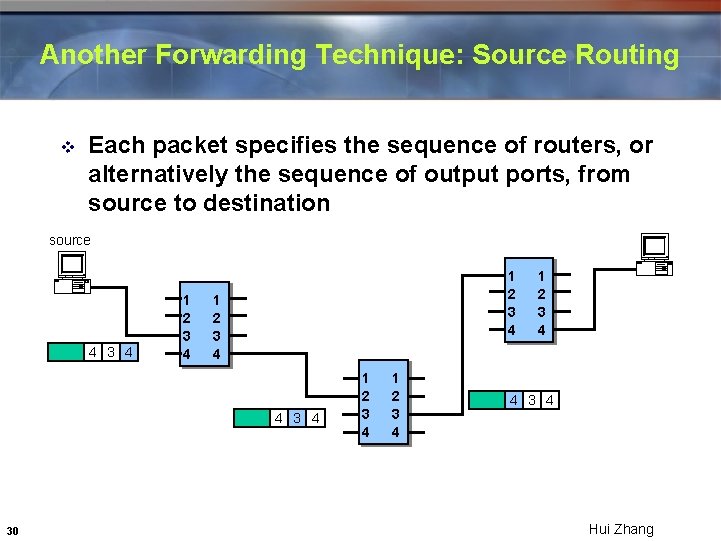

Another Forwarding Technique: Source Routing v Each packet specifies the sequence of routers, or alternatively the sequence of output ports, from source to destination source 4 3 4 1 2 3 4 4 30 1 2 3 4 4 3 4 Hui Zhang

Source Routing (cont’d) 31 v Gives the source control of the path v Not scalable § Packet overhead proportional to the number of routers § Typically, require variable header length which is harder to implement v Hard for source to have complete information v Loose source routing sender specifies only a subset of routers along the path Hui Zhang

Concepts v Control plane vs. data plane v Various switching architectures v Buffering § 32 Input vs. Output vs. Combined Input/Output v Head of line blocking v Scheduling v Header lookup Hui Zhang