12 th workshop of FCPPL 24 27 April

- Slides: 7

12 th workshop of FCPPL 24 -27 April 2019 @ Shanghai -China ASIC development for pixel sensor readout I. Laktineh On behalf of M. Dahoumane 1, L. Zhang 2 1 IPNL, 2 Institute 11/10/2010 Université de Lyon, F-69003 Lyon, France; Université Lyon 1 and CNRS/IN 2 P 3, UMR 5822 F- 69622 Villeurbanne, France of Frontier and Interdisciplinary Science and Key Laboratory of Particle Physics and Particle Irradiation, Shandong University, Qingdao, 266237, Shandong, China

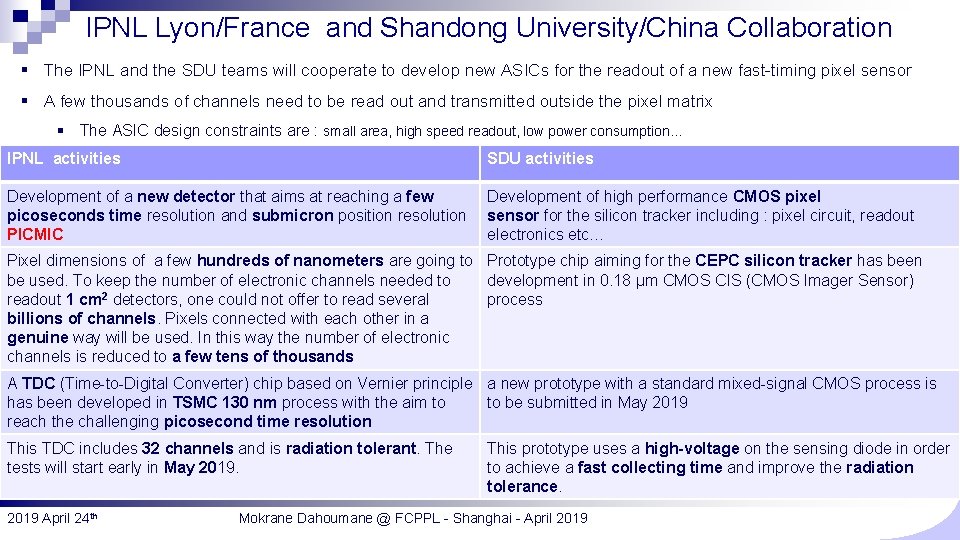

IPNL Lyon/France and Shandong University/China Collaboration § The IPNL and the SDU teams will cooperate to develop new ASICs for the readout of a new fast-timing pixel sensor § A few thousands of channels need to be read out and transmitted outside the pixel matrix § The ASIC design constraints are : small area, high speed readout, low power consumption… IPNL activities SDU activities Development of a new detector that aims at reaching a few picoseconds time resolution and submicron position resolution PICMIC Development of high performance CMOS pixel sensor for the silicon tracker including : pixel circuit, readout electronics etc… Pixel dimensions of a few hundreds of nanometers are going to Prototype chip aiming for the CEPC silicon tracker has been be used. To keep the number of electronic channels needed to development in 0. 18 μm CMOS CIS (CMOS Imager Sensor) readout 1 cm 2 detectors, one could not offer to read several process billions of channels. Pixels connected with each other in a genuine way will be used. In this way the number of electronic channels is reduced to a few tens of thousands A TDC (Time-to-Digital Converter) chip based on Vernier principle a new prototype with a standard mixed-signal CMOS process is has been developed in TSMC 130 nm process with the aim to to be submitted in May 2019 reach the challenging picosecond time resolution This TDC includes 32 channels and is radiation tolerant. The tests will start early in May 2019 April 24 th This prototype uses a high-voltage on the sensing diode in order to achieve a fast collecting time and improve the radiation tolerance. Mokrane Dahoumane @ FCPPL - Shanghai - April 2019

IPNL Lyon/France and Shandong University/China Collaboration § To read out this big number of channels in a small area the expertise developed by the SDU group to readout Silicon tracker will be extremely useful. § The expertise on time measurement developed by the IPNL group will be shared with the SDU group § This work will be a part of a large collaboration including the French groups from Strasbourg and Marseille : § Liang Zhang as a visiting scholar in IPNL Lyon will engage in this project. § The IPNL group will be eager to host students from SDU and encourages them to follow a co-joint Ph. D between the two groups. § The DSU group members will also host their colleagues from Lyon to get more insight on the pixel sensor characterization § Laboratory test setup and beam test setup § Data acquisition electronics setup… 2019 April 24 th Mokrane Dahoumane @ FCPPL - Shanghai - April 2019

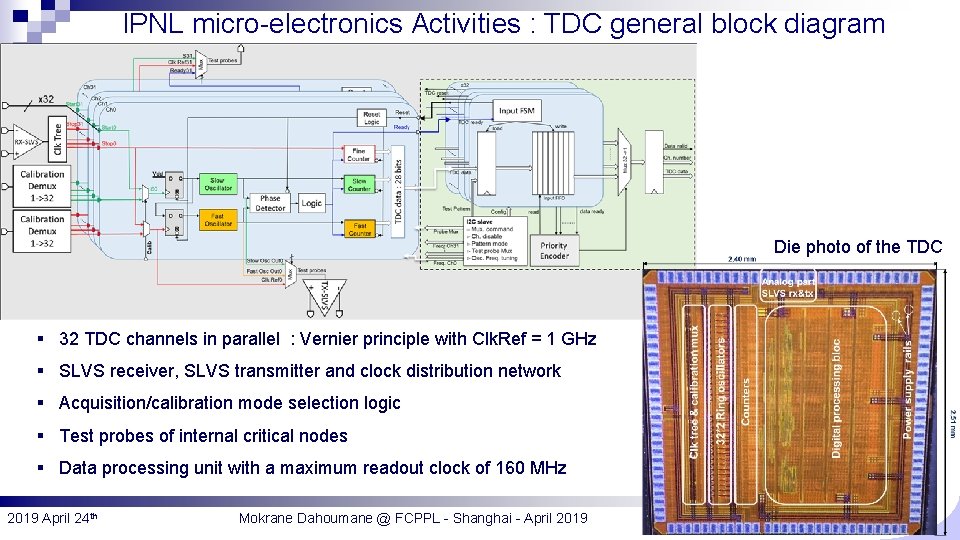

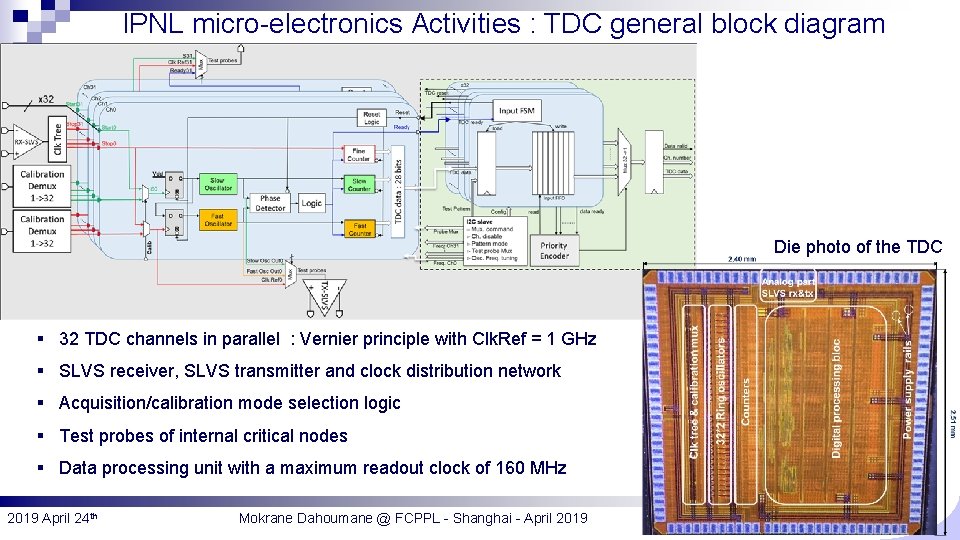

IPNL micro-electronics Activities : TDC general block diagram Die photo of the TDC § 32 TDC channels in parallel : Vernier principle with Clk. Ref = 1 GHz § SLVS receiver, SLVS transmitter and clock distribution network § Acquisition/calibration mode selection logic § Test probes of internal critical nodes § Data processing unit with a maximum readout clock of 160 MHz 2019 April 24 th Mokrane Dahoumane @ FCPPL - Shanghai - April 2019

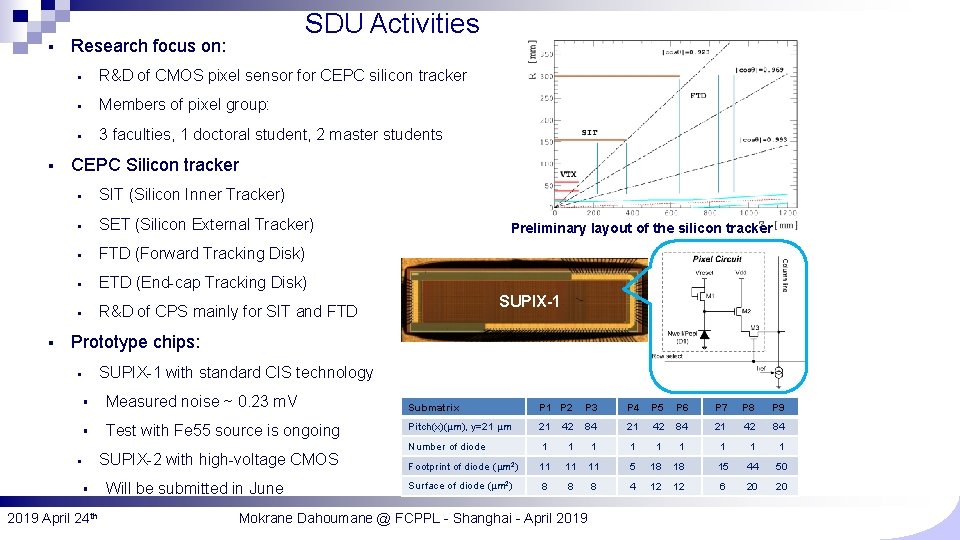

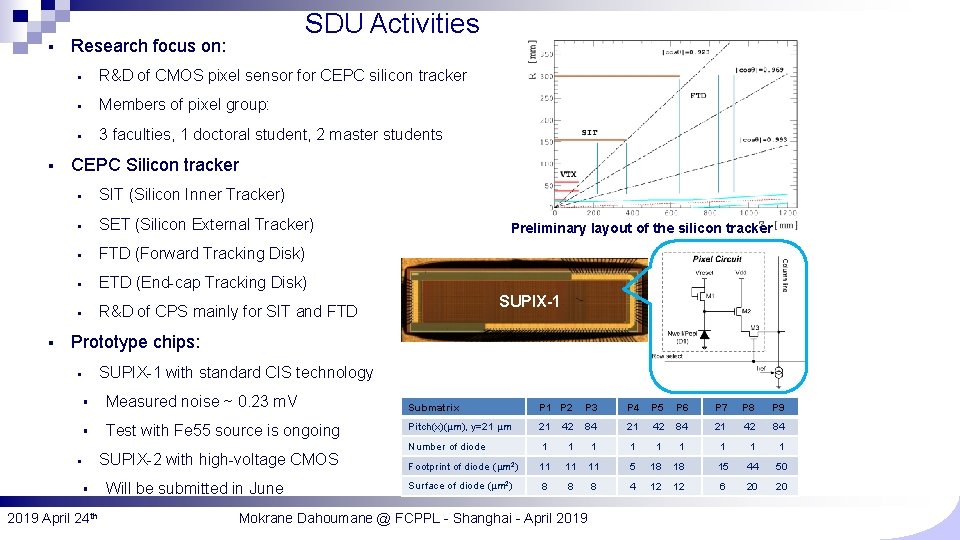

§ § § SDU Activities Research focus on: § R&D of CMOS pixel sensor for CEPC silicon tracker § Members of pixel group: § 3 faculties, 1 doctoral student, 2 master students CEPC Silicon tracker § SIT (Silicon Inner Tracker) § SET (Silicon External Tracker) § FTD (Forward Tracking Disk) § ETD (End-cap Tracking Disk) § R&D of CPS mainly for SIT and FTD Preliminary layout of the silicon tracker SUPIX-1 Prototype chips: SUPIX-1 with standard CIS technology § § Measured noise ~ 0. 23 m. V § Test with Fe 55 source is ongoing SUPIX-2 with high-voltage CMOS § § 2019 April 24 th Will be submitted in June Submatrix P 1 P 2 P 3 P 4 P 5 P 6 P 7 P 8 P 9 Pitch(x)(µm), y=21 µm 21 42 84 Number of diode 1 1 1 1 1 Footprint of diode (µm 2) 11 11 11 5 18 18 15 44 50 Surface of diode (µm 2) 8 8 8 4 12 12 6 20 20 Mokrane Dahoumane @ FCPPL - Shanghai - April 2019

2019 April 24 th Mokrane Dahoumane @ FCPPL - Shanghai - April 2019

Thank you 2019 April 24 th Mokrane Dahoumane @ FCPPL - Shanghai - April 2019