12 bits 10 MSs Pipelined ADC HoYong Jung

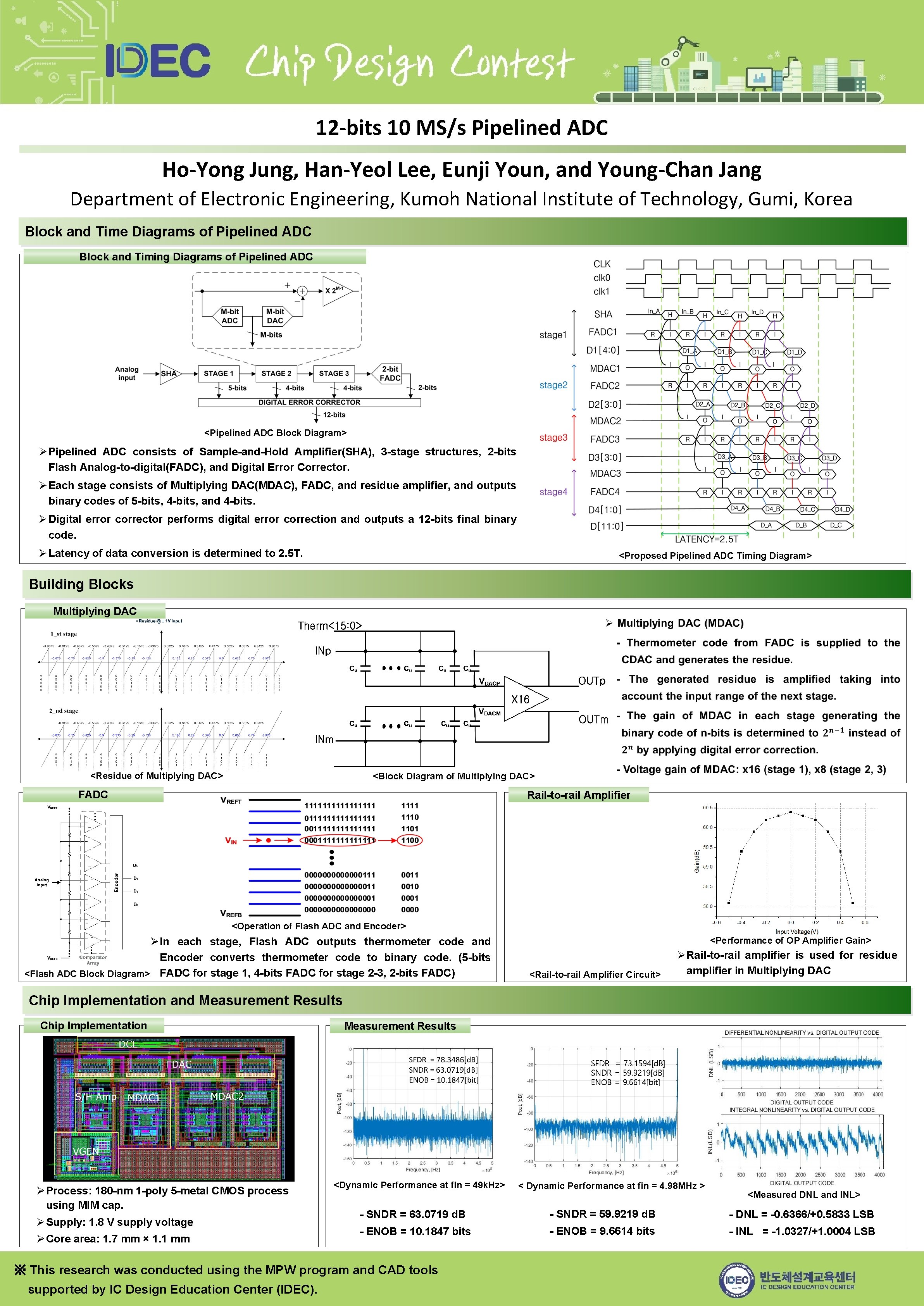

12 -bits 10 MS/s Pipelined ADC Ho-Yong Jung, Han-Yeol Lee, Eunji Youn, and Young-Chan Jang Department of Electronic Engineering, Kumoh National Institute of Technology, Gumi, Korea Block and Time Diagrams of Pipelined ADC Block and Timing Diagrams of Pipelined ADC <Pipelined ADC Block Diagram> Ø Pipelined ADC consists of Sample-and-Hold Amplifier(SHA), 3 -stage structures, 2 -bits Flash Analog-to-digital(FADC), and Digital Error Corrector. Ø Each stage consists of Multiplying DAC(MDAC), FADC, and residue amplifier, and outputs binary codes of 5 -bits, 4 -bits, and 4 -bits. Ø Digital error corrector performs digital error correction and outputs a 12 -bits final binary code. Ø Latency of data conversion is determined to 2. 5 T. <Proposed Pipelined ADC Timing Diagram> Building Blocks Multiplying DAC <Residue of Multiplying DAC> <Block Diagram of Multiplying DAC> FADC Rail-to-rail Amplifier <Operation of Flash ADC and Encoder> Ø In each stage, Flash ADC outputs thermometer code and Encoder converts thermometer code to binary code. (5 -bits <Flash ADC Block Diagram> FADC for stage 1, 4 -bits FADC for stage 2 -3, 2 -bits FADC) <Performance of OP Amplifier Gain> <Rail-to-rail Amplifier Circuit> Ø Rail-to-rail amplifier is used for residue amplifier in Multiplying DAC Chip Implementation and Measurement Results Chip Implementation Ø Process: 180 -nm 1 -poly 5 -metal CMOS process using MIM cap. Ø Supply: 1. 8 V supply voltage Ø Core area: 1. 7 mm × 1. 1 mm Measurement Results <Dynamic Performance at fin = 49 k. Hz> <Measured DNL and INL> - SNDR = 63. 0719 d. B - SNDR = 59. 9219 d. B - DNL = -0. 6366/+0. 5833 LSB - ENOB = 10. 1847 bits - ENOB = 9. 6614 bits - INL = -1. 0327/+1. 0004 LSB ※ This research was conducted using the MPW program and CAD tools supported by IC Design Education Center (IDEC). < Dynamic Performance at fin = 4. 98 MHz >

- Slides: 1