10 PIO Slide 1 of 28 1 PIPOParallel

- Slides: 28

10장 주변장치 (PIO) Slide 1 (of 28)

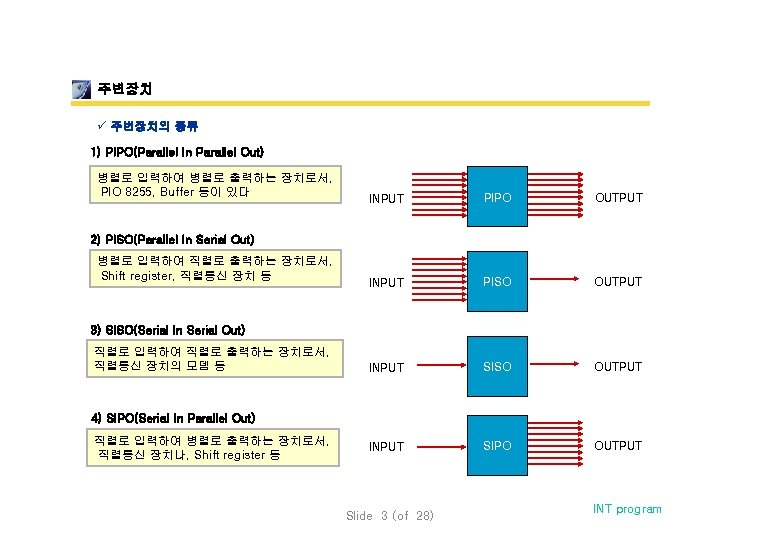

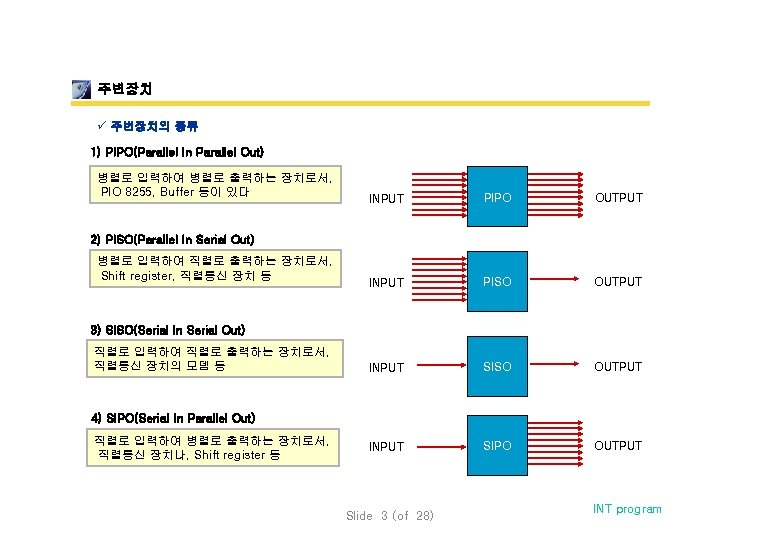

주변장치 ü 주변장치의 종류 1) PIPO(Parallel In Parallel Out) 병렬로 입력하여 병렬로 출력하는 장치로서, PIO 8255, Buffer 등이 있다 INPUT PIPO OUTPUT INPUT PISO OUTPUT INPUT SIPO OUTPUT 2) PISO(Parallel In Serial Out) 병렬로 입력하여 직렬로 출력하는 장치로서, Shift register, 직렬통신 장치 등 3) SISO(Serial In Serial Out) 직렬로 입력하여 직렬로 출력하는 장치로서, 직렬통신 장치의 모뎀 등 4) SIPO(Serial In Parallel Out) 직렬로 입력하여 병렬로 출력하는 장치로서, 직렬통신 장치나, Shift register 등 Slide 3 (of 28) INT program

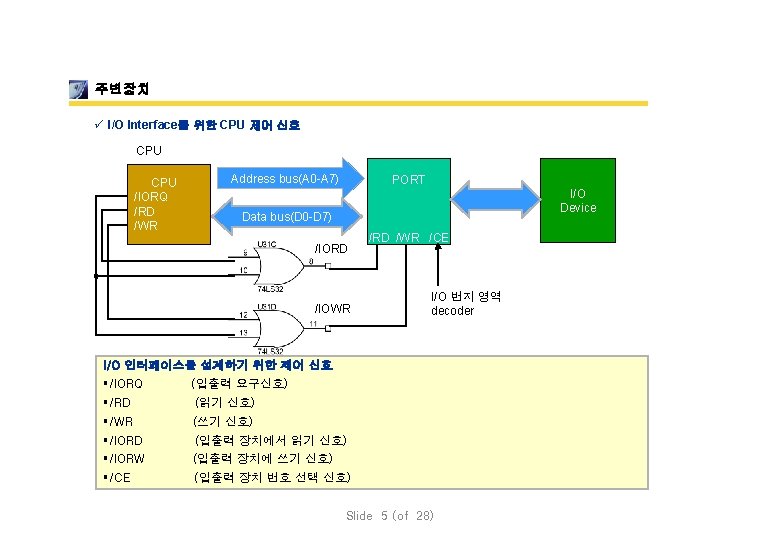

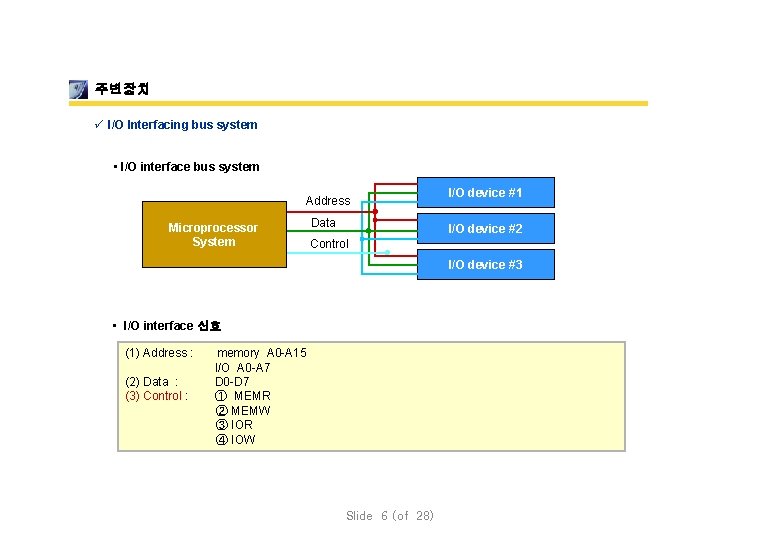

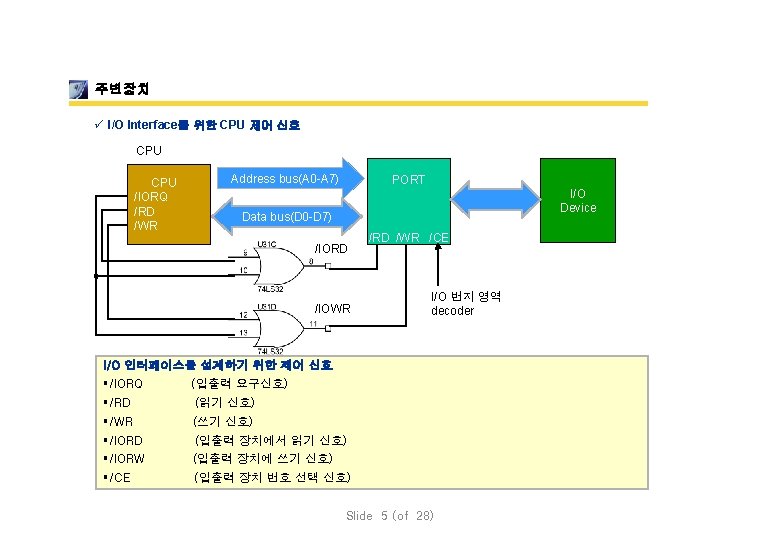

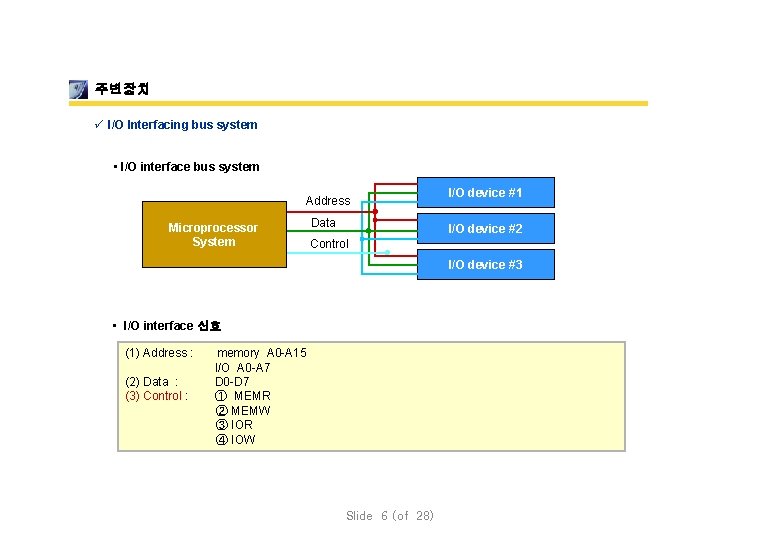

주변장치 ü I/O Interfacing bus system • I/O interface bus system Address Microprocessor System Data I/O device #1 I/O device #2 Control I/O device #3 • I/O interface 신호 (1) Address : memory A 0 -A 15 I/O A 0 -A 7 (2) Data : D 0 -D 7 (3) Control : ① MEMR ② MEMW ③ IOR ④ IOW Slide 6 (of 28)

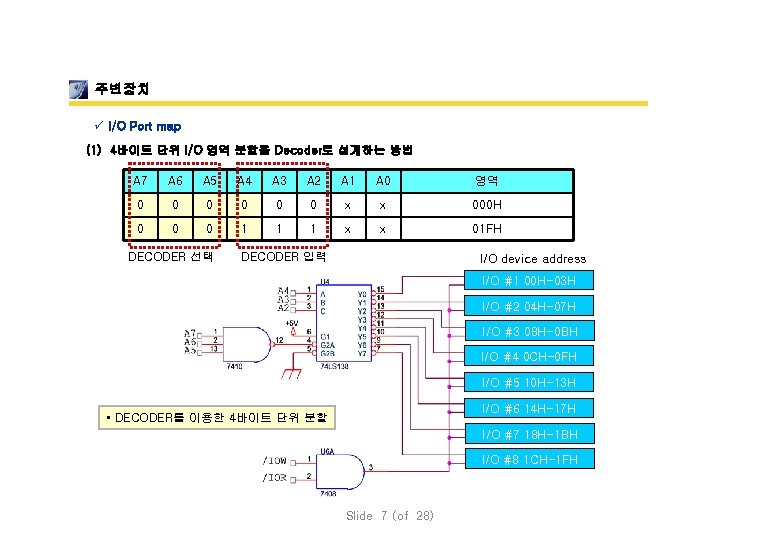

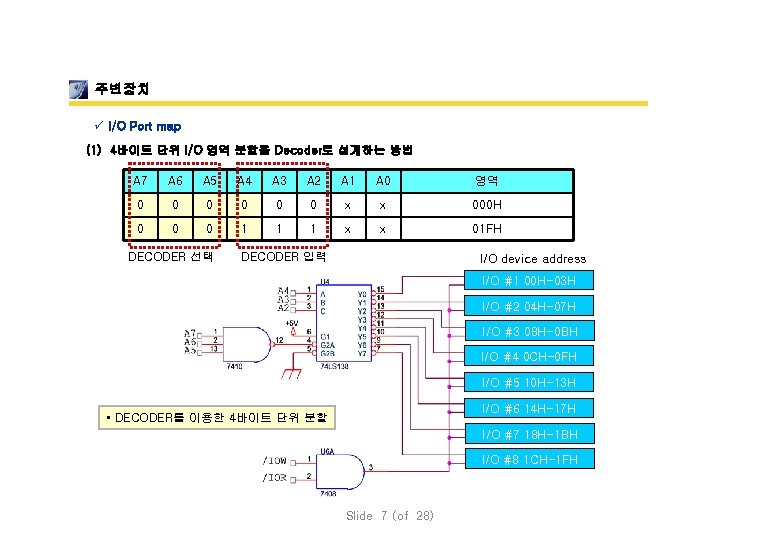

주변장치 ü I/O Port map (1) 4바이트 단위 I/O 영역 분할을 Decoder로 설계하는 방법 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 영역 0 0 0 x x 000 H 0 0 0 1 1 1 x x 01 FH DECODER 선택 DECODER 입력 I/O device address I/O #1 00 H-03 H I/O #2 04 H-07 H I/O #3 08 H-0 BH I/O #4 0 CH-0 FH I/O #5 10 H-13 H I/O #6 14 H-17 H • DECODER를 이용한 4바이트 단위 분할 I/O #7 18 H-1 BH I/O #8 1 CH-1 FH Slide 7 (of 28)

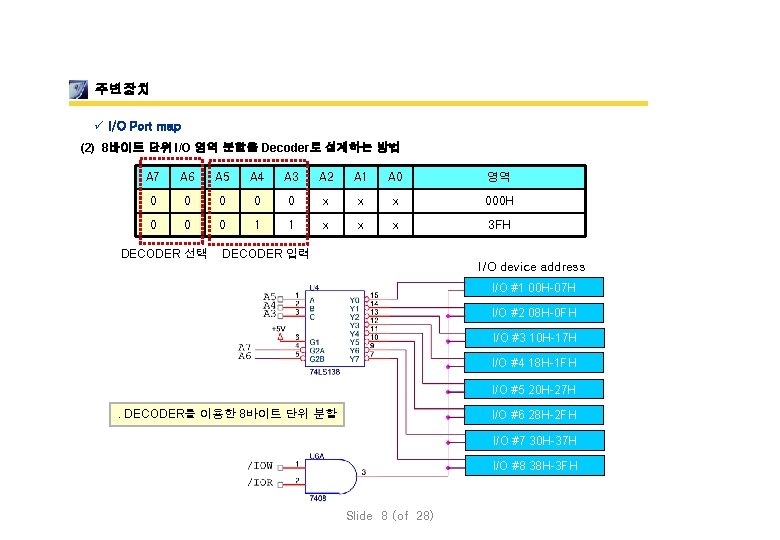

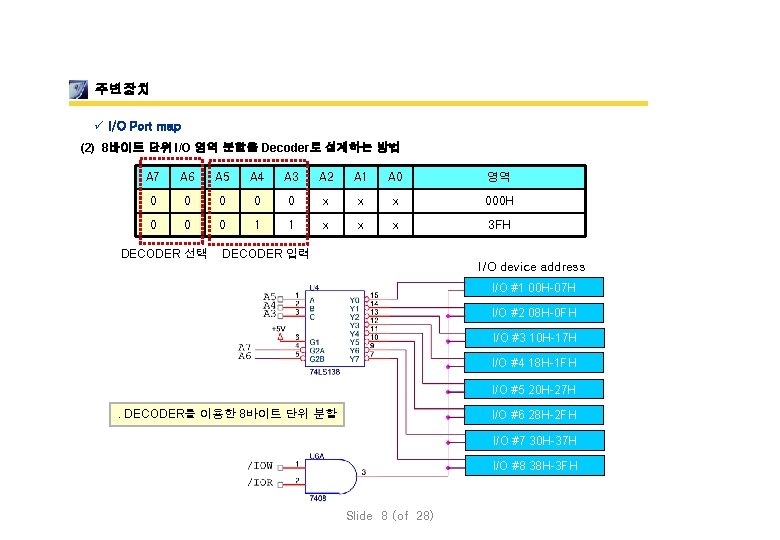

주변장치 ü I/O Port map (2) 8바이트 단위 I/O 영역 분할을 Decoder로 설계하는 방법 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 영역 0 0 0 x x x 000 H 0 0 0 1 1 x x x 3 FH DECODER 선택 DECODER 입력 I/O device address I/O #1 00 H-07 H I/O #2 08 H-0 FH I/O #3 10 H-17 H I/O #4 18 H-1 FH I/O #5 20 H-27 H . DECODER를 이용한 8바이트 단위 분할 I/O #6 28 H-2 FH I/O #7 30 H-37 H I/O #8 38 H-3 FH Slide 8 (of 28)

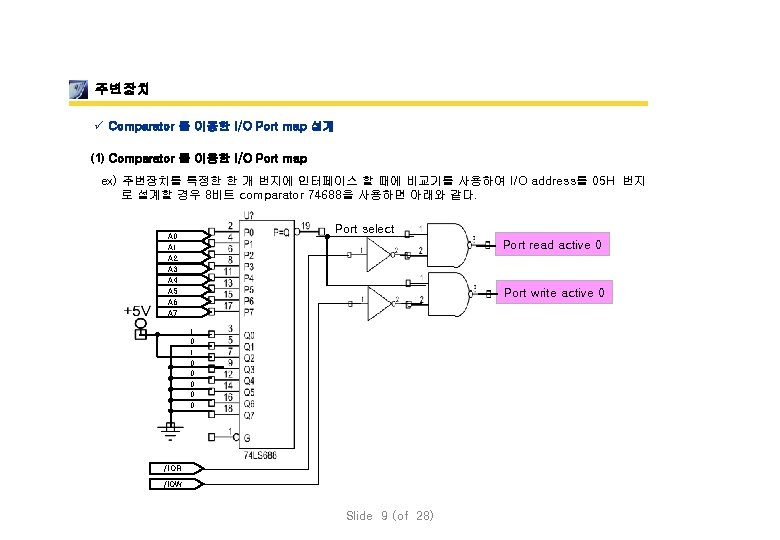

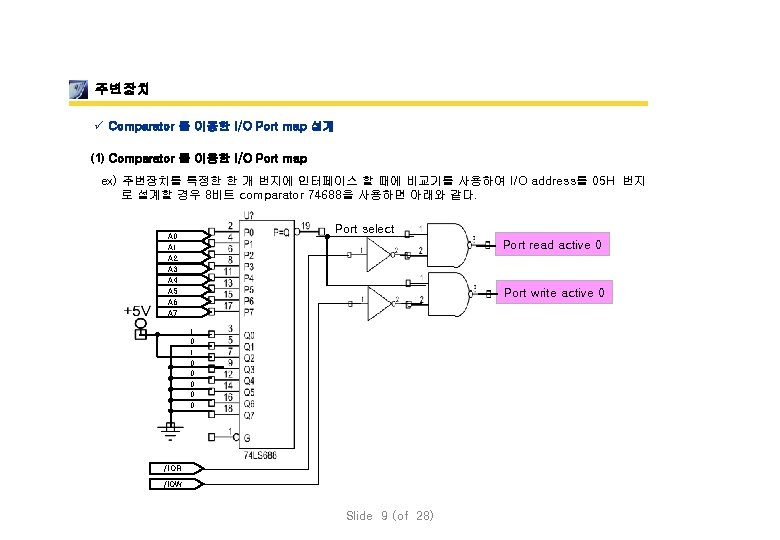

주변장치 ü Comparator 를 이용한 I/O Port map 설계 (1) Comparator 를 이용한 I/O Port map ex) 주변장치를 특정한 한 개 번지에 인터페이스 할 때에 비교기를 사용하여 I/O address를 05 H 번지 로 설계할 경우 8비트 comparator 74688을 사용하면 아래와 같다. Port select A 0 A 1 A 2 A 3 A 4 A 5 A 6 A 7 Port read active 0 Port write active 0 1 0 0 0 /IOR /IOW Slide 9 (of 28)

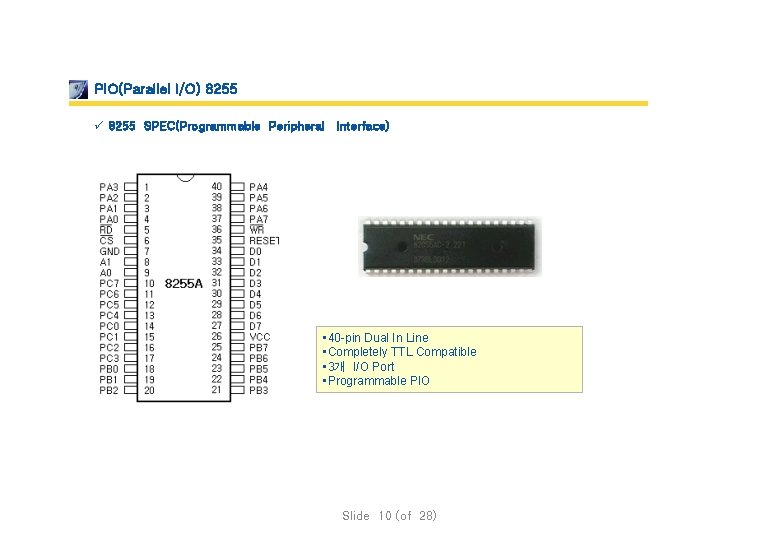

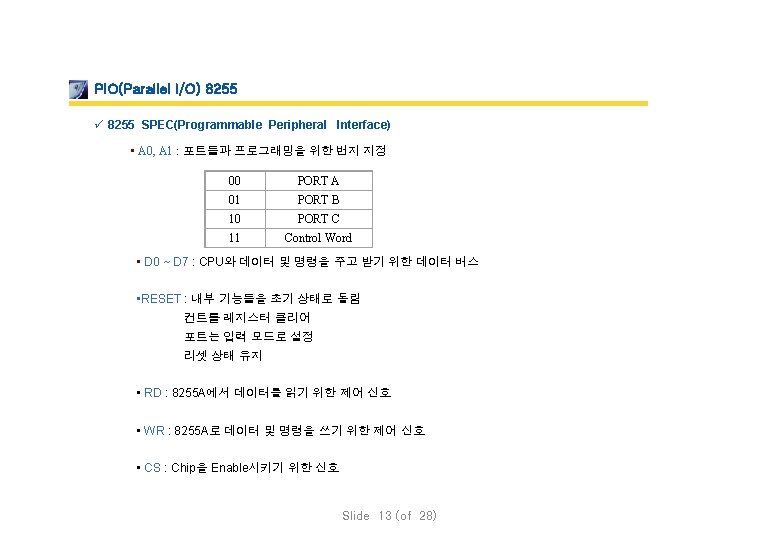

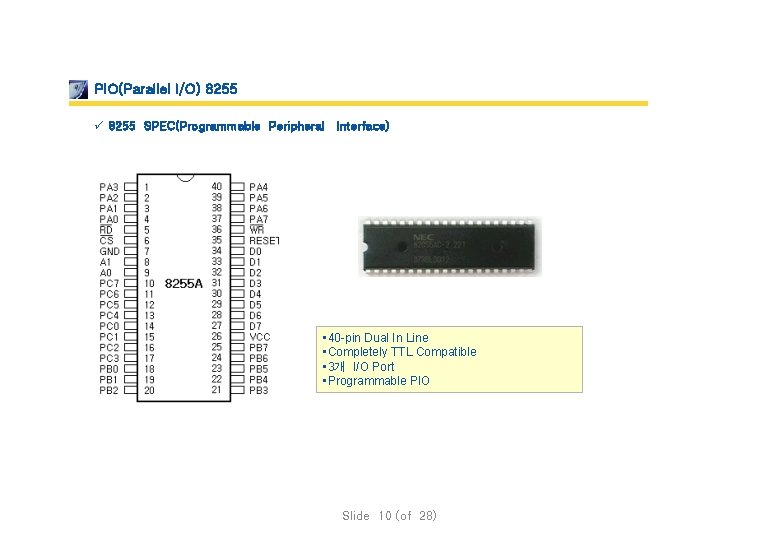

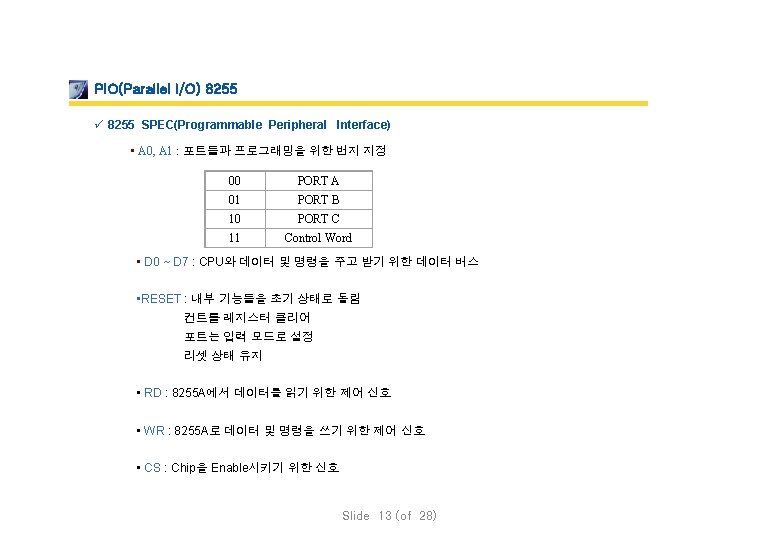

PIO(Parallel I/O) 8255 ü 8255 SPEC(Programmable Peripheral Interface) • 40 -pin Dual In Line • Completely TTL Compatible • 3개 I/O Port • Programmable PIO Slide 10 (of 28)

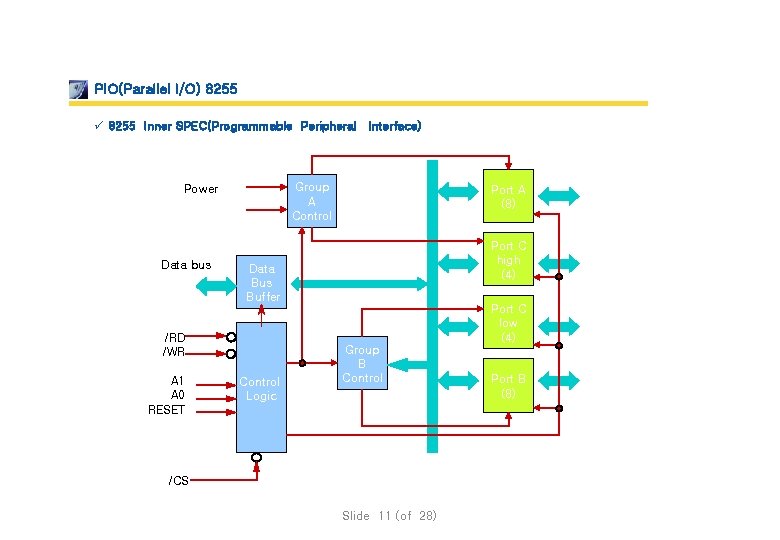

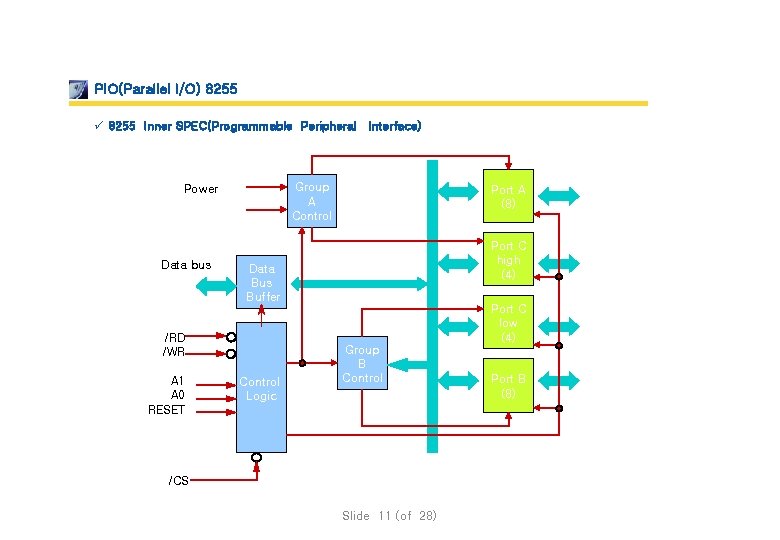

PIO(Parallel I/O) 8255 ü 8255 Inner SPEC(Programmable Peripheral Interface) Group A Control Power Data bus Port C high (4) Data Bus Buffer /RD /WR A 1 A 0 RESET Port A (8) Control Logic Group B Control /CS Slide 11 (of 28) Port C low (4) Port B (8)

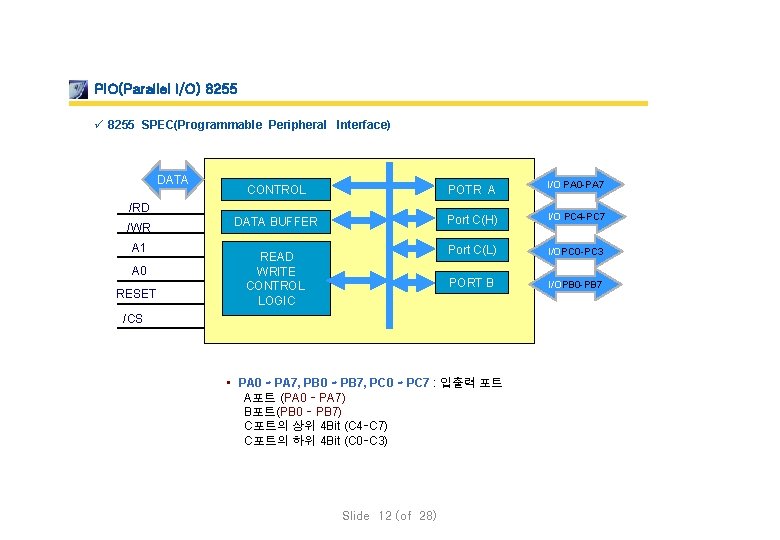

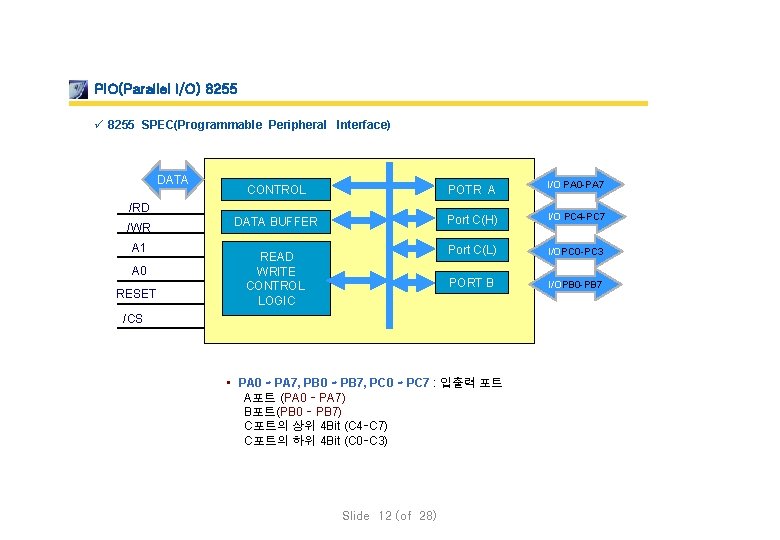

PIO(Parallel I/O) 8255 ü 8255 SPEC(Programmable Peripheral Interface) DATA CONTROL POTR A I/O PA 0 -PA 7 DATA BUFFER Port C(H) I/O PC 4 -PC 7 Port C(L) I/OPC 0 -PC 3 PORT B I/OPB 0 -PB 7 /RD /WR A 1 A 0 RESET READ WRITE CONTROL LOGIC /CS • PA 0 ∼ PA 7, PB 0 ∼ PB 7, PC 0 ∼ PC 7 : 입출력 포트 A포트 (PA 0 ∼ PA 7) B포트(PB 0 ∼ PB 7) C포트의 상위 4 Bit (C 4∼C 7) C포트의 하위 4 Bit (C 0∼C 3) Slide 12 (of 28)

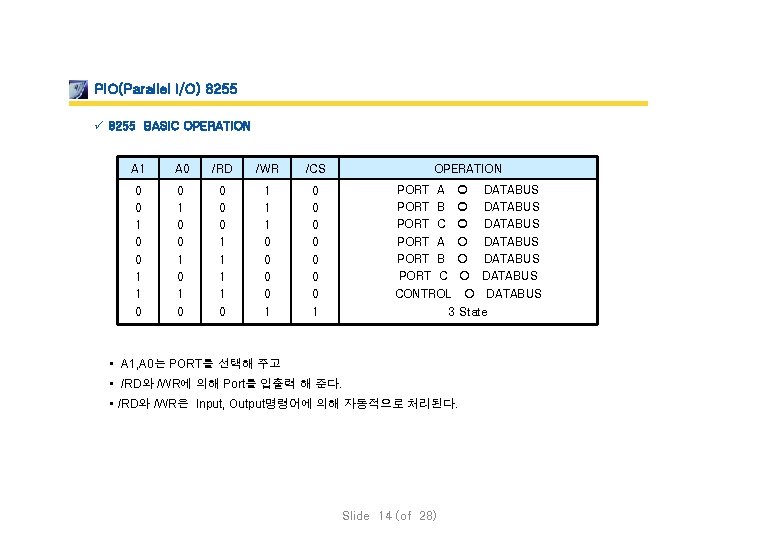

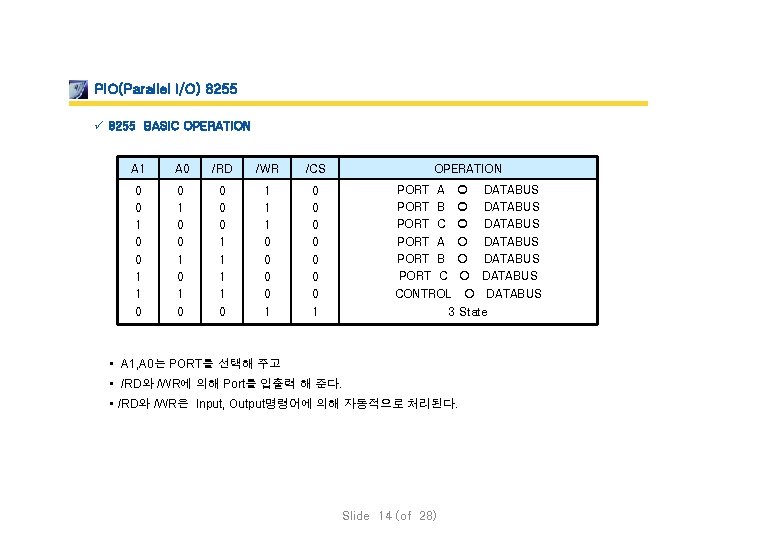

PIO(Parallel I/O) 8255 ü 8255 BASIC OPERATION A 1 A 0 /RD /WR /CS OPERATION 0 0 1 1 0 0 0 0 1 1 1 0 0 0 0 1 PORT A DATABUS PORT B DATABUS PORT C DATABUS CONTROL DATABUS 3 State • A 1, A 0는 PORT를 선택해 주고 • /RD와 /WR에 의해 Port를 입출력 해 준다. • /RD와 /WR은 Input, Output명령어에 의해 자동적으로 처리된다. Slide 14 (of 28)

PIO(Parallel I/O) 8255 ü 8255 CONTROL REGISTER(3번지) D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 PORT C(LOW) 1 : INPUT 0 : OUTPUT MODE SET FLAG 1 : ACTIVE PORT B 1 : INPUT 0 : OUTPUT MODE SELECT 0 : MODE 0 1 : MODE 1 PORT C(UP) 1 : INPUT 0 : OUTPUT PORT A 1 : INPUT 0 : OUTPUT MODE SELECT 00 : MODE 0 01 : MODE 1 1 X : MODE 2 Slide 15 (of 28)

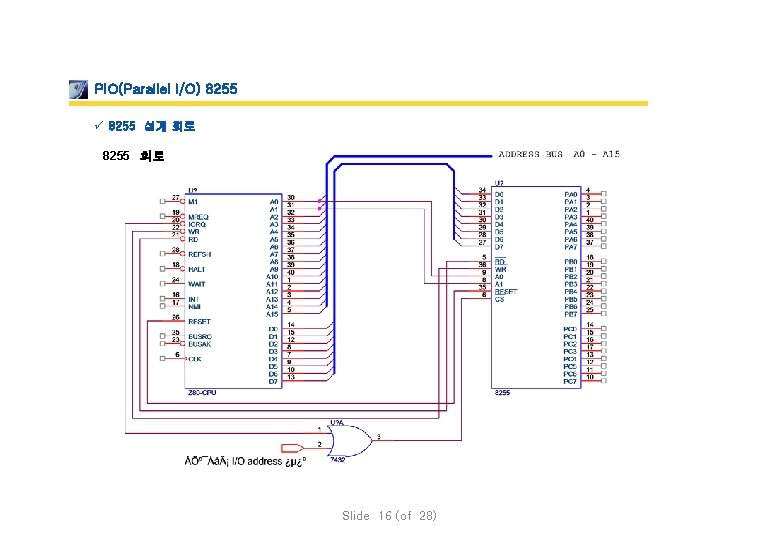

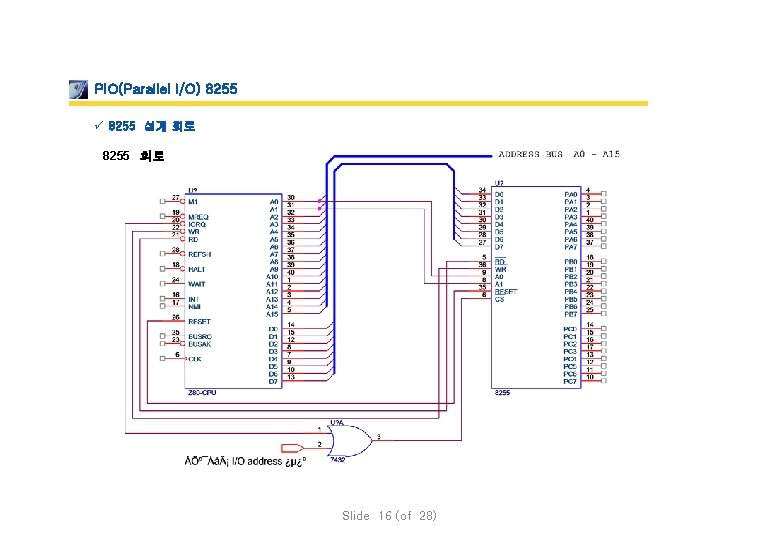

PIO(Parallel I/O) 8255 ü 8255 설계 회로 8255 회로 Slide 16 (of 28)

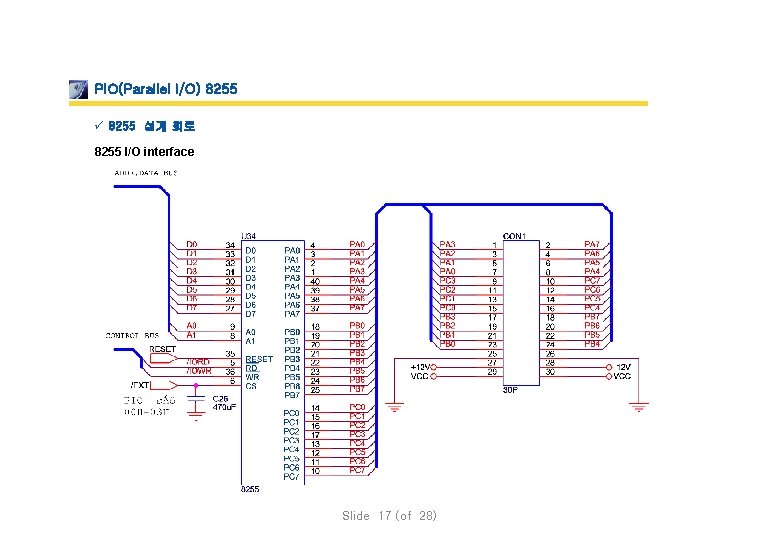

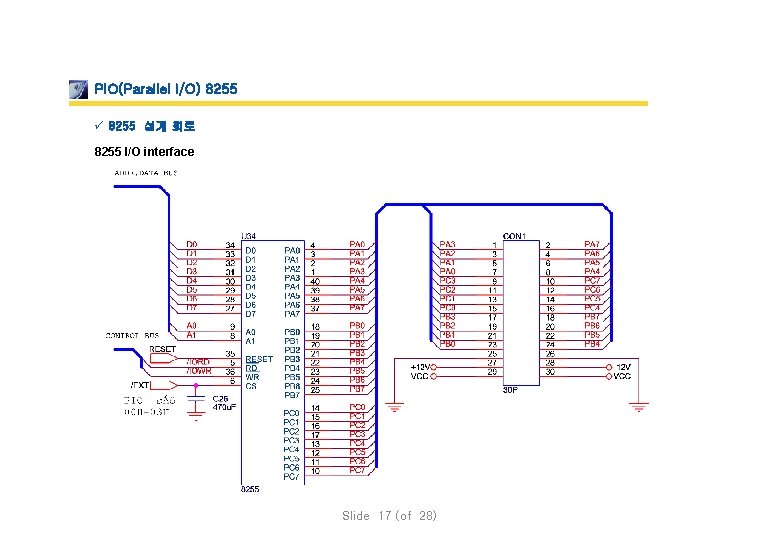

PIO(Parallel I/O) 8255 ü 8255 설계 회로 8255 I/O interface Slide 17 (of 28)

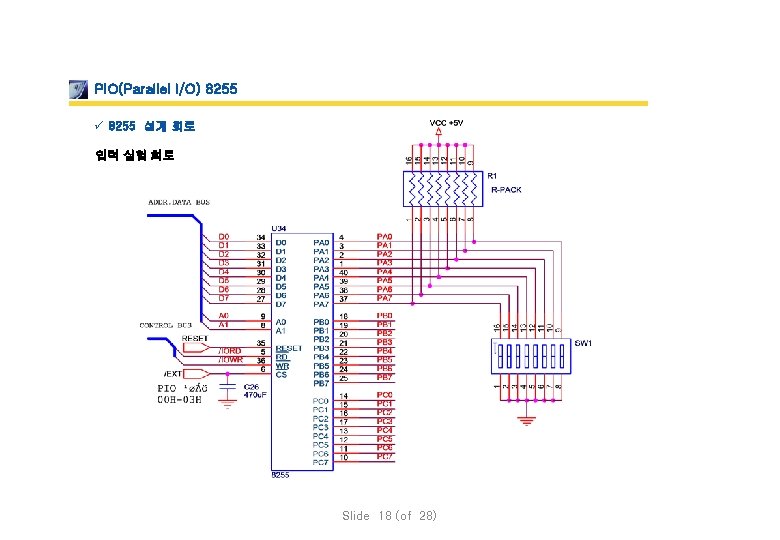

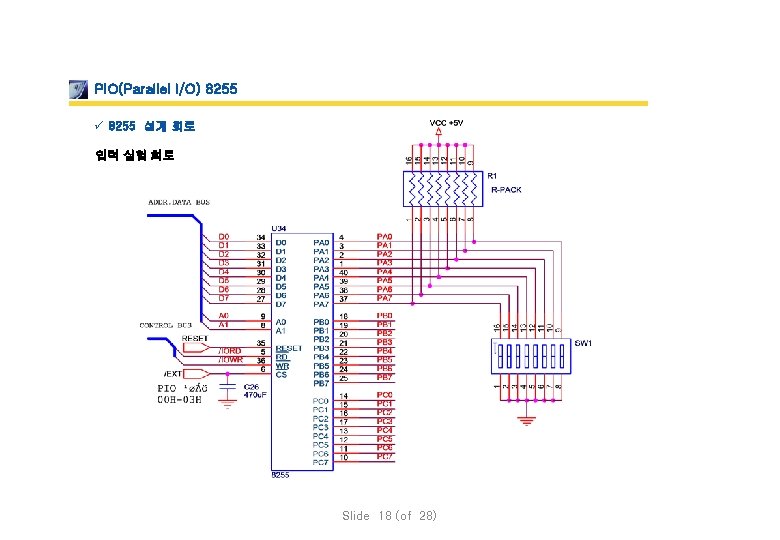

PIO(Parallel I/O) 8255 ü 8255 설계 회로 입력 실험 회로 Slide 18 (of 28)

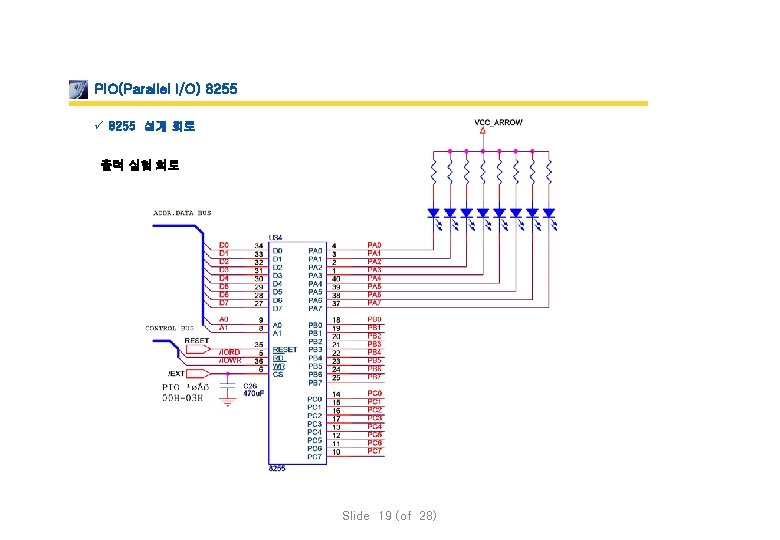

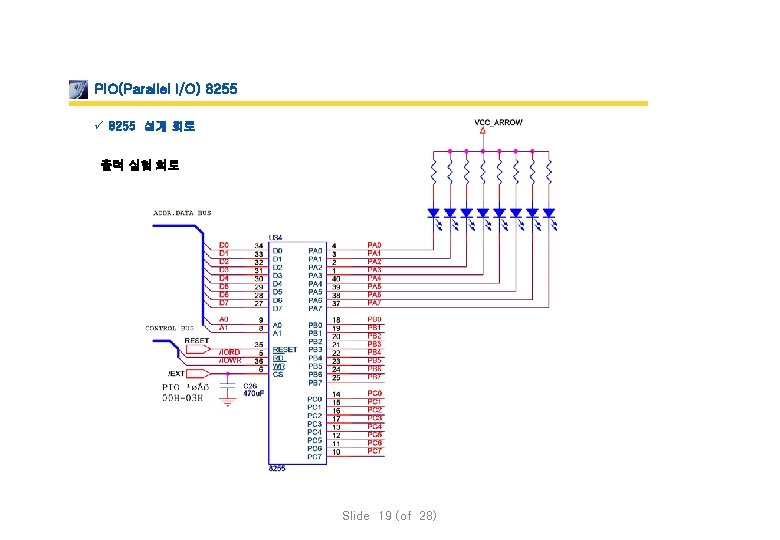

PIO(Parallel I/O) 8255 ü 8255 설계 회로 출력 실험 회로 Slide 19 (of 28)

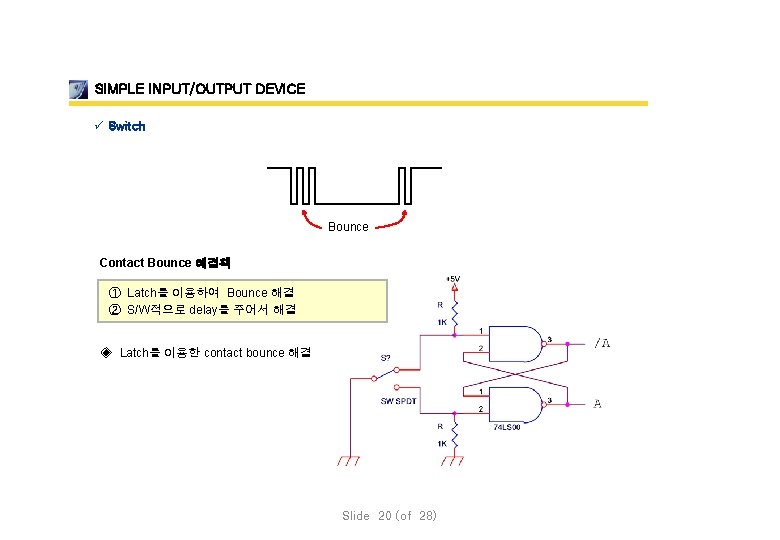

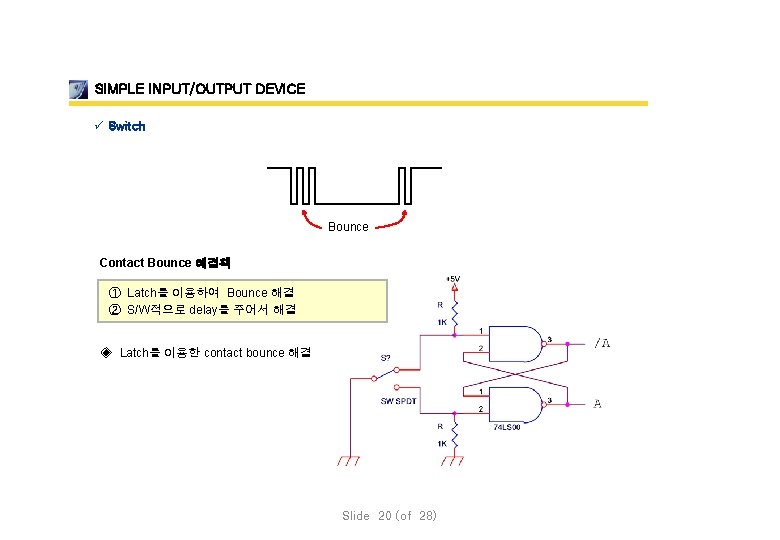

SIMPLE INPUT/OUTPUT DEVICE ü Switch Bounce Contact Bounce 해결책 ① Latch를 이용하여 Bounce 해결 ② S/W적으로 delay를 주어서 해결 ◈ Latch를 이용한 contact bounce 해결 Slide 20 (of 28)

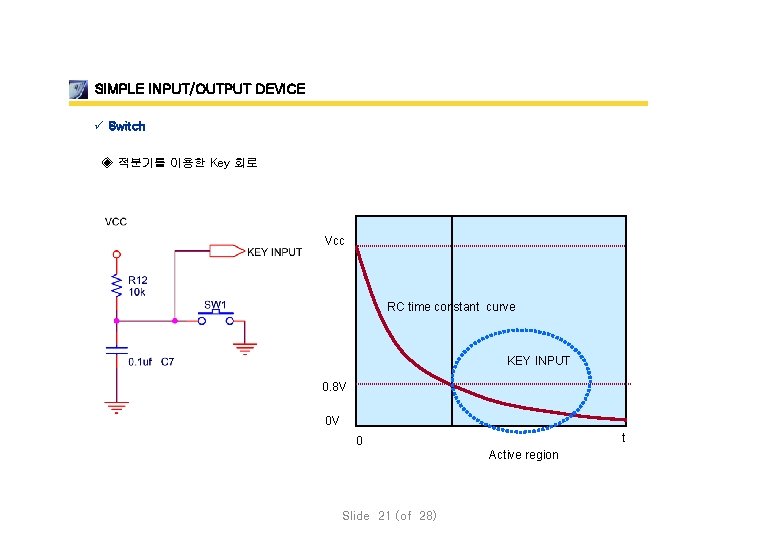

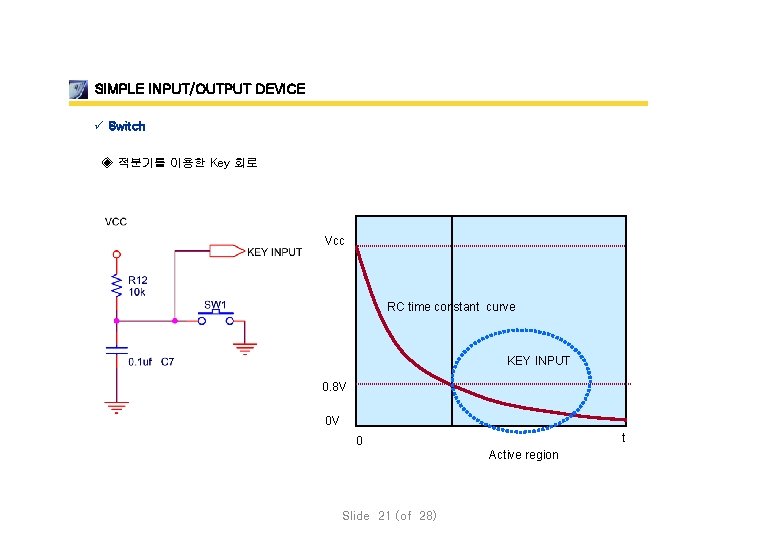

SIMPLE INPUT/OUTPUT DEVICE ü Switch ◈ 적분기를 이용한 Key 회로 Vcc RC time constant curve KEY INPUT 0. 8 V 0 V t 0 Active region Slide 21 (of 28)

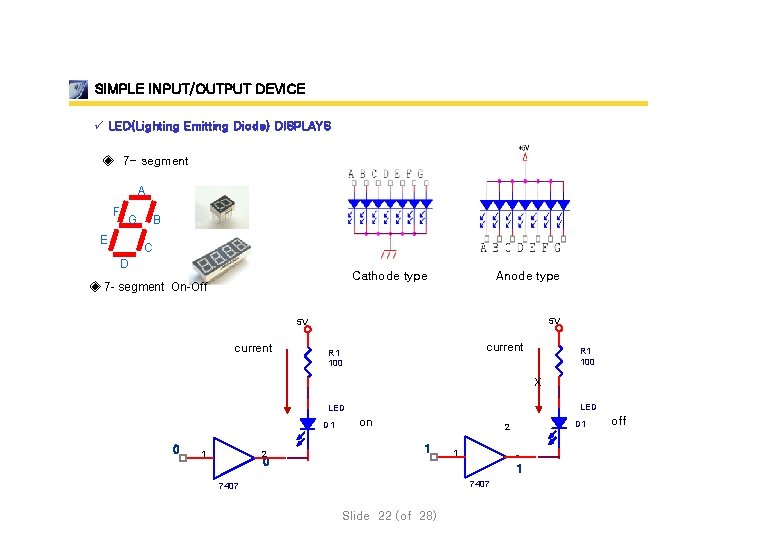

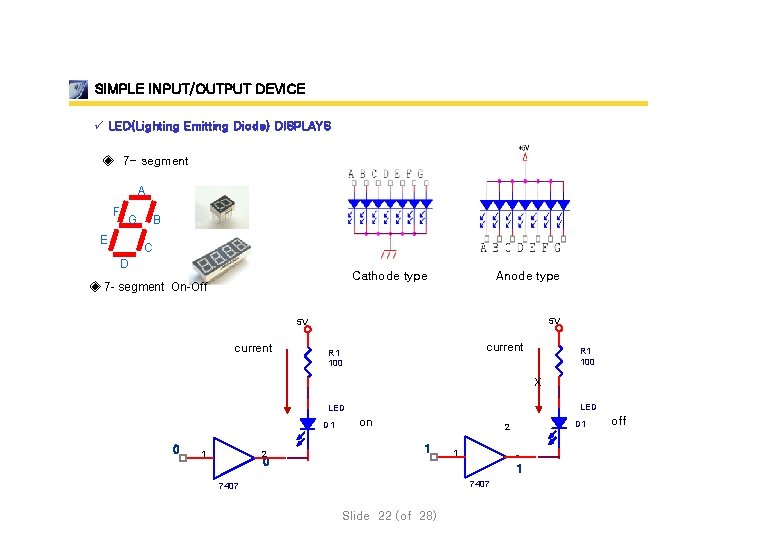

SIMPLE INPUT/OUTPUT DEVICE ü LED(Lighting Emitting Diode) DISPLAYS ◈ 7 - segment A F G E B C D Cathode type ◈ 7 - segment On-Off Anode type 5 V 5 V current R 1 100 x LED D 1 0 1 2 on D 1 2 1 0 1 7407 Slide 22 (of 28) off

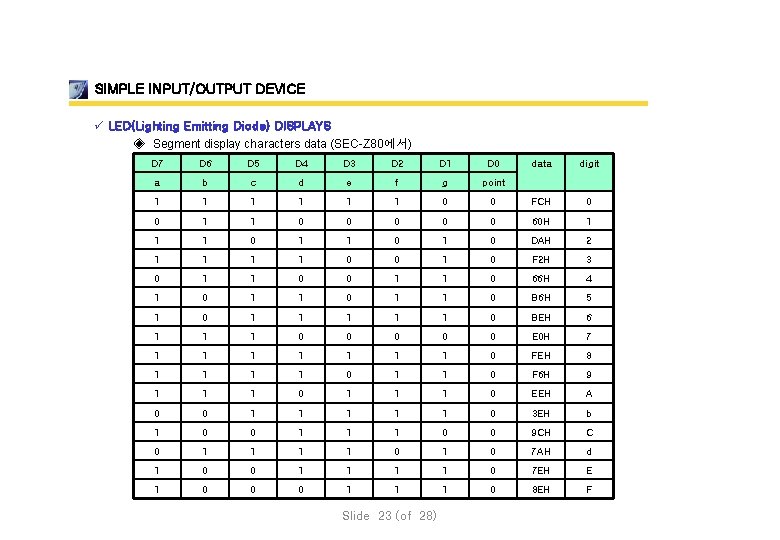

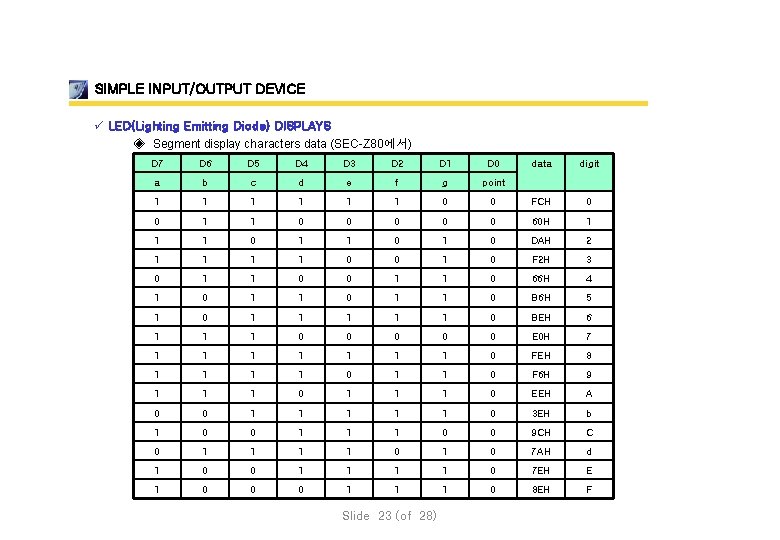

SIMPLE INPUT/OUTPUT DEVICE ü LED(Lighting Emitting Diode) DISPLAYS ◈ Segment display characters data (SEC-Z 80에서) D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 data digit a b c d e f g point 1 1 1 0 0 FCH 0 0 1 1 0 0 0 60 H 1 1 1 0 1 0 DAH 2 1 1 0 0 1 0 F 2 H 3 0 1 1 0 66 H 4 1 0 1 1 0 B 6 H 5 1 0 1 1 1 0 BEH 6 1 1 1 0 0 0 E 0 H 7 1 1 1 1 0 FEH 8 1 1 0 F 6 H 9 1 1 1 0 EEH A 0 0 1 1 1 0 3 EH b 1 0 0 1 1 1 0 0 9 CH C 0 1 1 0 1 0 7 AH d 1 0 0 1 1 0 7 EH E 1 0 0 0 1 1 1 0 8 EH F Slide 23 (of 28)

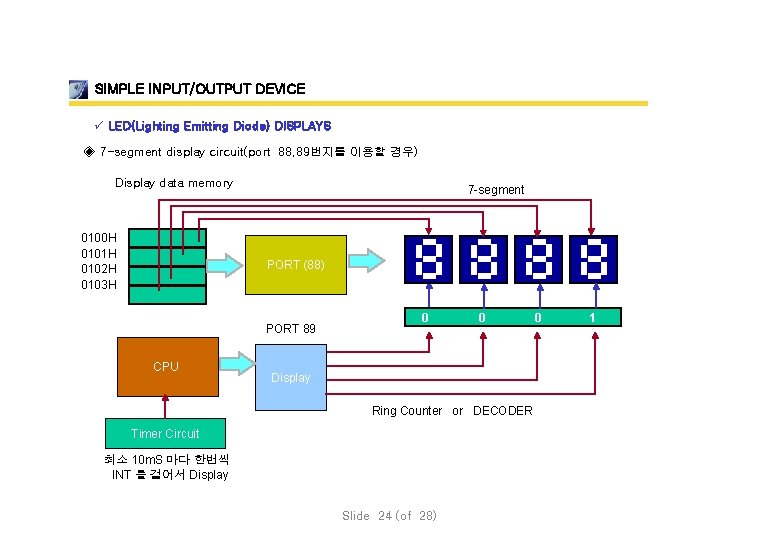

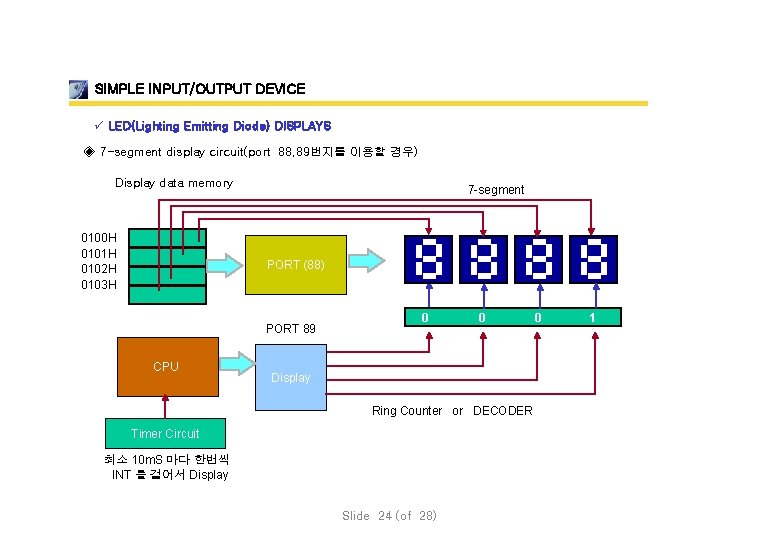

SIMPLE INPUT/OUTPUT DEVICE ü LED(Lighting Emitting Diode) DISPLAYS ◈ 7 -segment display circuit(port 88, 89번지를 이용할 경우) Display data memory 0100 H 0101 H 0102 H 0103 H 7 -segment PORT (88) PORT 89 CPU 0 0 Display Ring Counter or DECODER Timer Circuit 최소 10 m. S 마다 한번씩 INT 를 걸어서 Display Slide 24 (of 28) 0 1

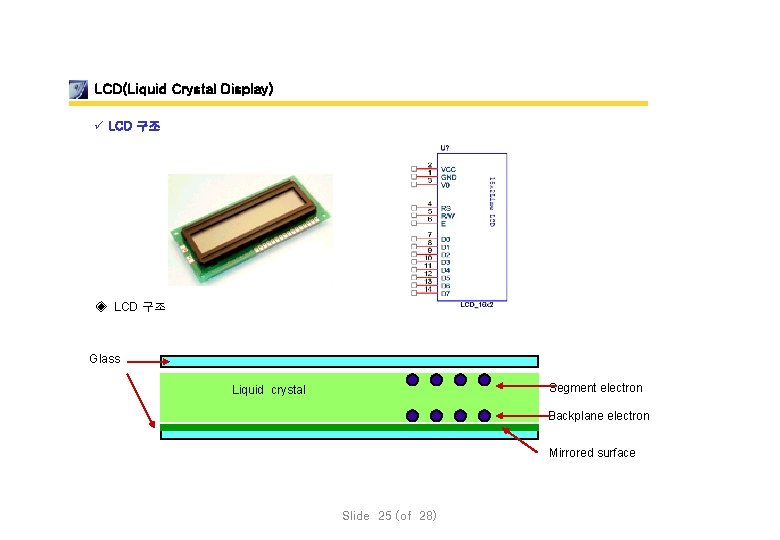

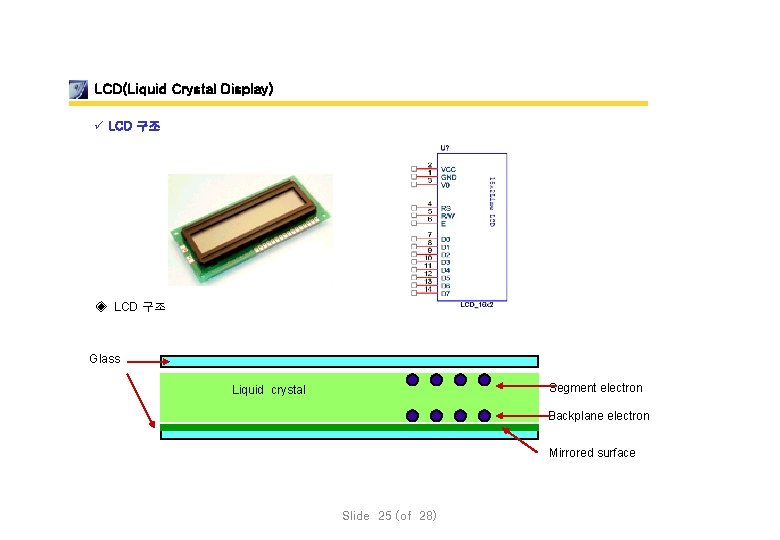

LCD(Liquid Crystal Display) ü LCD 구조 ◈ LCD 구조 Glass Segment electron Liquid crystal Backplane electron Mirrored surface Slide 25 (of 28)

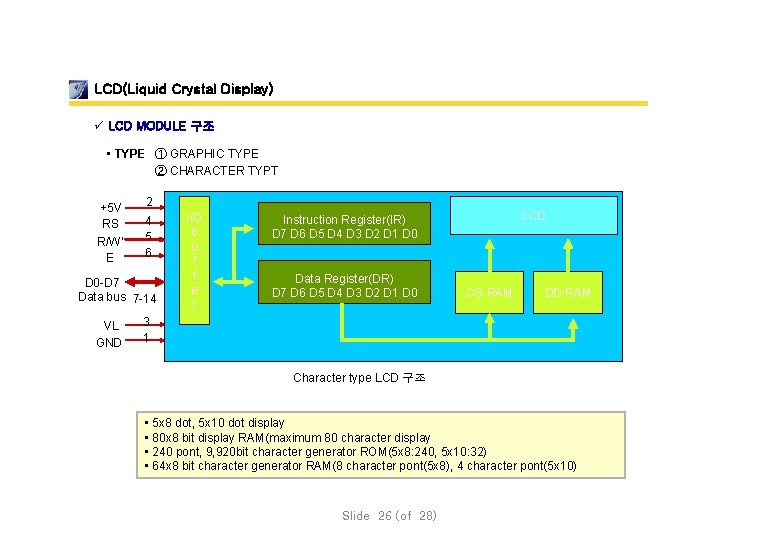

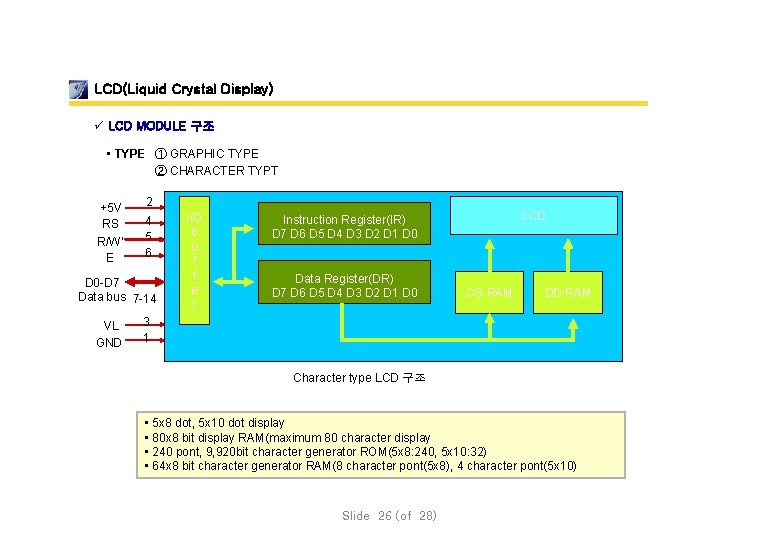

LCD(Liquid Crystal Display) ü LCD MODULE 구조 • TYPE ① GRAPHIC TYPE ② CHARACTER TYPT +5 V RS R/W’ E 2 4 5 6 D 0 -D 7 Data bus 7 -14 VL GND I/O b u f f e r LCD Instruction Register(IR) D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 Data Register(DR) D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 CG RAM DD RAM 3 1 Character type LCD 구조 • 5 x 8 dot, 5 x 10 dot display • 80 x 8 bit display RAM(maximum 80 character display • 240 pont, 9, 920 bit character generator ROM(5 x 8: 240, 5 x 10: 32) • 64 x 8 bit character generator RAM(8 character pont(5 x 8), 4 character pont(5 x 10) Slide 26 (of 28)

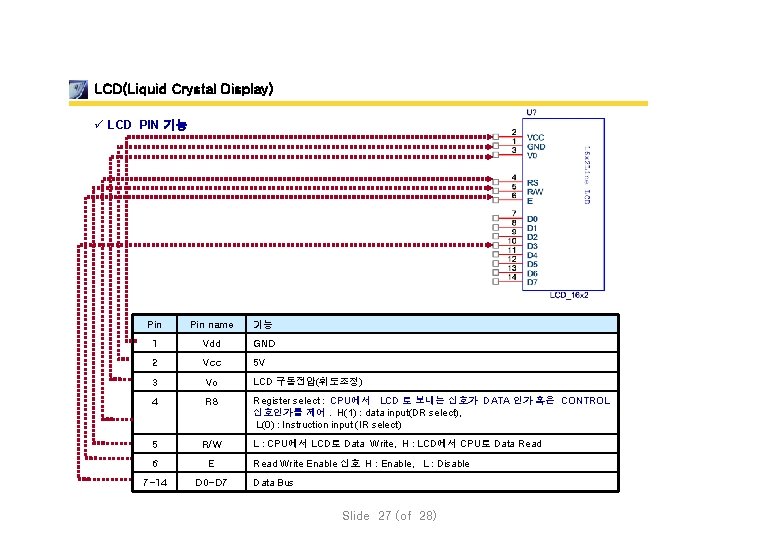

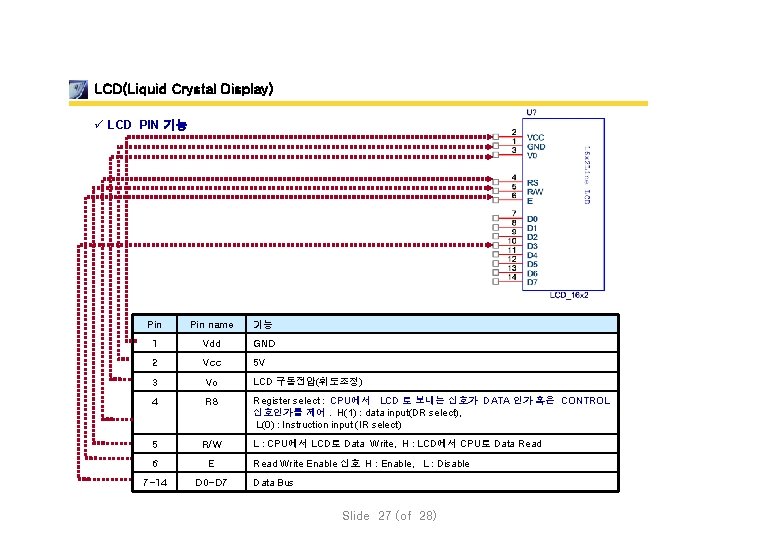

LCD(Liquid Crystal Display) ü LCD PIN 기능 Pin name 기능 1 Vdd GND 2 Vcc 5 V 3 Vo LCD 구동전압(휘도조정) 4 RS Register select : CPU에서 LCD 로 보내는 신호가 DATA 인가 혹은 CONTROL 신호인가를 제어. H(1) : data input(DR select), L(0) : Instruction input (IR select) 5 R/W 6 E 7 -14 D 0 -D 7 L : CPU에서 LCD로 Data Write, H : LCD에서 CPU로 Data Read Write Enable 신호 H : Enable, L : Disable Data Bus Slide 27 (of 28)

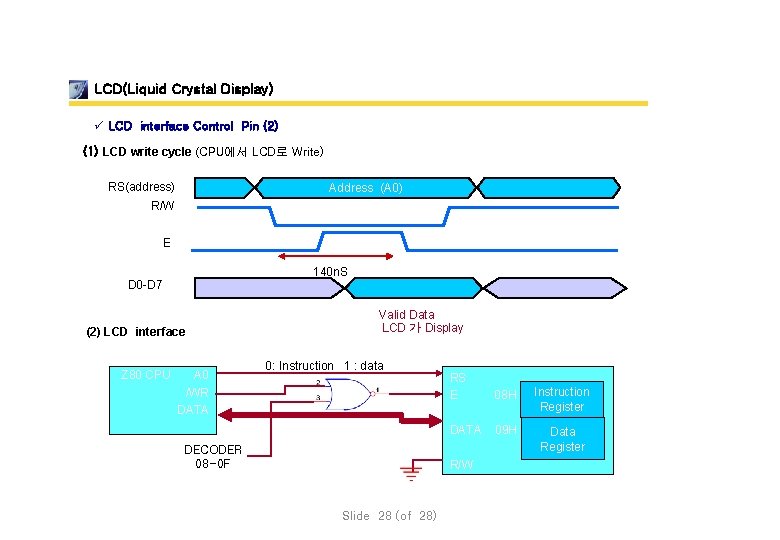

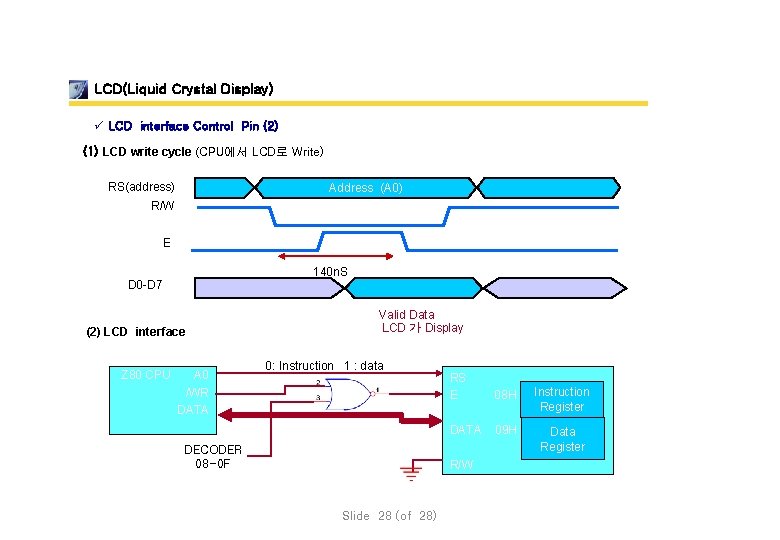

LCD(Liquid Crystal Display) ü LCD interface Control Pin (2) (1) LCD write cycle (CPU에서 LCD로 Write) RS(address) Address (A 0) R/W E 140 n. S D 0 -D 7 (2) LCD interface Z 80 CPU A 0 /WR DATA Valid Data LCD 가 Display 0: Instruction 1 : data DECODER 08 -0 F RS E 08 H DATA 09 H R/W Slide 28 (of 28) Instruction Register Data Register