10 G PON Downlink Evaluation Status Jubin MITRA

10 G PON Downlink Evaluation Status Jubin MITRA, Jozsef IMREK, Erno DAVID Wigner Research Center for Physics (HU) 23 March, 2016

Our Test Plans and Results • Test 1 • Transceiver Toolkit Loopback Tests, 9. 6 Gbps, BER, Eye Diagram • Plans: ttps: //indico. cern. ch/event/496404/contribution/3/attachments/1228107/1799154/PON_ Jubin_15_02_16. pdf • Results: https: //indico. cern. ch/event/497118/contribution/6/attachments/1231962/1806445/PON_Jubin_22_02_16. pdf • Test 1. 5 • Arria 10 transceiver features test: PMA Analog Reset, PMA Clock Slip (simulation + HW) • Test 2 • OLT Pattern Generator and ONU Pattern Checker in loopback mode (SFP+, single Arria 10 transceiver) • Test 3 • Same as the Test 2 but with the final OLT and ONU SFP+ modules, and included 10 G PON splitter 2

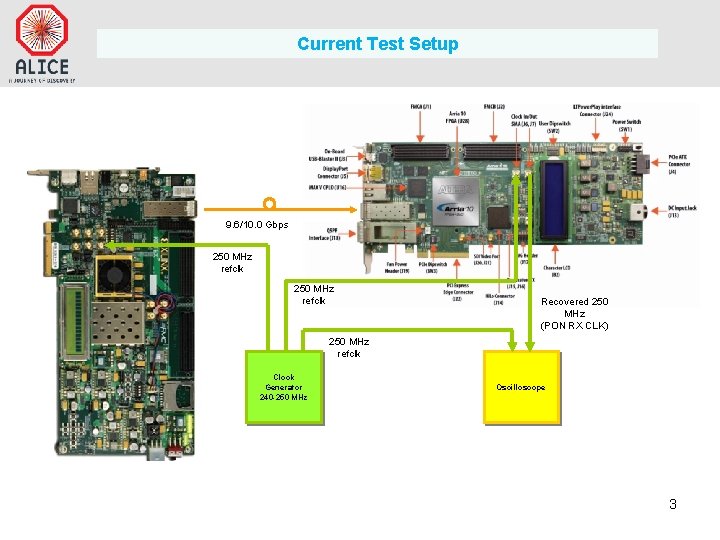

Current Test Setup 9. 6/10. 0 Gbps 250 MHz refclk Recovered 250 MHz (PON RX CLK) 250 MHz refclk Clock Generator 240 -250 MHz Oscilloscope 3

LHC Clock Distribution (1) CRU Arria 10 FPGA 10 G PON REFCLK 120 MHz 10 G PON External PLL + Jitter Cleaner + Fanout Buffer 10 G PON Transceiver 240 MHz TTS (ONU) 1 40 MHz 2 184 bit Busy 76543210 Phase Control PMA Reset GBT 3 GBT Transmitters Bank 0 120 MHz 6 x 40 bit GBT TX 80/112 bit Downlink Logic Bank 0 250 MHz 512 bit 2400 MHz GBT_BANK_0_REFCLK 120 MHz GBT Bank 0 – Link 0. . 5 (Consist 6 adjacent bonded Arria 10 transceiver) ATX PLL 6 x 2 bit TX GBTx 2 bit 120 MHz GBT Receivers Bank 0 6 x 40 bit GBT RX 80/112 bit 6 x The number of GBT Banks is equal to GBT Links / 6 GBT_BANK_7_REFCLK 120 MHz TX SCA 2 bit Uplink Logic Bank 0 250 MHz 512 bit RX SCA RX GBTx 2 bit 4

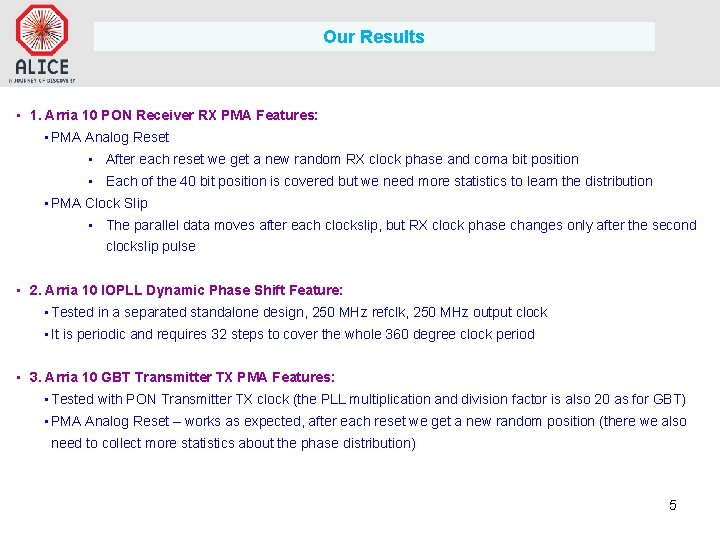

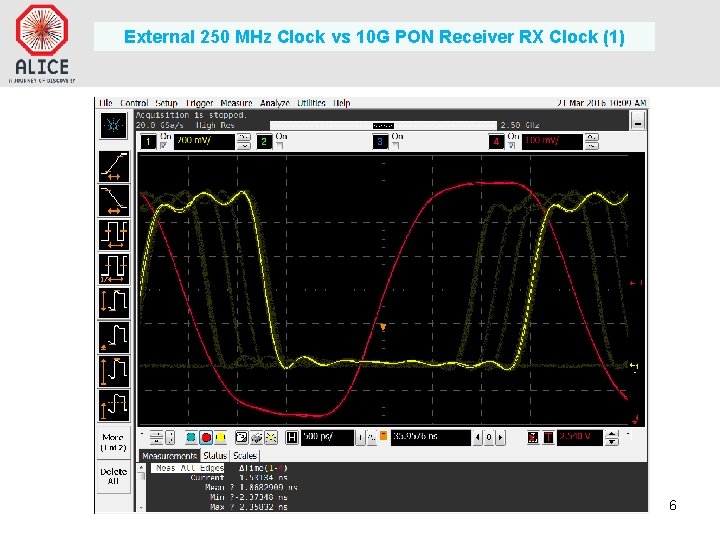

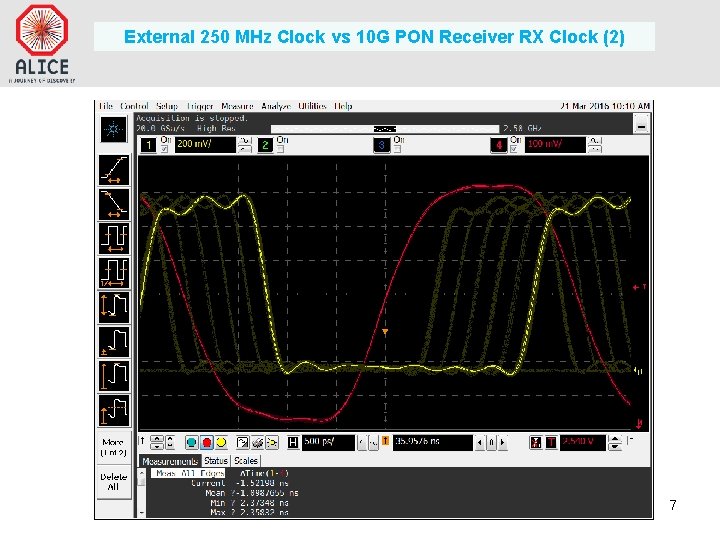

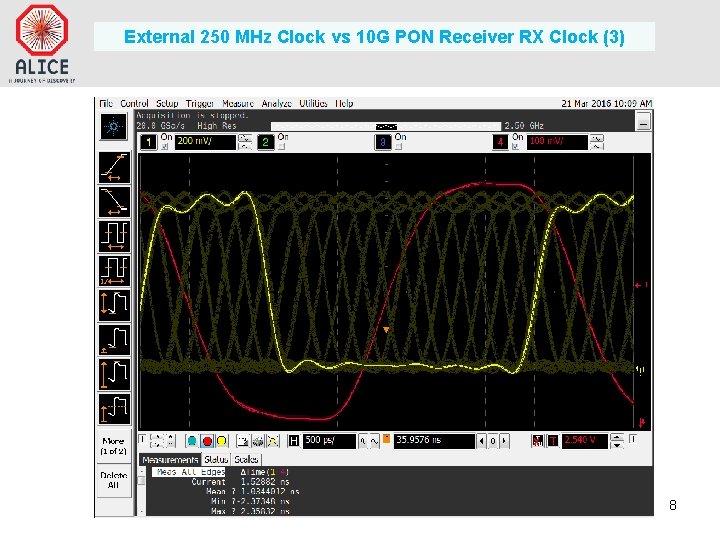

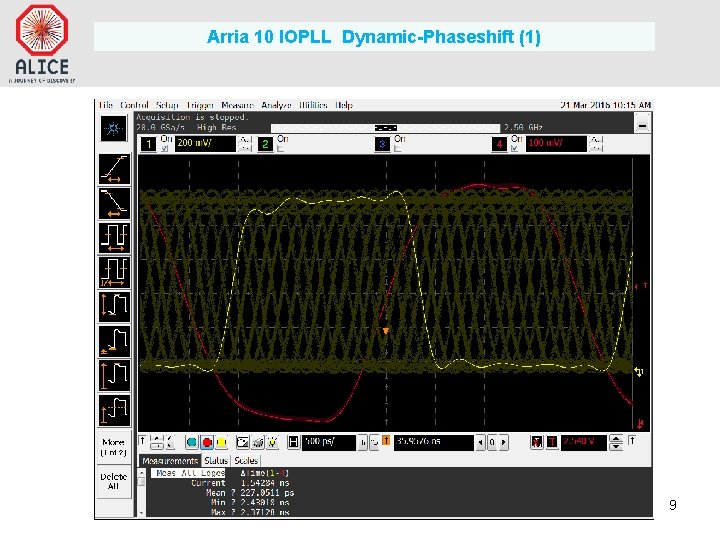

Our Results • 1. Arria 10 PON Receiver RX PMA Features: • PMA Analog Reset • After each reset we get a new random RX clock phase and coma bit position • Each of the 40 bit position is covered but we need more statistics to learn the distribution • PMA Clock Slip • The parallel data moves after each clockslip, but RX clock phase changes only after the second clockslip pulse • 2. Arria 10 IOPLL Dynamic Phase Shift Feature: • Tested in a separated standalone design, 250 MHz refclk, 250 MHz output clock • It is periodic and requires 32 steps to cover the whole 360 degree clock period • 3. Arria 10 GBT Transmitter TX PMA Features: • Tested with PON Transmitter TX clock (the PLL multiplication and division factor is also 20 as for GBT) • PMA Analog Reset – works as expected, after each reset we get a new random position (there we also need to collect more statistics about the phase distribution) 5

External 250 MHz Clock vs 10 G PON Receiver RX Clock (1) 6

External 250 MHz Clock vs 10 G PON Receiver RX Clock (2) 7

External 250 MHz Clock vs 10 G PON Receiver RX Clock (3) 8

Arria 10 IOPLL Dynamic-Phaseshift (1) 9

Our Problems and Next Steps • 1. We used 250 MHz as reference clock (10. 0 Gbps) instead 240 MHz (9. 6 Gbps): • It seems that the issue is on the Kintex 7 side • Should we investigate this or get help from PON or CTP Xilinx experts? • 2. We managed to send only 40 -bit PON “frames”: • We started with our 40 -bit frame generator to save time, but we experienced some strange bit flips with longer frames • Only last day started to test the optical link between the KC 705 and the Arria 10 devkit with BER test tools and we found that the link is very noisy • Our next step is to test the link with BER test tools and fix it before doing any further PON HW tests • 3. We managed the measurements from System Console with TCL scripts : • We found very productively to use the Altera ISSP tools and the TCL scripts in parallel • But for the final tests we need our control state machines written in VHDL • 4. Decide about the 240 MHz -> 40 MHz PLL: • Do we need 40 / 120 / 240 MHz for the GBT-FPGA? 10

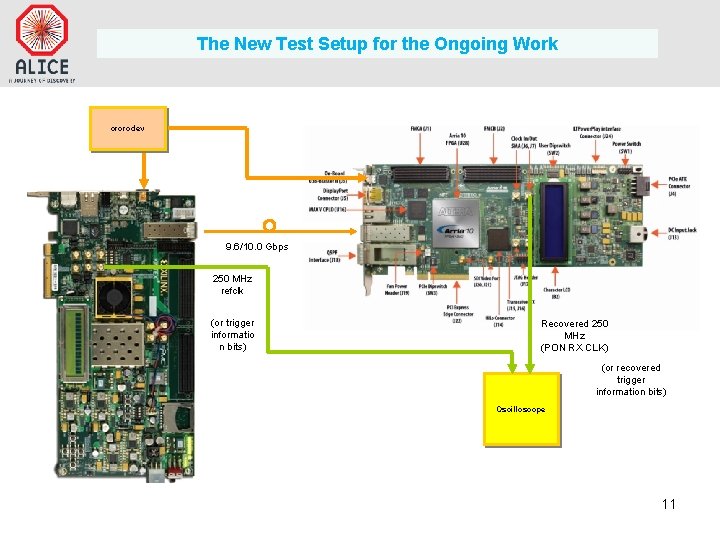

The New Test Setup for the Ongoing Work crorcdev 9. 6/10. 0 Gbps 250 MHz refclk (or trigger informatio n bits) Recovered 250 MHz (PON RX CLK) (or recovered trigger information bits) Oscilloscope 11

- Slides: 11