10 FPGA Verilog HDL 2008 2 event transfer

![语法: <assign> [#delay] [strength] <net_name> = <expressions> 例如: wire out; assign out =in_data_a|in_data_b; //也可以不经assign而用wire直接指定,这种方 语法: <assign> [#delay] [strength] <net_name> = <expressions> 例如: wire out; assign out =in_data_a|in_data_b; //也可以不经assign而用wire直接指定,这种方](https://slidetodoc.com/presentation_image_h/b62fbf1ae7e9bcd25145924a90af697e/image-20.jpg)

![示例10. 10: module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i; always 示例10. 10: module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i; always](https://slidetodoc.com/presentation_image_h/b62fbf1ae7e9bcd25145924a90af697e/image-36.jpg)

![下面是while语句应用例子(示例10. 11) module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i; always 下面是while语句应用例子(示例10. 11) module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i; always](https://slidetodoc.com/presentation_image_h/b62fbf1ae7e9bcd25145924a90af697e/image-37.jpg)

![下面是repeat语句应用例子(示例10. 12 ) module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i; 下面是repeat语句应用例子(示例10. 12 ) module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i;](https://slidetodoc.com/presentation_image_h/b62fbf1ae7e9bcd25145924a90af697e/image-38.jpg)

![下面是forever语句应用例子(示例10. 13) module verilog_1(input[7: 0] a, output reg[7: 0] y ); initial begin forever 下面是forever语句应用例子(示例10. 13) module verilog_1(input[7: 0] a, output reg[7: 0] y ); initial begin forever](https://slidetodoc.com/presentation_image_h/b62fbf1ae7e9bcd25145924a90af697e/image-40.jpg)

- Slides: 51

第 10章 FPGA Verilog HDL�程基� © 2008 2 ®

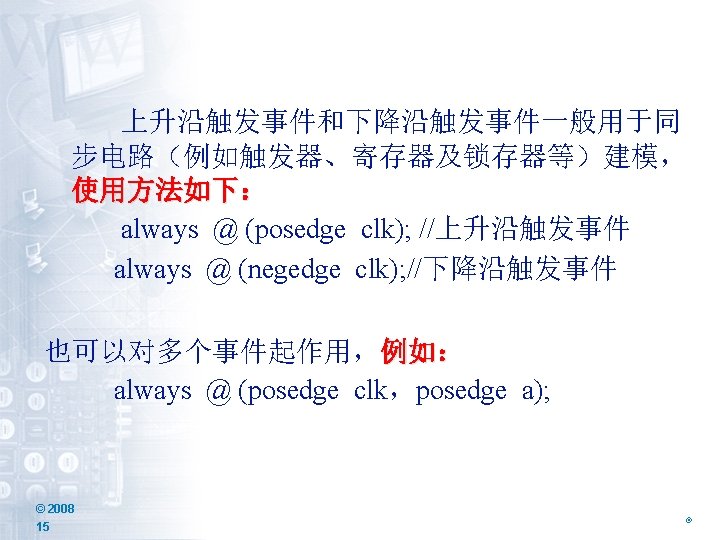

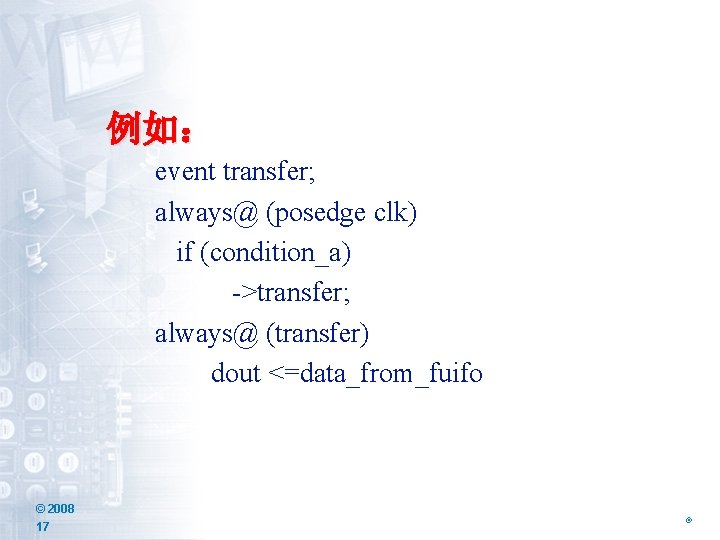

例如: event transfer; always@ (posedge clk) if (condition_a) ->transfer; always@ (transfer) dout <=data_from_fuifo © 2008 17 ®

![语法 assign delay strength netname expressions 例如 wire out assign out indataaindatab 也可以不经assign而用wire直接指定这种方 语法: <assign> [#delay] [strength] <net_name> = <expressions> 例如: wire out; assign out =in_data_a|in_data_b; //也可以不经assign而用wire直接指定,这种方](https://slidetodoc.com/presentation_image_h/b62fbf1ae7e9bcd25145924a90af697e/image-20.jpg)

语法: <assign> [#delay] [strength] <net_name> = <expressions> 例如: wire out; assign out =in_data_a|in_data_b; //也可以不经assign而用wire直接指定,这种方 式较为简捷 wire out =in_data_a|in_data_b; © 2008 20 ®

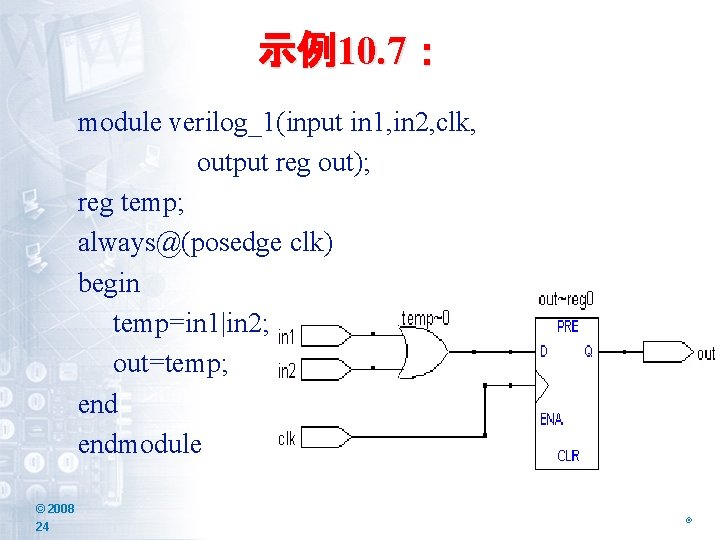

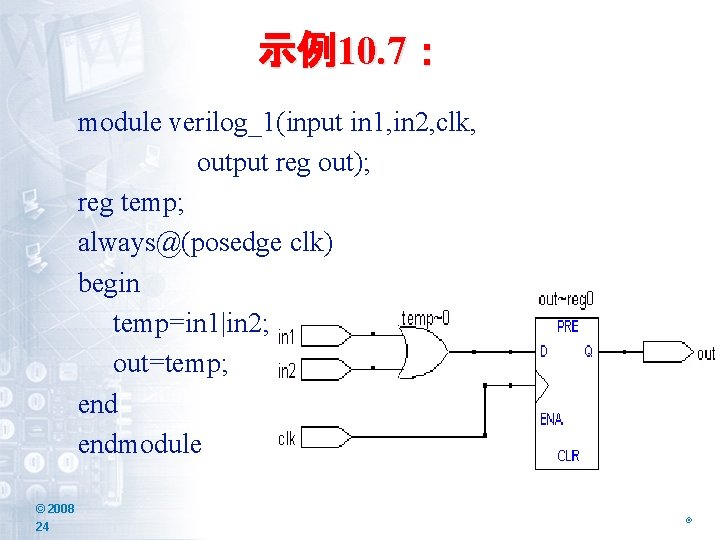

示例10. 7: module verilog_1(input in 1, in 2, clk, output reg out); reg temp; always@(posedge clk) begin temp=in 1|in 2; out=temp; endmodule © 2008 24 ®

示例10. 8: module verilog_1(input in 1, in 2, clk, output reg out); reg temp; always@(posedge clk) begin out=in 1|in 2; endmodule 示例10. 8综合结果和示例1的综合结果完全一样。 © 2008 25 ®

示例10. 9: module verilog_1(input in 1, in 2, clk, output reg out); reg temp; always@(posedge clk) begin temp<=in 1|in 2; out<=temp; endmodule © 2008 27 ®

module verilog_1(input in 1, in 2, clk, output reg out); reg temp; always@(posedge clk) begin temp=in 1|in 2; out=temp; endmodule verilog_2(input in 1, in 2, clk, output reg out); reg temp; always@(posedge clk) begin temp<=in 1|in 2; out<=temp; endmodule verilog_3(input in 1, in 2, clk, output reg out); reg temp; always@(posedge clk) begin out=temp; temp=in 1|in 2; endmodule verilog_4(input in 1, in 2, clk, output reg out); reg temp; always@(posedge clk) begin out<=temp; temp<=in 1|in 2; endmodule verilog_5(input in 1, in 2, clk, output reg out); reg temp; always@( clk) begin temp=in 1|in 2; out=temp; endmodule verilog_6(input in 1, in 2, clk, output reg out); reg temp; always@( in 1, in 2) begin temp<=in 1|in 2; out<=temp; endmodule © 2008 28 ®

© 2008 29 ®

![示例10 10 module verilog1input7 0 a output reg7 0 y integer i always 示例10. 10: module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i; always](https://slidetodoc.com/presentation_image_h/b62fbf1ae7e9bcd25145924a90af697e/image-36.jpg)

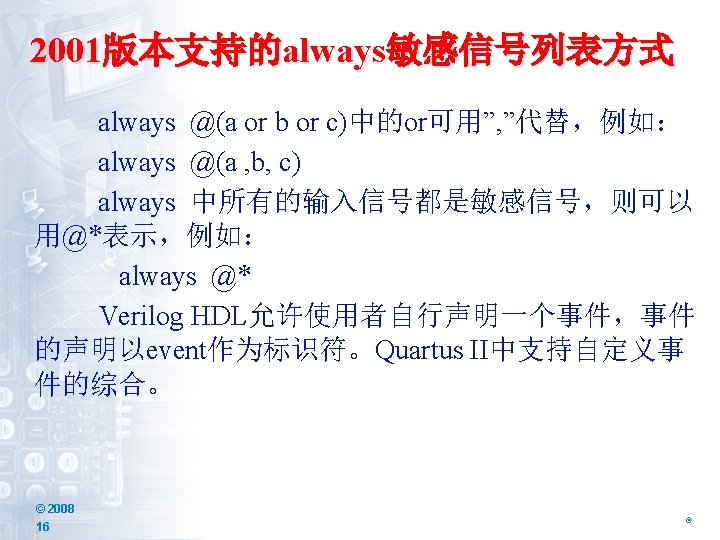

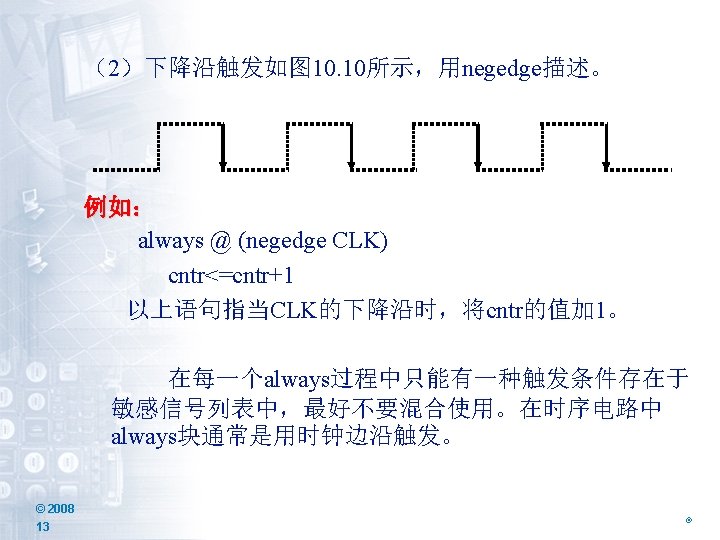

示例10. 10: module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i; always @(a) begin for(i=0; i<7; i=i+1) begin y[i]=~a[i]&a[i+1]; end endmodule © 2008 36 ®

![下面是while语句应用例子示例10 11 module verilog1input7 0 a output reg7 0 y integer i always 下面是while语句应用例子(示例10. 11) module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i; always](https://slidetodoc.com/presentation_image_h/b62fbf1ae7e9bcd25145924a90af697e/image-37.jpg)

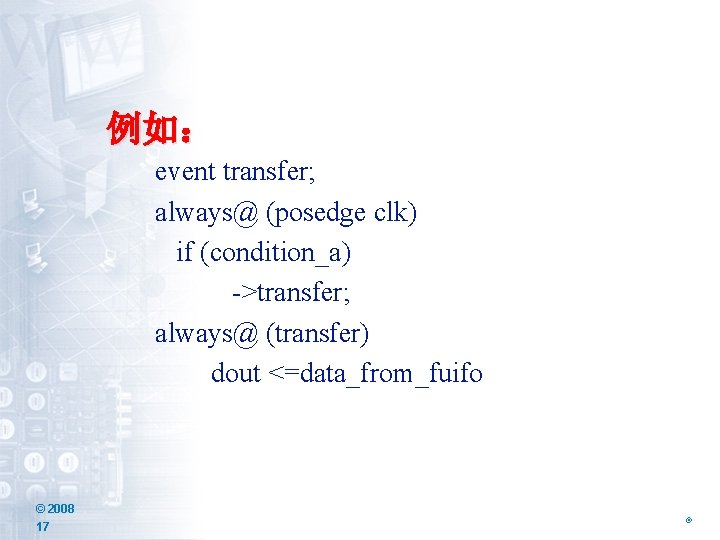

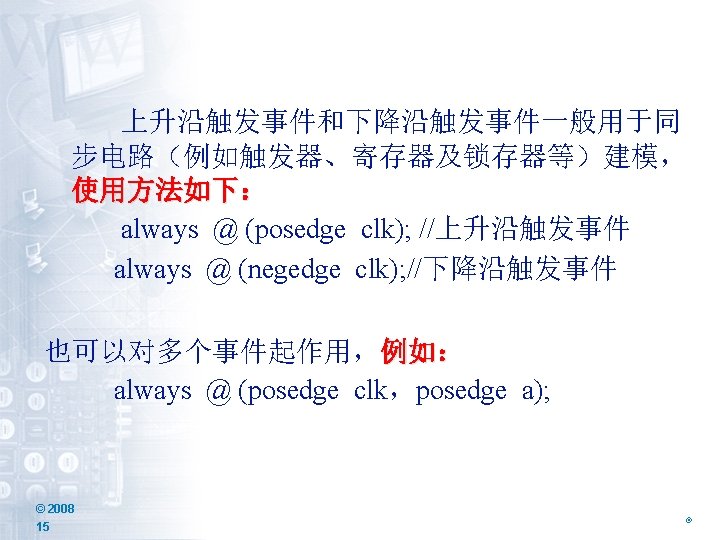

下面是while语句应用例子(示例10. 11) module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i; always @(a) begin i=0; while(i<7) begin y[i]=~a[i]&a[i+1]; i=i+1; end endmodule © 2008 37 ®

![下面是repeat语句应用例子示例10 12 module verilog1input7 0 a output reg7 0 y integer i 下面是repeat语句应用例子(示例10. 12 ) module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i;](https://slidetodoc.com/presentation_image_h/b62fbf1ae7e9bcd25145924a90af697e/image-38.jpg)

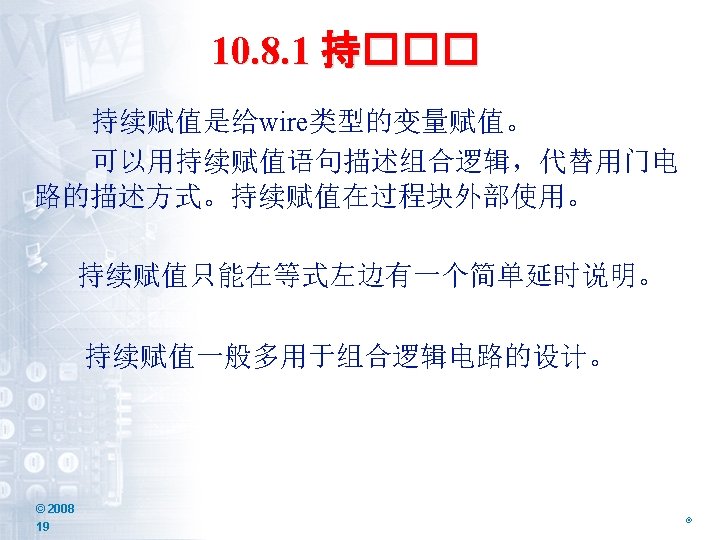

下面是repeat语句应用例子(示例10. 12 ) module verilog_1(input[7: 0] a, output reg[7: 0] y ); integer i; always @(a) begin i=0; repeat(8) begin y[i]=y[i]&a[i]; i=i+1; end endmodule © 2008 38 ®

![下面是forever语句应用例子示例10 13 module verilog1input7 0 a output reg7 0 y initial begin forever 下面是forever语句应用例子(示例10. 13) module verilog_1(input[7: 0] a, output reg[7: 0] y ); initial begin forever](https://slidetodoc.com/presentation_image_h/b62fbf1ae7e9bcd25145924a90af697e/image-40.jpg)

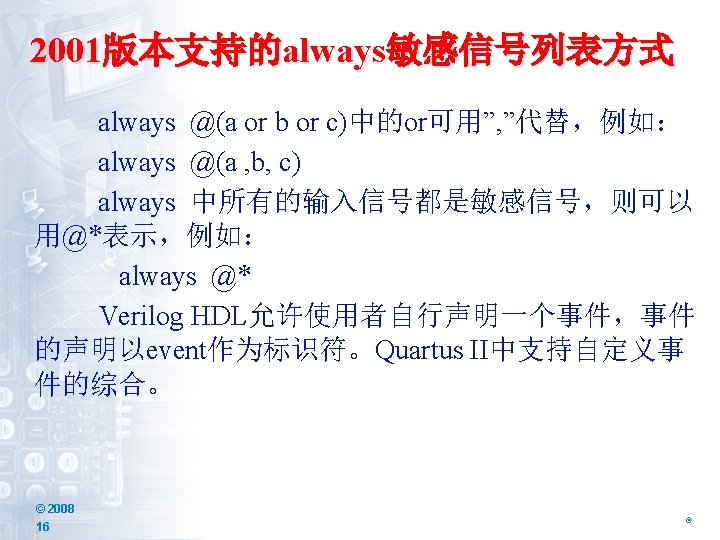

下面是forever语句应用例子(示例10. 13) module verilog_1(input[7: 0] a, output reg[7: 0] y ); initial begin forever y[1]=a[2]&a[4]; end Endmodule 上述程序在quartus中综合没有报错,但没有电路 输出。 © 2008 40 ®

10. 10 Verilog HDL任�及函数定� © 2008 41 ®

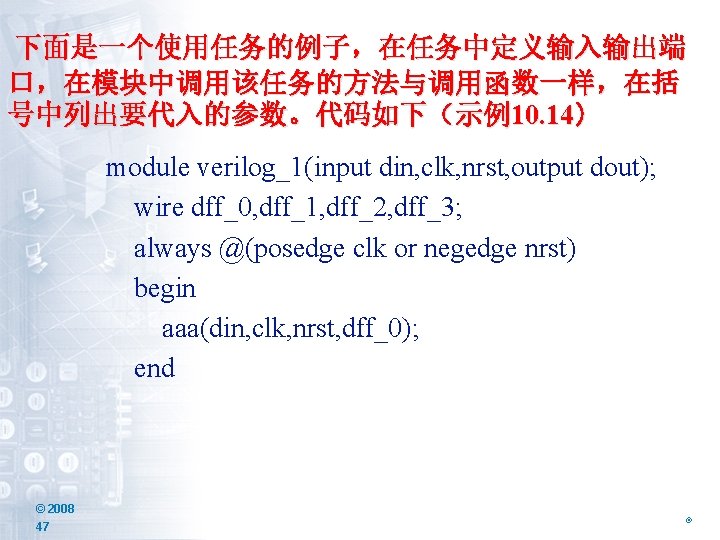

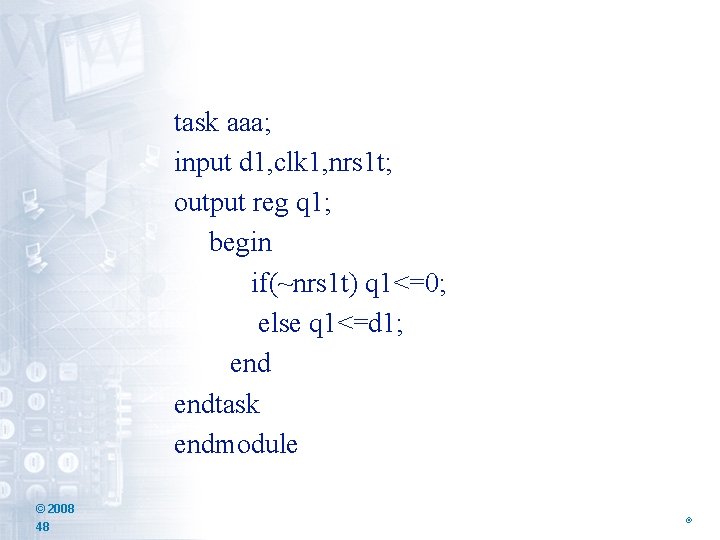

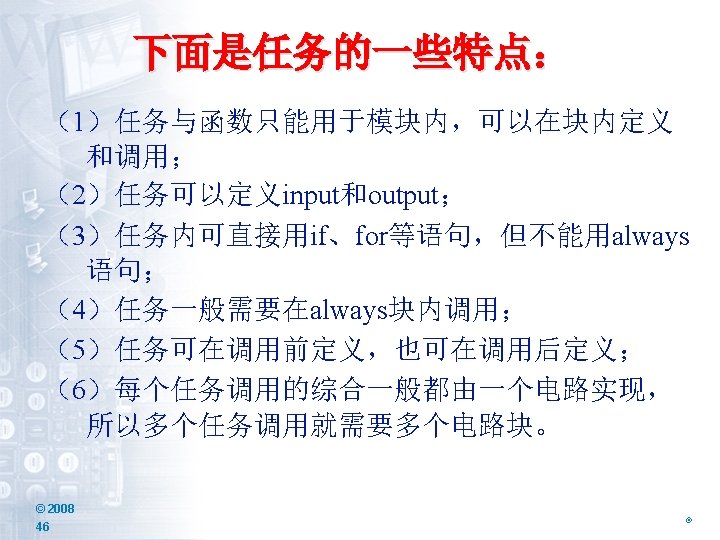

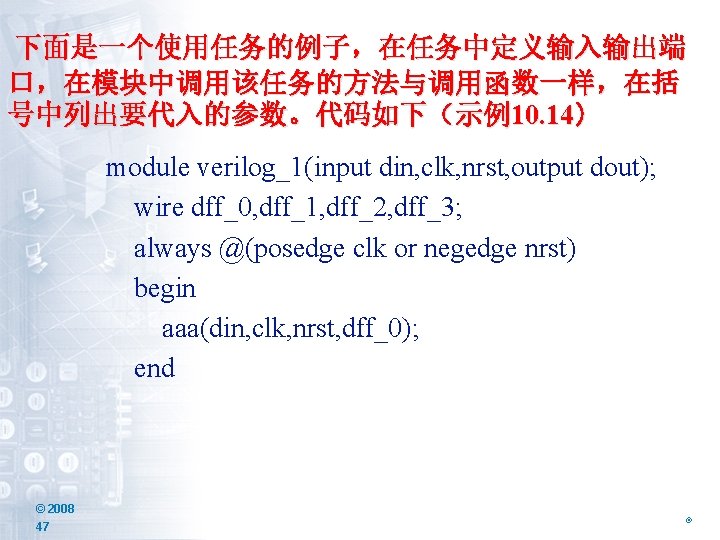

下面是一个使用任务的例子,在任务中定义输入输出端 口,在模块中调用该任务的方法与调用函数一样,在括 号中列出要代入的参数。代码如下(示例10. 14) module verilog_1(input din, clk, nrst, output dout); wire dff_0, dff_1, dff_2, dff_3; always @(posedge clk or negedge nrst) begin aaa(din, clk, nrst, dff_0); end © 2008 47 ®

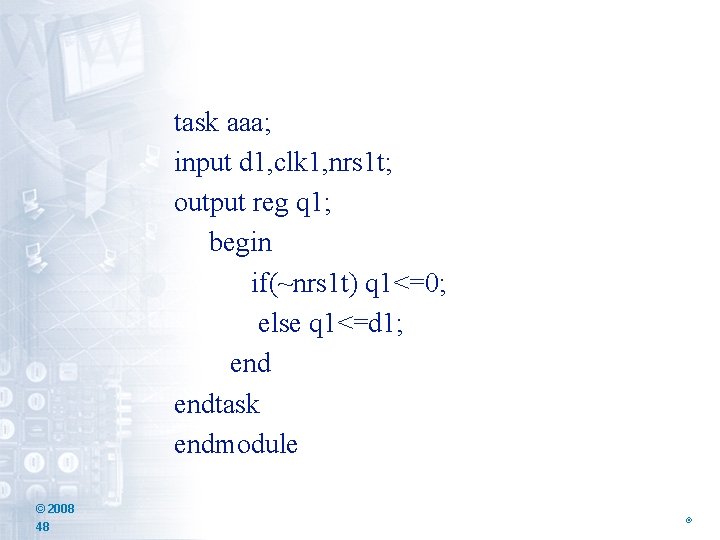

task aaa; input d 1, clk 1, nrs 1 t; output reg q 1; begin if(~nrs 1 t) q 1<=0; else q 1<=d 1; endtask endmodule © 2008 48 ®

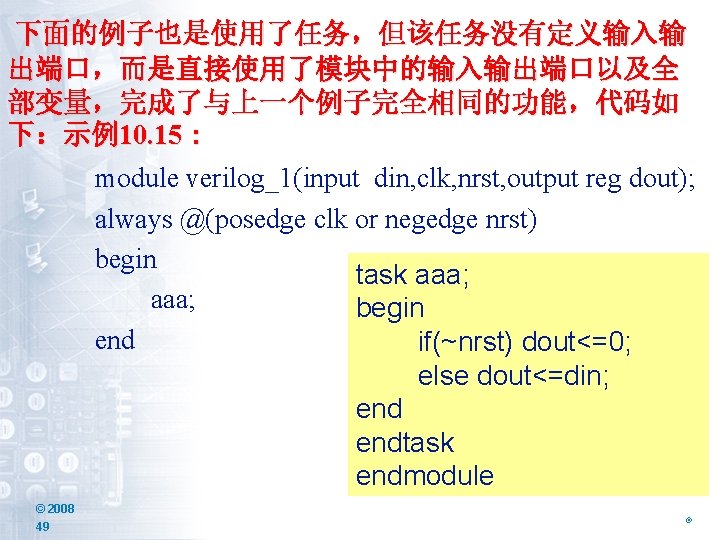

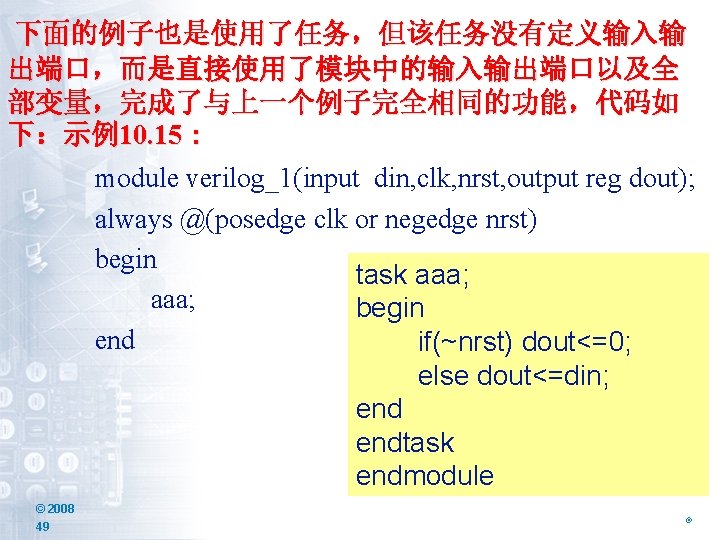

下面的例子也是使用了任务,但该任务没有定义输入输 出端口,而是直接使用了模块中的输入输出端口以及全 部变量,完成了与上一个例子完全相同的功能,代码如 下:示例10. 15: module verilog_1(input din, clk, nrst, output reg dout); always @(posedge clk or negedge nrst) begin task aaa; begin end if(~nrst) dout<=0; else dout<=din; endtask endmodule © 2008 49 ®