1 Sampling chip ps TDC02 presentation JeanFrancois Genat

- Slides: 16

1 Sampling chip ps. TDC_02 presentation Jean-Francois Genat – Herve Grabas Mary Heinz – Eric Oberla 6/14/2021

2 ps. TDC_02 presentation 6/14/2021 Overall presentation : the principle

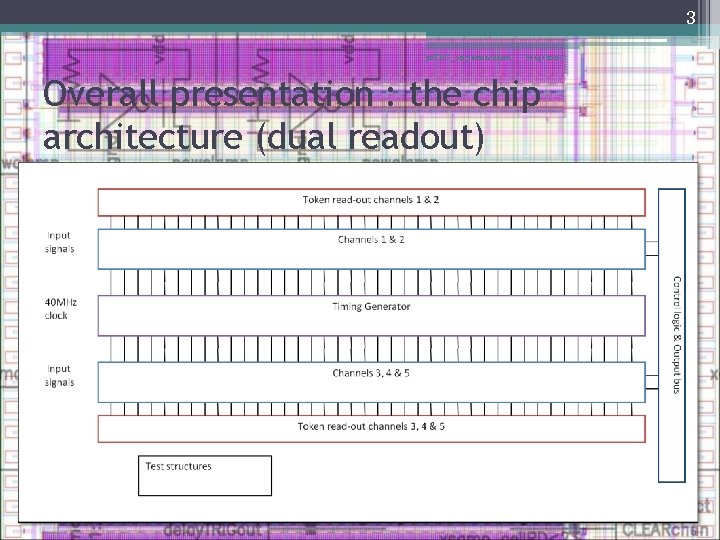

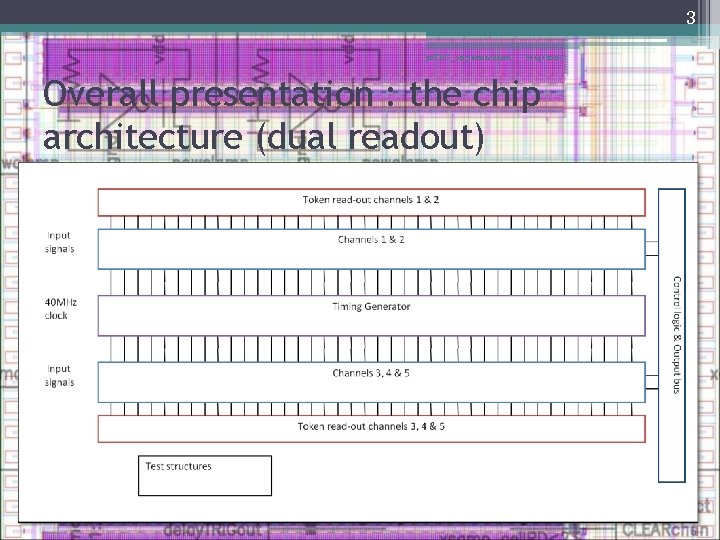

3 ps. TDC_02 presentation 6/14/2021 Overall presentation : the chip architecture (dual readout)

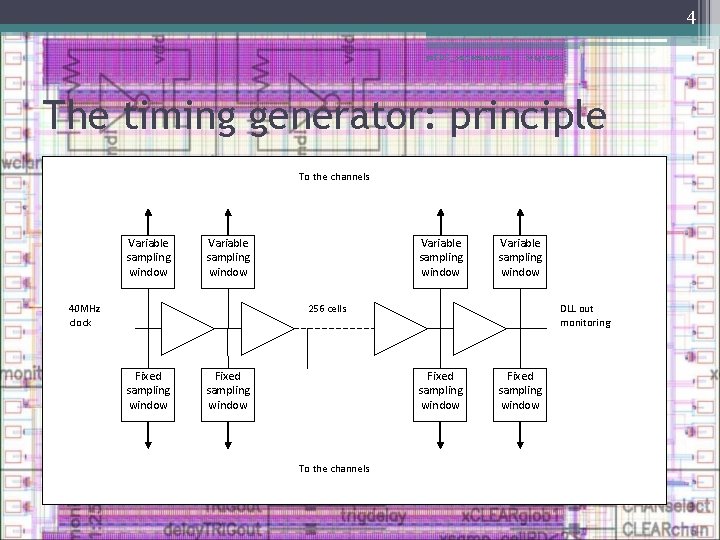

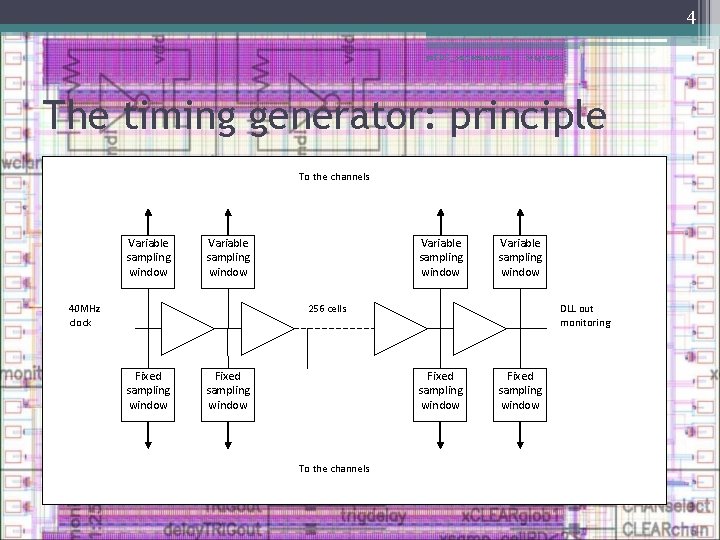

4 ps. TDC_02 presentation 6/14/2021 The timing generator: principle To the channels Variable sampling window 256 cells 40 MHz clock Fixed sampling window DLL out monitoring Fixed sampling window To the channels Fixed sampling window

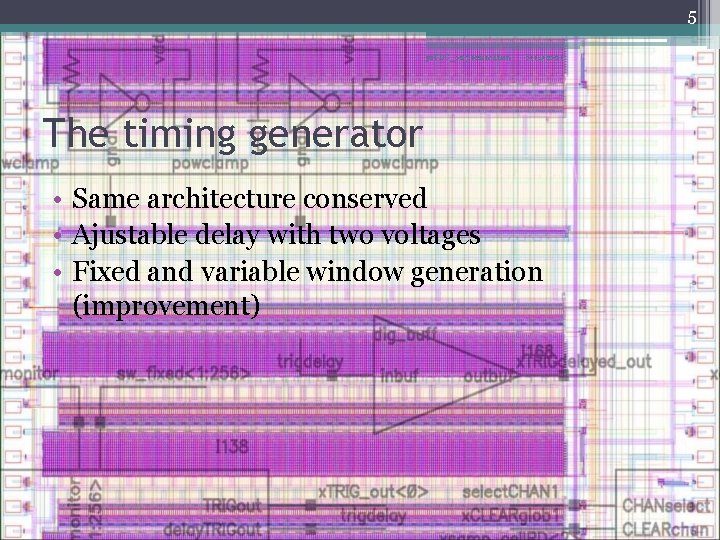

5 ps. TDC_02 presentation 6/14/2021 The timing generator • Same architecture conserved • Ajustable delay with two voltages • Fixed and variable window generation (improvement)

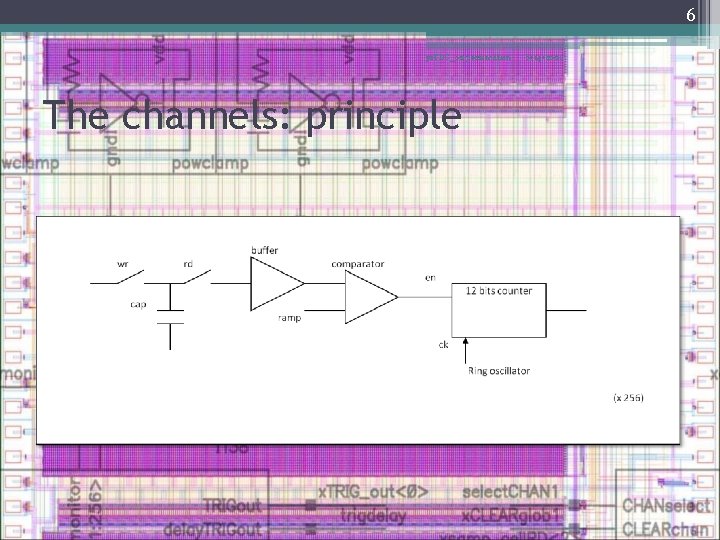

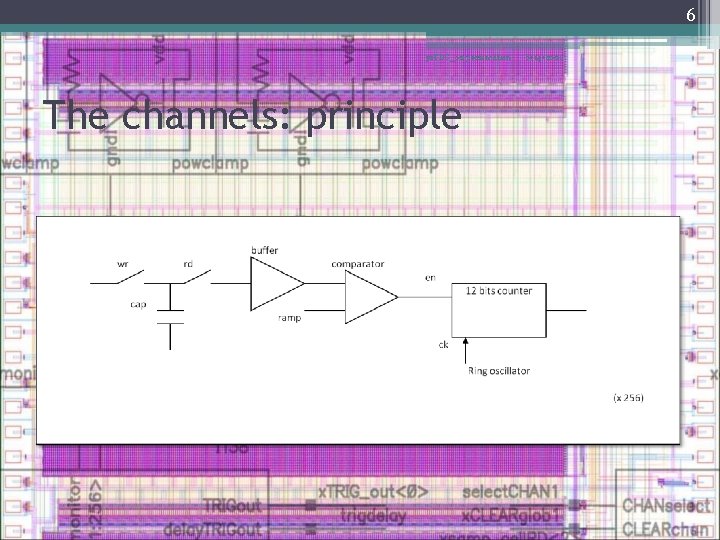

6 ps. TDC_02 presentation The channels: principle 6/14/2021

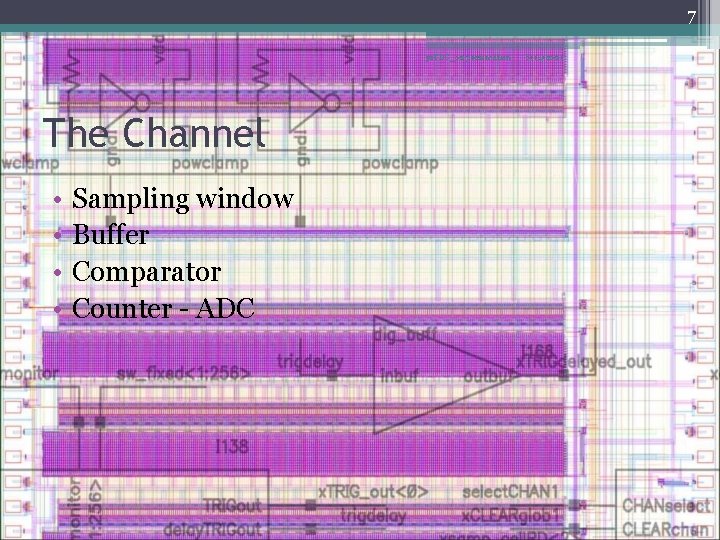

7 ps. TDC_02 presentation The Channel • • Sampling window Buffer Comparator Counter - ADC 6/14/2021

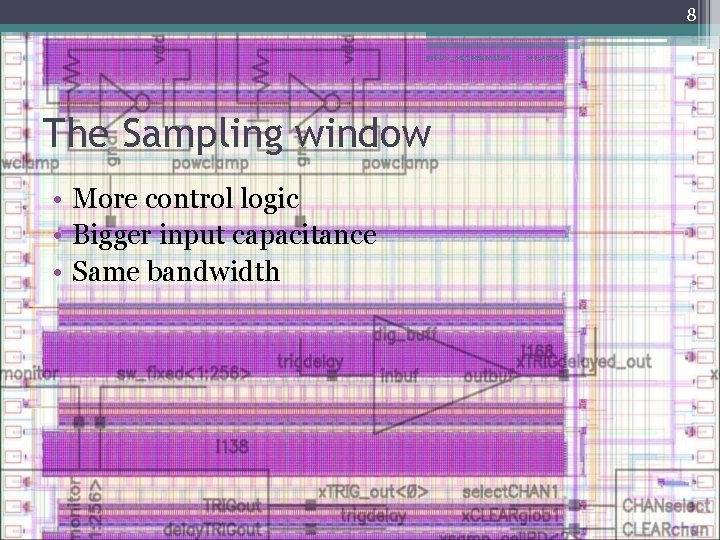

8 ps. TDC_02 presentation The Sampling window • More control logic • Bigger input capacitance • Same bandwidth 6/14/2021

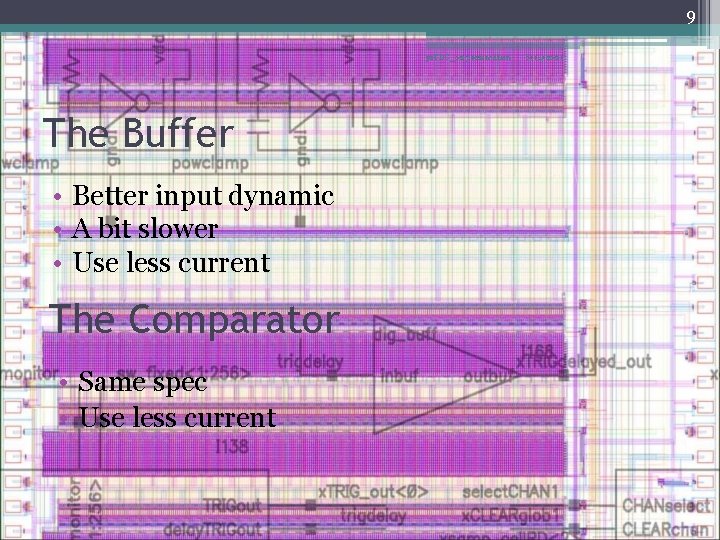

9 ps. TDC_02 presentation The Buffer • Better input dynamic • A bit slower • Use less current The Comparator • Same spec • Use less current 6/14/2021

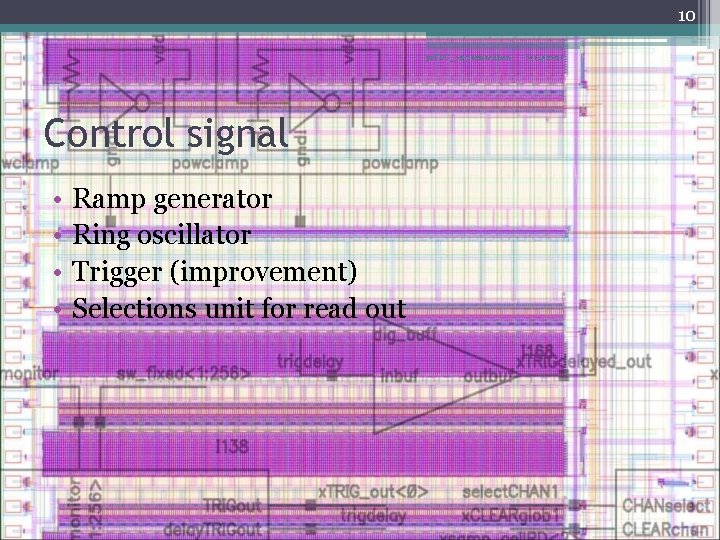

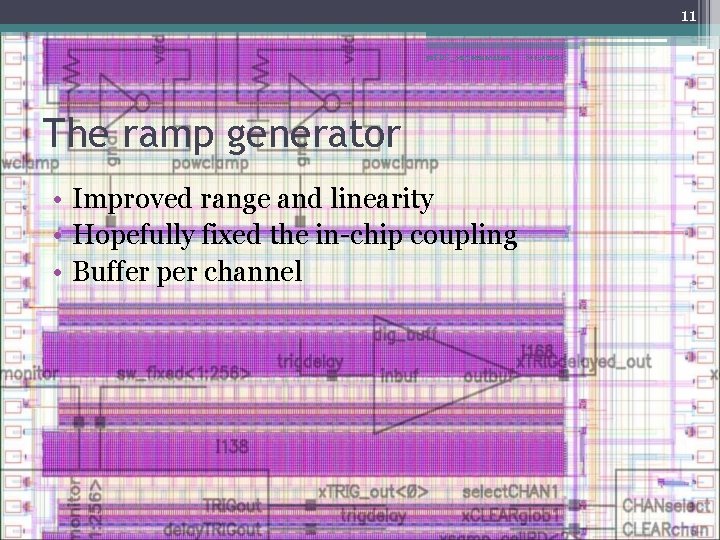

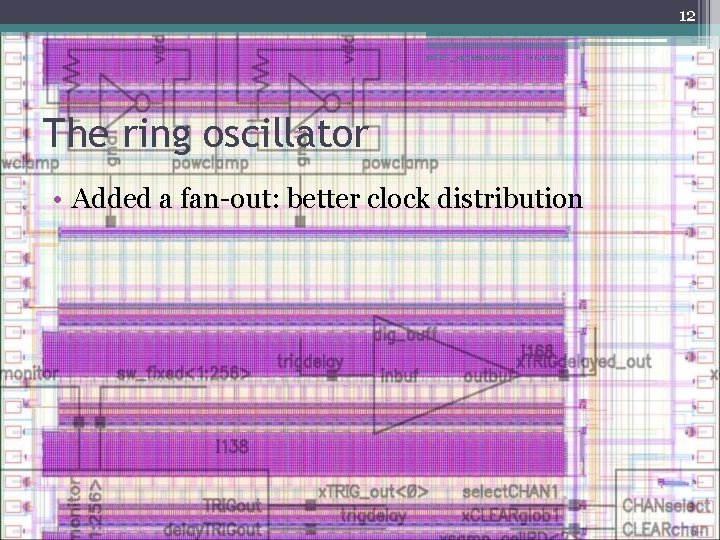

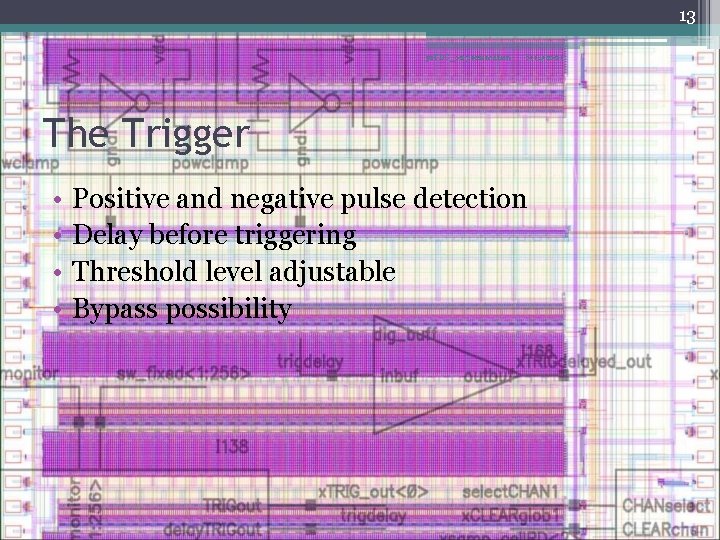

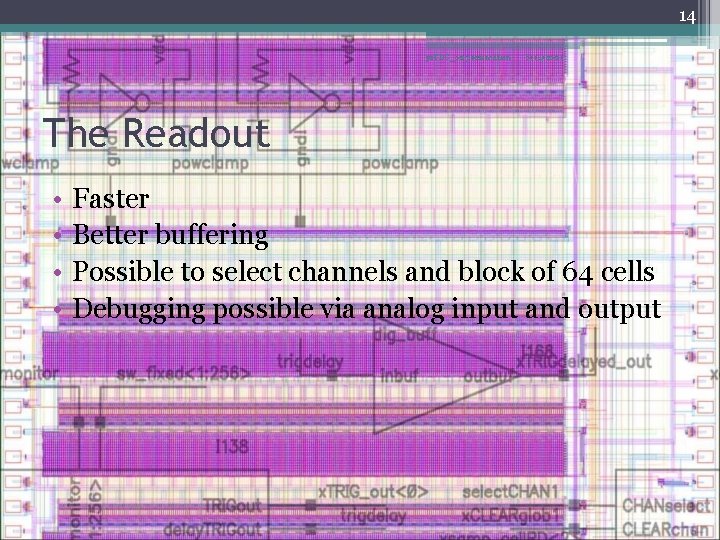

10 ps. TDC_02 presentation Control signal • • Ramp generator Ring oscillator Trigger (improvement) Selections unit for read out 6/14/2021

11 ps. TDC_02 presentation The ramp generator • Improved range and linearity • Hopefully fixed the in-chip coupling • Buffer per channel 6/14/2021

12 ps. TDC_02 presentation 6/14/2021 The ring oscillator • Added a fan-out: better clock distribution

13 ps. TDC_02 presentation 6/14/2021 The Trigger • • Positive and negative pulse detection Delay before triggering Threshold level adjustable Bypass possibility

14 ps. TDC_02 presentation 6/14/2021 The Readout • • Faster Better buffering Possible to select channels and block of 64 cells Debugging possible via analog input and output

15 ps. TDC_02 presentation 6/14/2021 Debugging • • • Fifth channel for sampling window observation Test structure: comparator and buffer Option for channel analog monitoring Resistance test structure More monitoring: ring oscillator, DLLout, ramp More bypassing

16 ps. TDC_02 presentation Chip design • Better layouting • Better ESD protection • Tools are well known Excpect the chip soon for tests 6/14/2021