1 m 3 Prototype Digital Hadron Calorimeter Collaborators

1 m 3 Prototype Digital Hadron Calorimeter Collaborators Argonne National Laboratory Boston University of Chicago Fermilab University of Texas at Arlington www. hep. anl. gov/repond/RPC_US. html

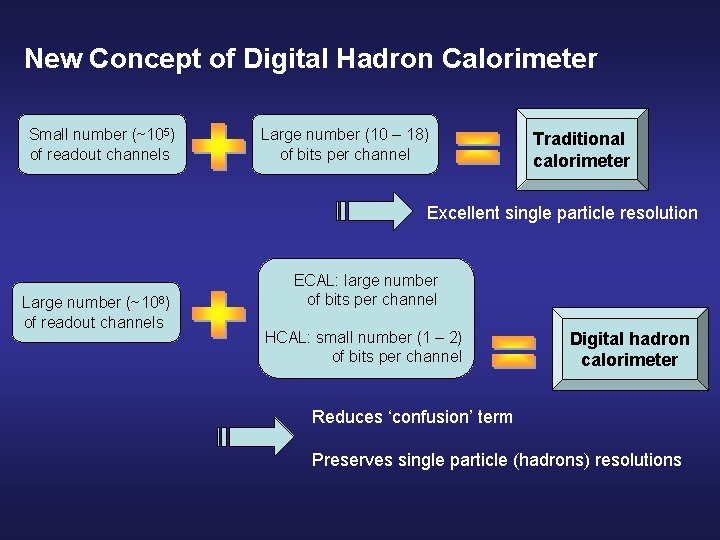

New Concept of Digital Hadron Calorimeter Small number (~105) of readout channels Large number (10 – 18) of bits per channel Traditional calorimeter Excellent single particle resolution Large number (~108) of readout channels ECAL: large number of bits per channel HCAL: small number (1 – 2) of bits per channel Digital hadron calorimeter Reduces ‘confusion’ term Preserves single particle (hadrons) resolutions

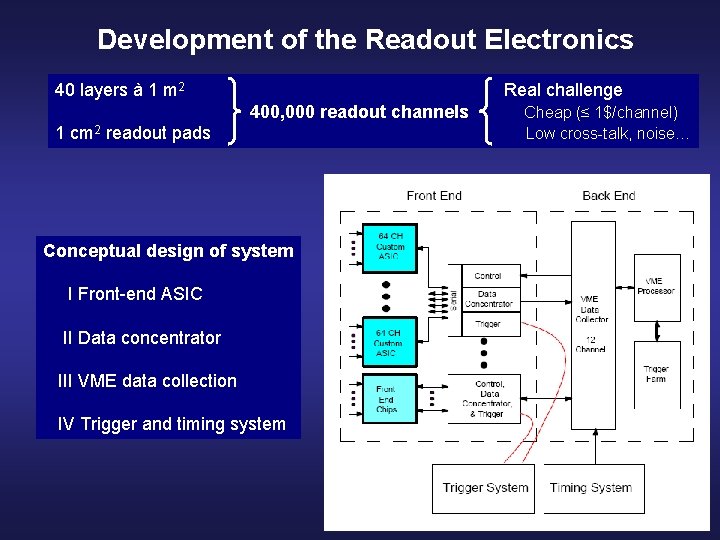

Development of the Readout Electronics 40 layers à 1 m 2 Real challenge 400, 000 readout channels 1 cm 2 readout pads Conceptual design of system I Front-end ASIC II Data concentrator III VME data collection IV Trigger and timing system Cheap (≤ 1$/channel) Low cross-talk, noise…

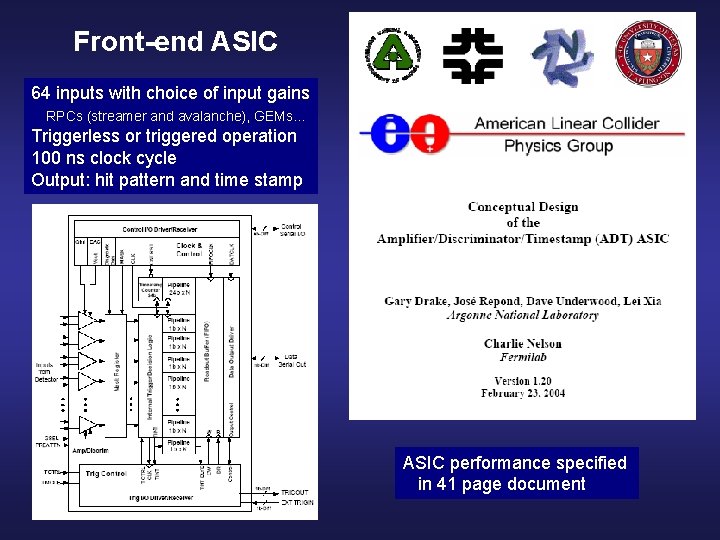

Front-end ASIC 64 inputs with choice of input gains RPCs (streamer and avalanche), GEMs… Triggerless or triggered operation 100 ns clock cycle Output: hit pattern and time stamp ASIC performance specified in 41 page document

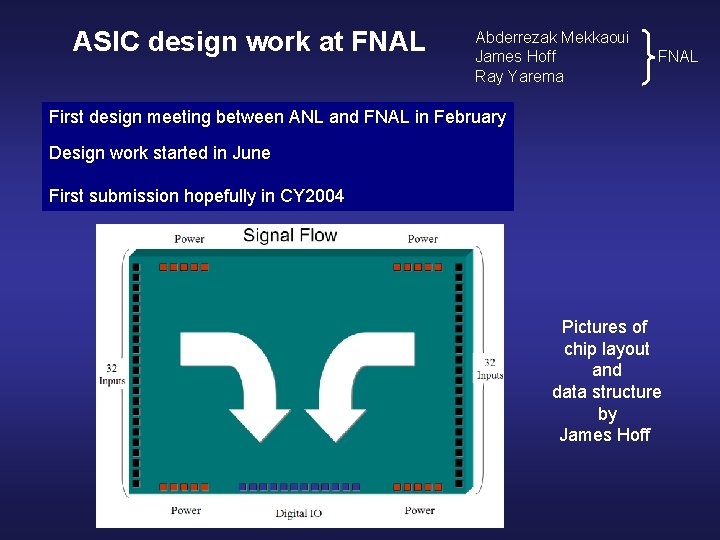

ASIC design work at FNAL Abderrezak Mekkaoui James Hoff Ray Yarema FNAL First design meeting between ANL and FNAL in February Design work started in June First submission hopefully in CY 2004 Pictures of chip layout and data structure by James Hoff

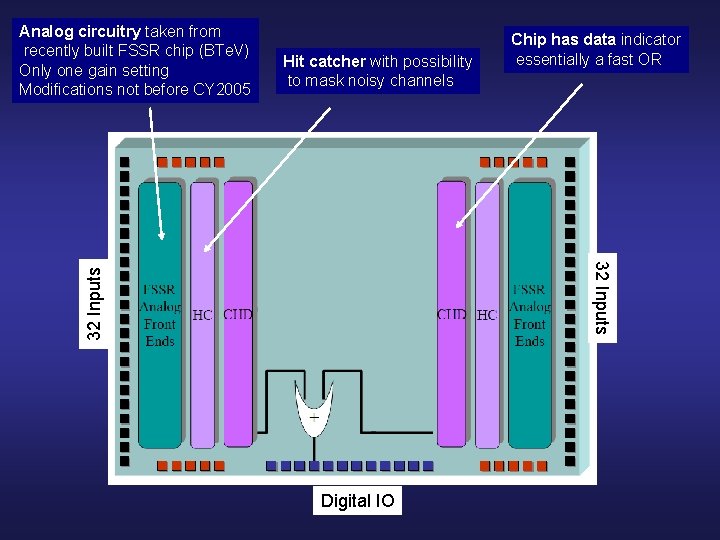

Hit catcher with possibility to mask noisy channels Chip has data indicator essentially a fast OR 32 Inputs Analog circuitry taken from recently built FSSR chip (BTe. V) Only one gain setting Modifications not before CY 2005 Digital IO

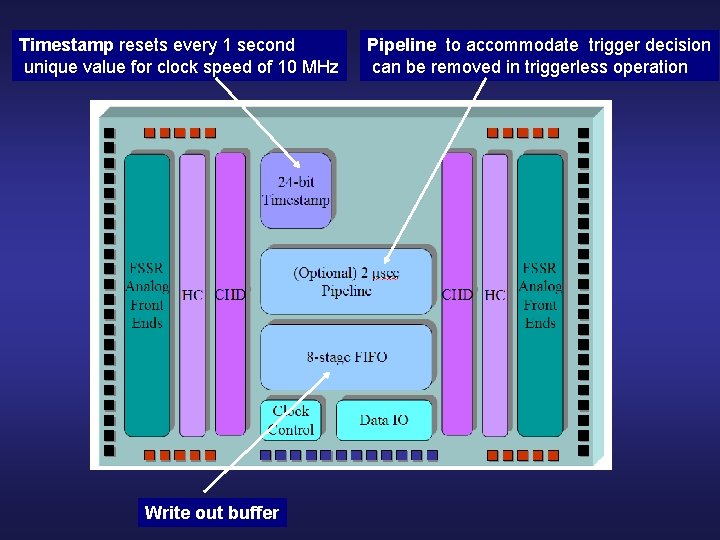

Timestamp resets every 1 second unique value for clock speed of 10 MHz Write out buffer Pipeline to accommodate trigger decision can be removed in triggerless operation

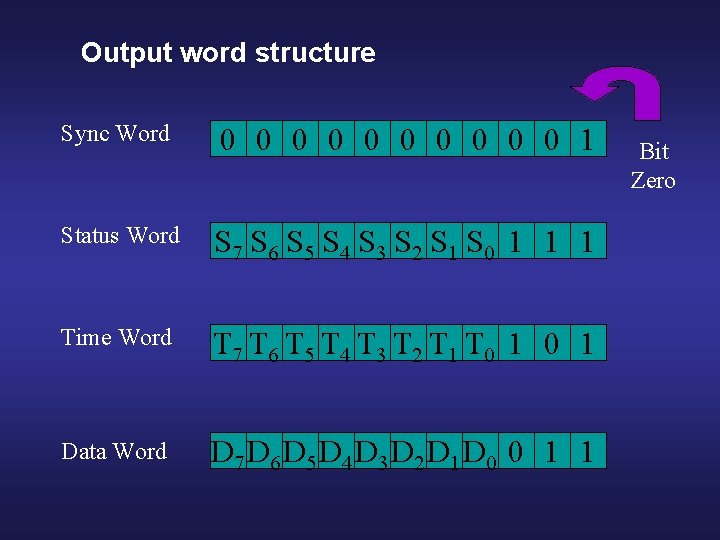

Output word structure Sync Word 0 0 0 0 0 1 Status Word S 7 S 6 S 5 S 4 S 3 S 2 S 1 S 0 1 1 1 Time Word T 7 T 6 T 5 T 4 T 3 T 2 T 1 T 0 1 Data Word D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 0 1 1 Bit Zero

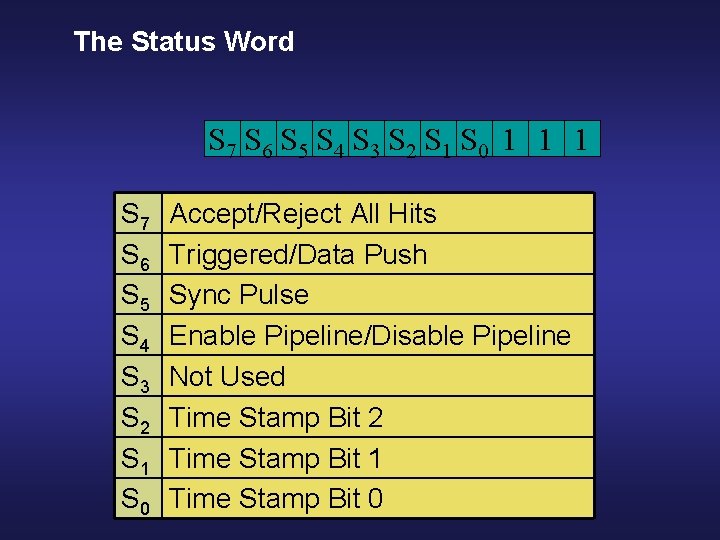

The Status Word S 7 S 6 S 5 S 4 S 3 S 2 S 1 S 0 1 1 1 S 7 S 6 S 5 S 4 S 3 S 2 S 1 S 0 Accept/Reject All Hits Triggered/Data Push Sync Pulse Enable Pipeline/Disable Pipeline Not Used Time Stamp Bit 2 Time Stamp Bit 1 Time Stamp Bit 0

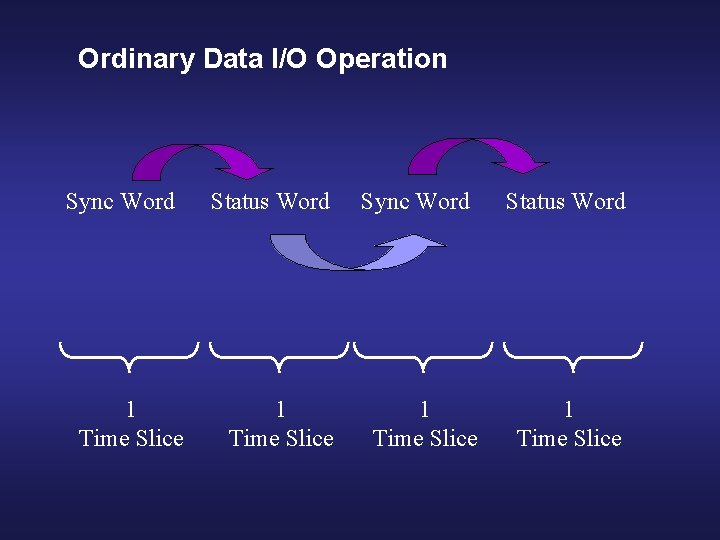

Ordinary Data I/O Operation Sync Word 1 Time Slice Status Word 1 Time Slice

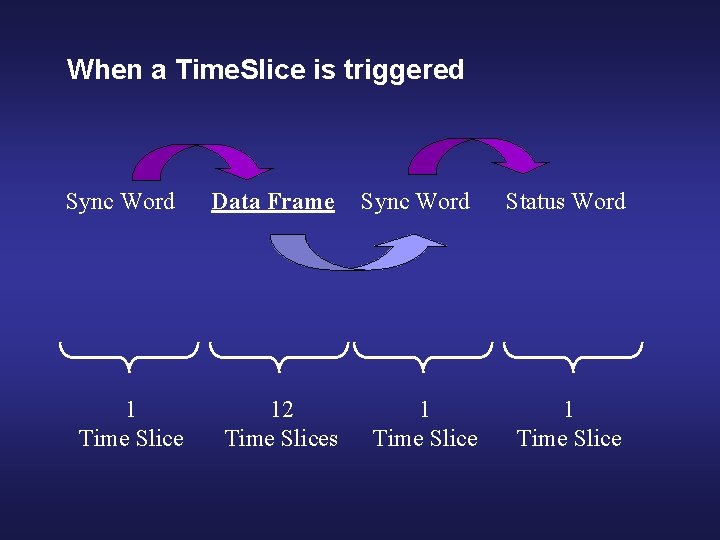

When a Time. Slice is triggered Sync Word 1 Time Slice Data Frame 12 Time Slices Sync Word 1 Time Slice Status Word 1 Time Slice

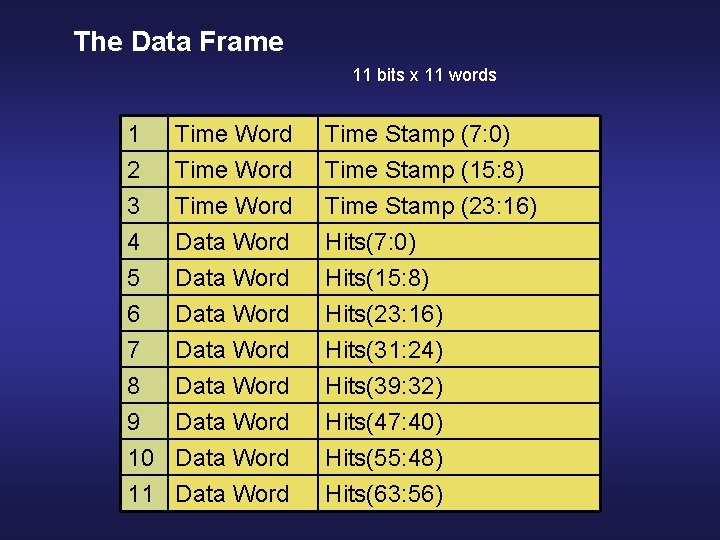

The Data Frame 11 bits x 11 words 1 2 3 4 Time Word Data Word Time Stamp (7: 0) Time Stamp (15: 8) Time Stamp (23: 16) Hits(7: 0) 5 6 7 8 9 10 11 Data Word Data Word Hits(15: 8) Hits(23: 16) Hits(31: 24) Hits(39: 32) Hits(47: 40) Hits(55: 48) Hits(63: 56)

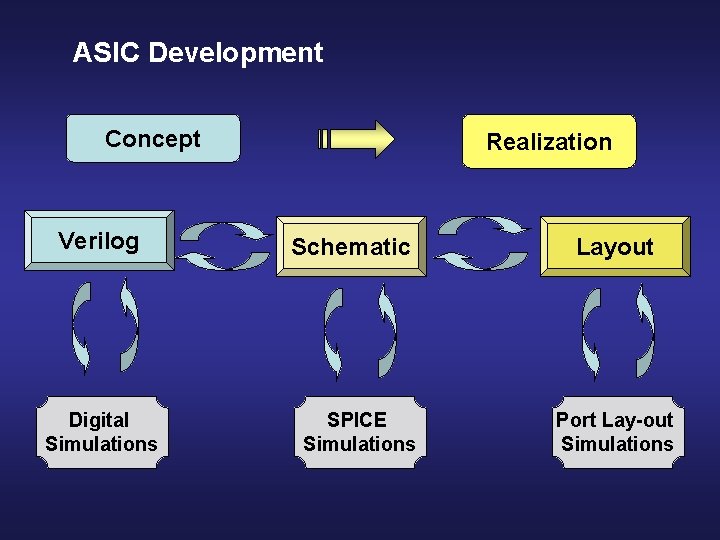

ASIC Development Concept Verilog Digital Simulations Realization Schematic SPICE Simulations Layout Port Lay-out Simulations

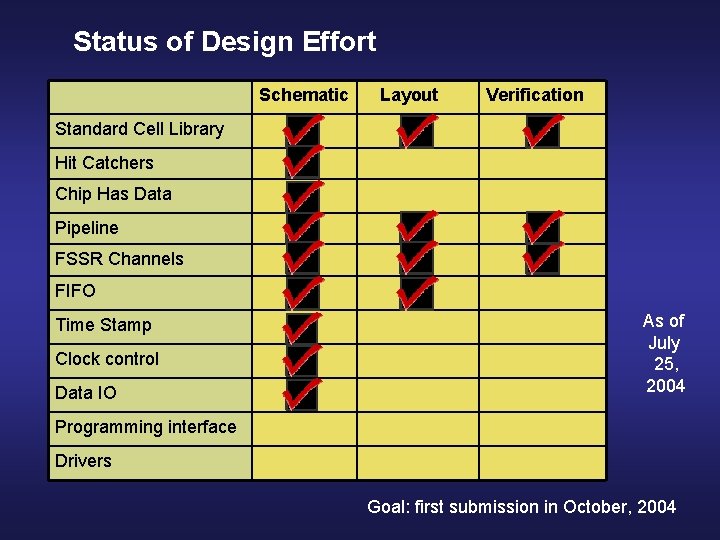

Status of Design Effort Schematic Layout Verification Standard Cell Library Hit Catchers Chip Has Data Pipeline FSSR Channels FIFO Time Stamp Clock control Data IO As of July 25, 2004 Programming interface Drivers Goal: first submission in October, 2004

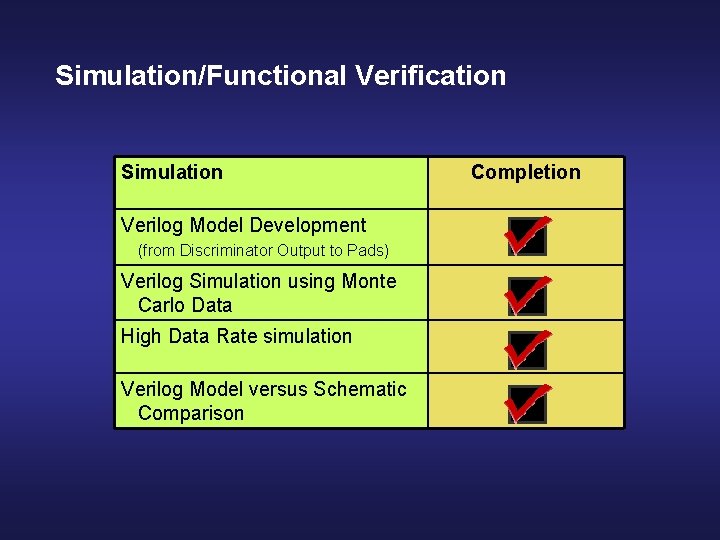

Simulation/Functional Verification Simulation Verilog Model Development (from Discriminator Output to Pads) Verilog Simulation using Monte Carlo Data High Data Rate simulation Verilog Model versus Schematic Comparison Completion

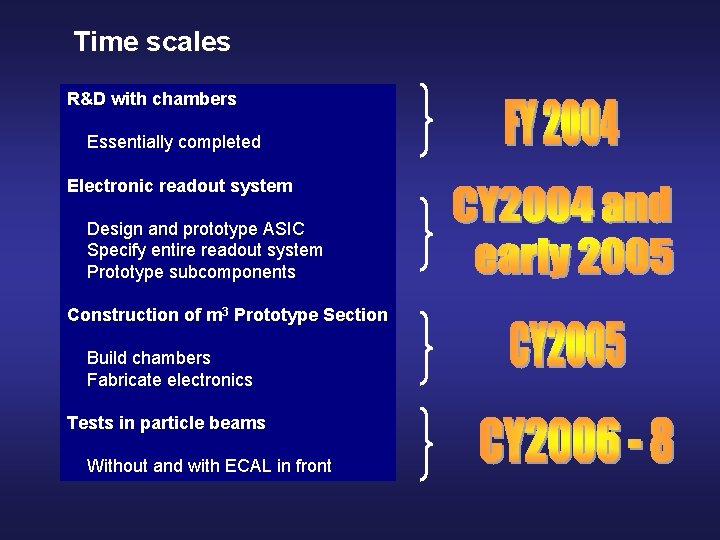

Time scales R&D with chambers Essentially completed Electronic readout system Design and prototype ASIC Specify entire readout system Prototype subcomponents Construction of m 3 Prototype Section Build chambers Fabricate electronics Tests in particle beams Without and with ECAL in front

- Slides: 16