1 Logic Circuits Registers and Counters 2 Registers

- Slides: 42

1

ﻣﺪﺍﺭ ﻣﻨﻄﻘی Logic Circuits Registers and Counters 2

Registers and Counters �Circuits that include flip‐flops are usually classified by the function they perform rather than by the name of the sequential circuit. �A register is a group of flip‐flops, each one of which shares a common clock and is capable of storing one bit of information. �An n ‐bit register consists of a group of n flip‐flops capable of storing n bits of binary information. �In addition to the flip‐flops, a register may have combinational gates that control its functionality. �A counter is essentially a register that goes through a predetermined sequence of binary states. �The gates in the counter are connected in such a way as to produce the prescribed sequence of states. 3

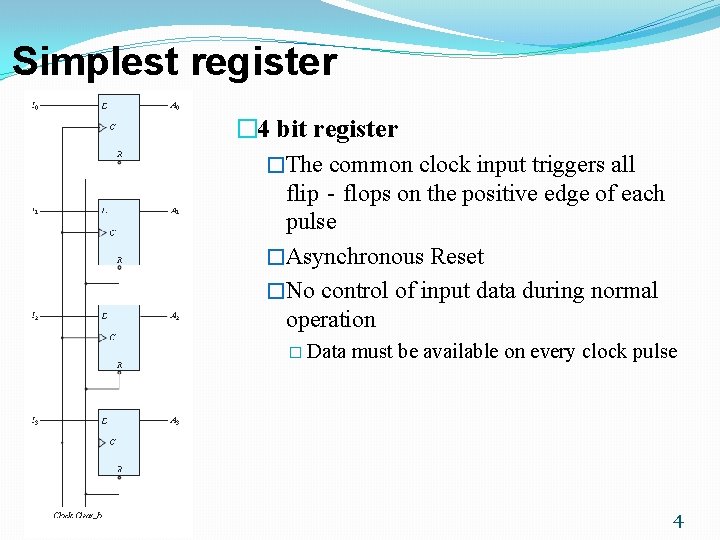

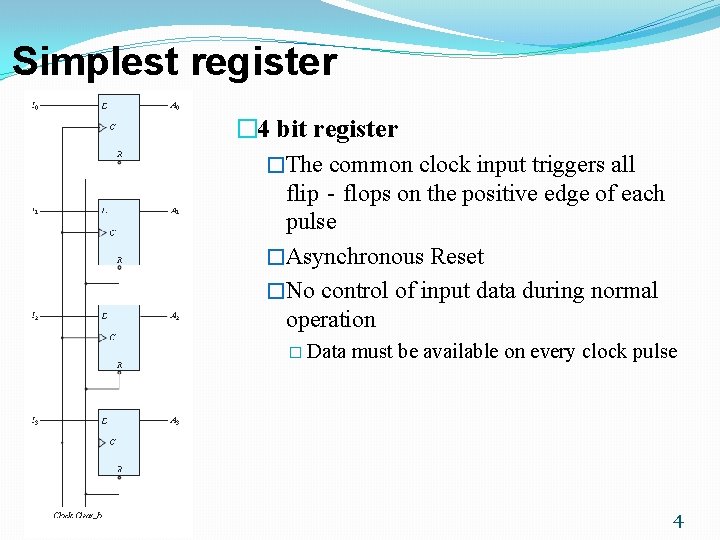

Simplest register � 4 bit register �The common clock input triggers all flip‐flops on the positive edge of each pulse �Asynchronous Reset �No control of input data during normal operation � Data must be available on every clock pulse 4

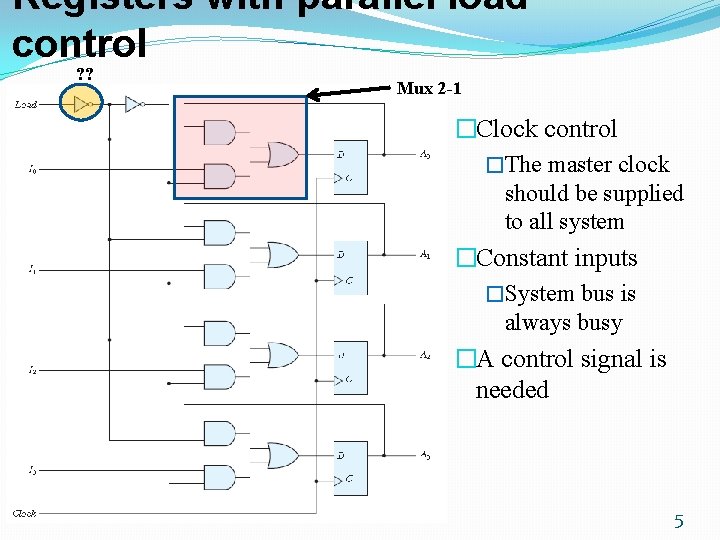

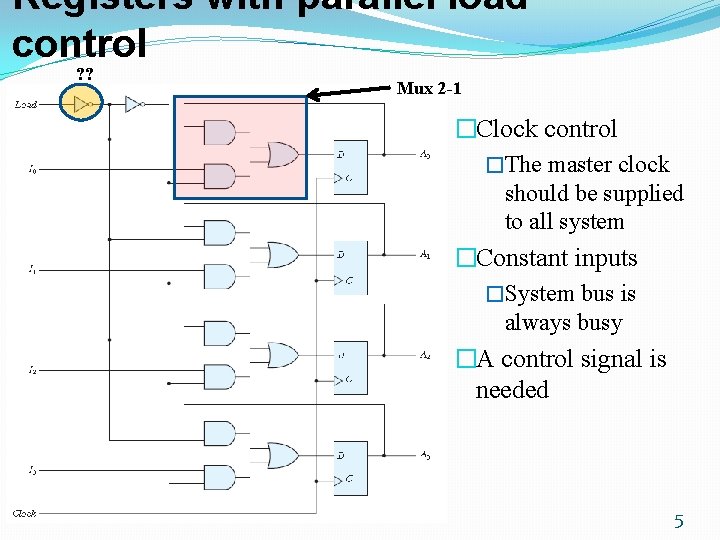

Registers with parallel load control ? ? Mux 2 -1 �Clock control �The master clock should be supplied to all system �Constant inputs �System bus is always busy �A control signal is needed 5

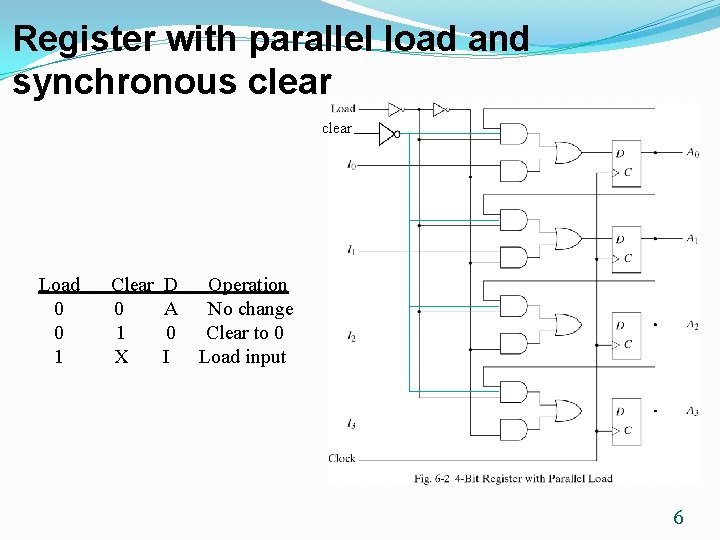

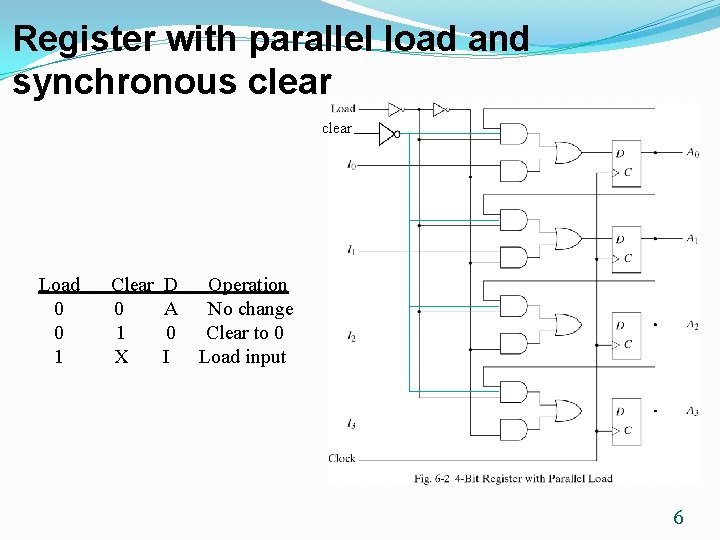

Register with parallel load and synchronous clear Load 0 0 1 Clear 0 1 X D A 0 I Operation No change Clear to 0 Load input 6

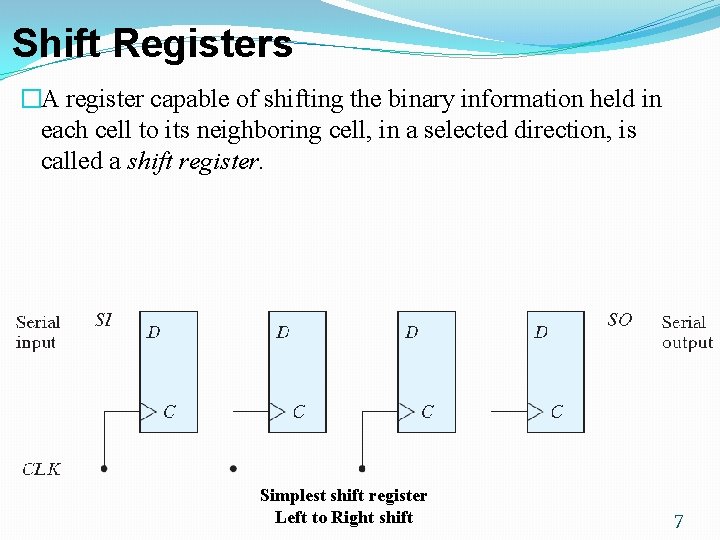

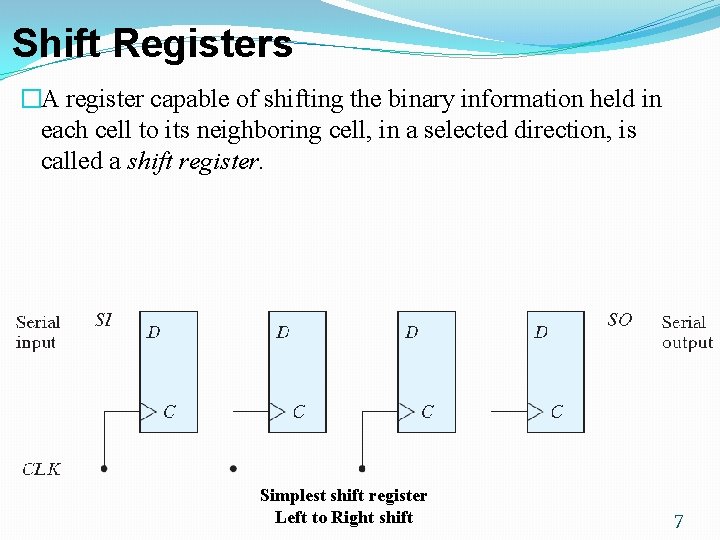

Shift Registers �A register capable of shifting the binary information held in each cell to its neighboring cell, in a selected direction, is called a shift register. Simplest shift register Left to Right shift 7

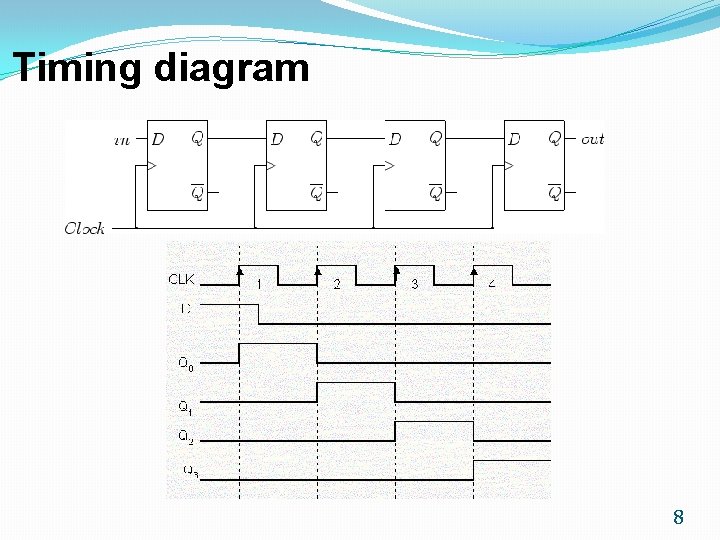

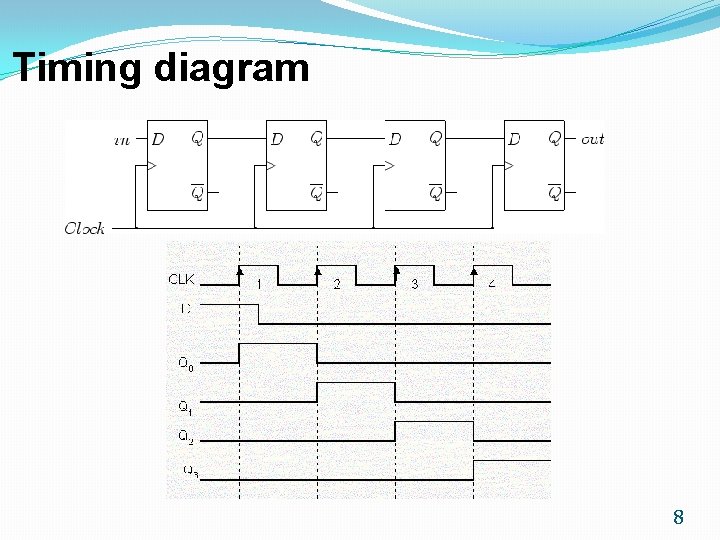

Timing diagram 8

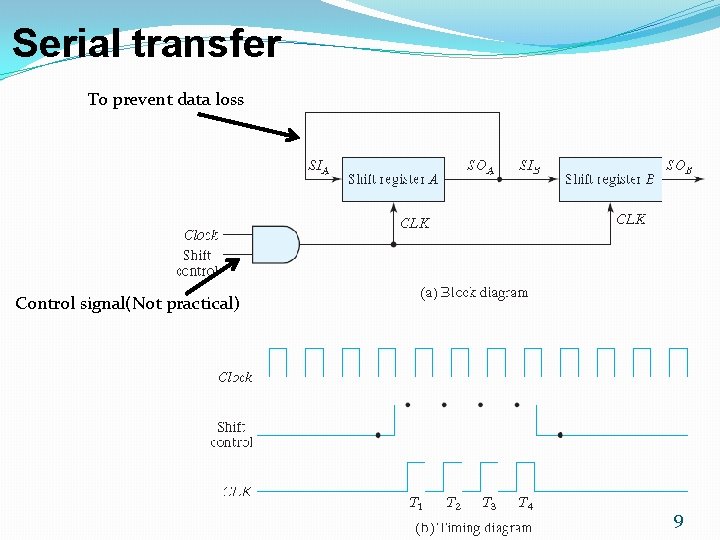

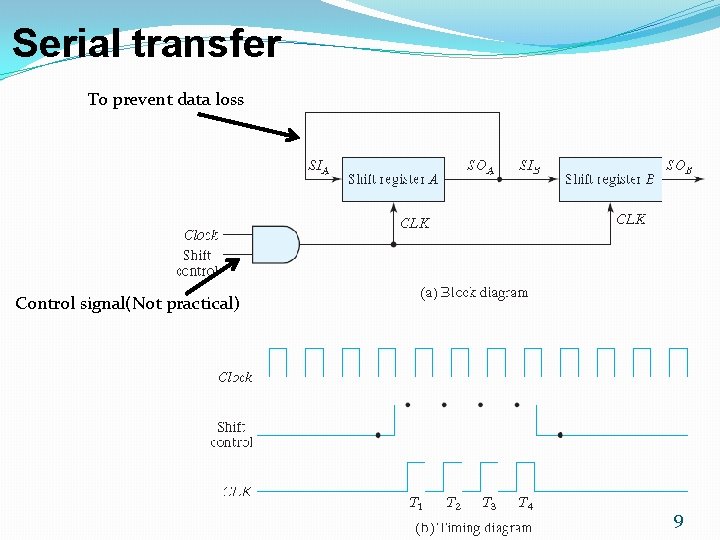

Serial transfer To prevent data loss Control signal(Not practical) 9

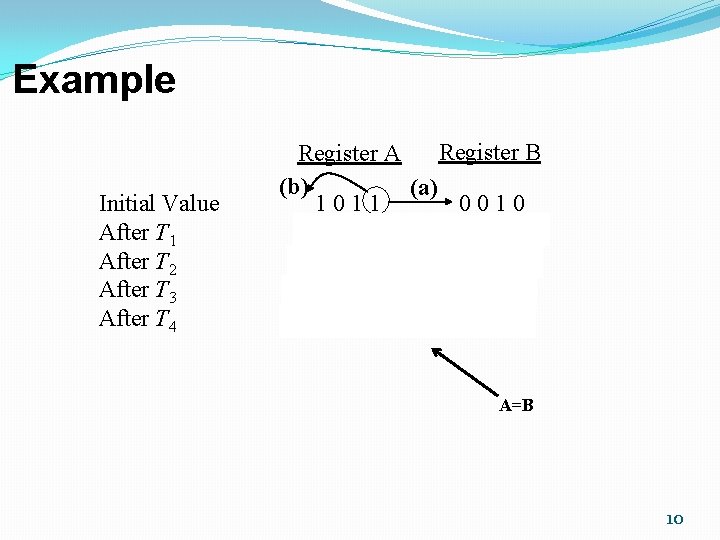

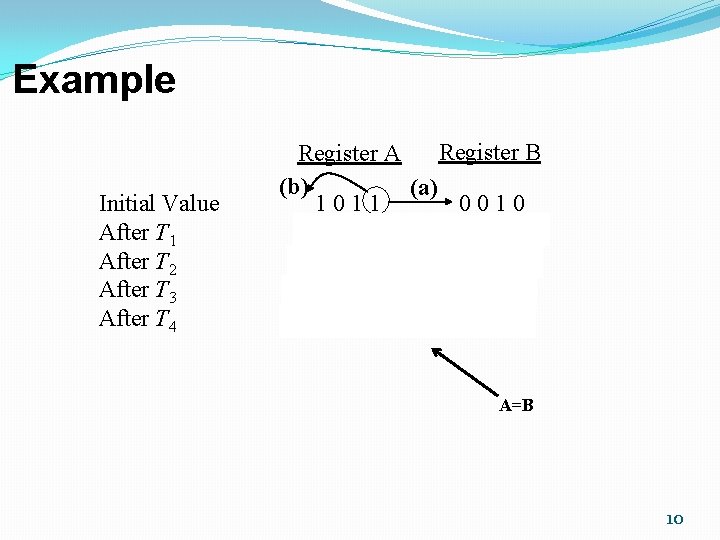

Example Initial Value After T 1 After T 2 After T 3 After T 4 Register B Register A (b) (a) 1011 0010 1101 1001 1110 1100 0111 0110 1011 A=B 10

Serial V. s. Parallel �Serial �One bit at a time �Slower �Cheaper �Parallel �All bits at a time �Faster �Expensive �Data communication Serial, Economical �Data manipulation in the system Parallel, Faster 11

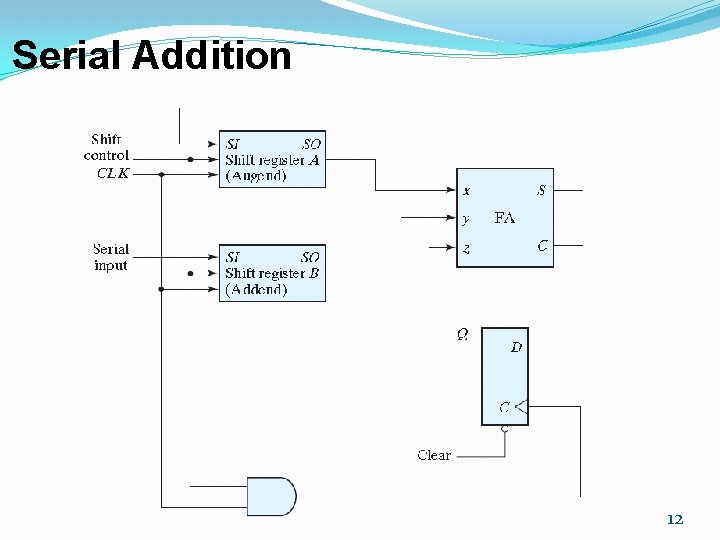

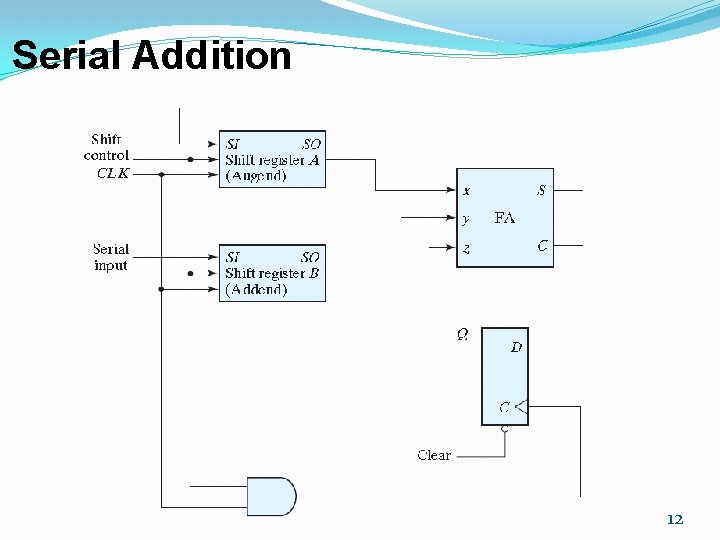

Serial Addition 12

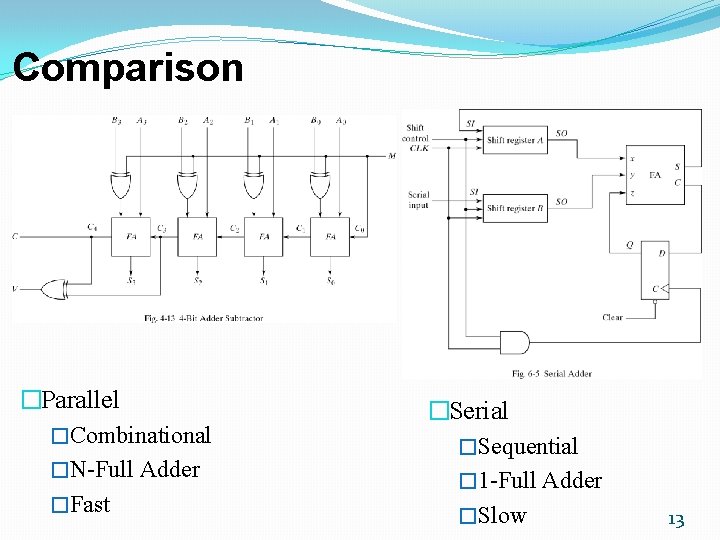

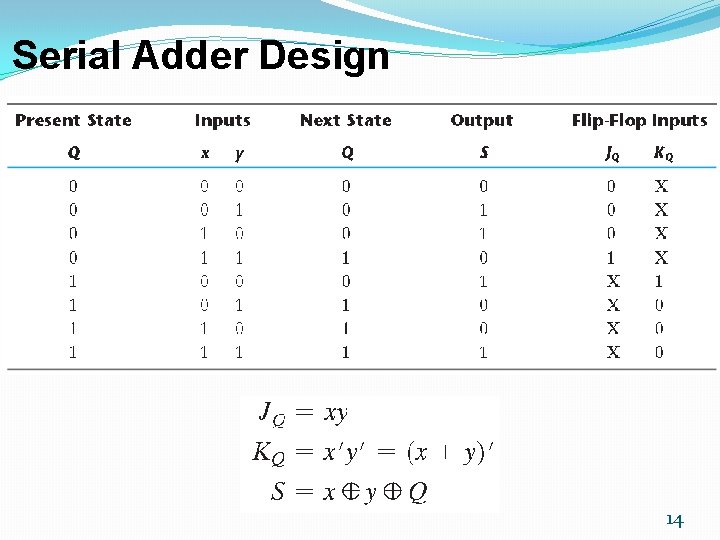

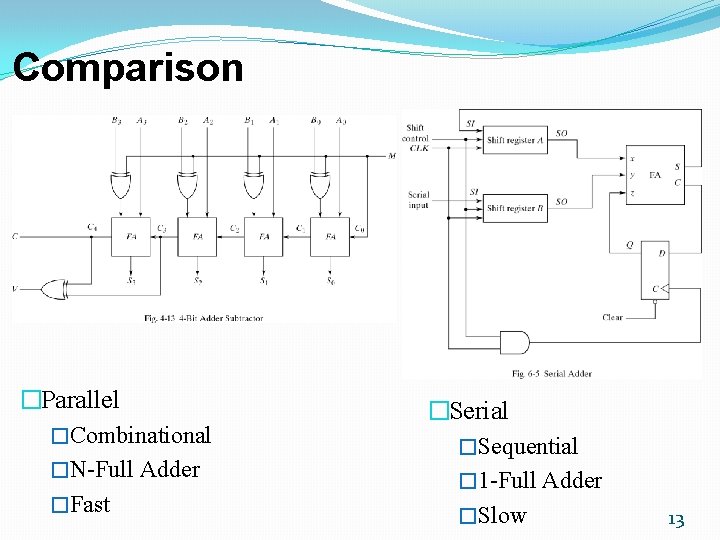

Comparison �Parallel �Combinational �N-Full Adder �Fast �Serial �Sequential � 1 -Full Adder �Slow 13

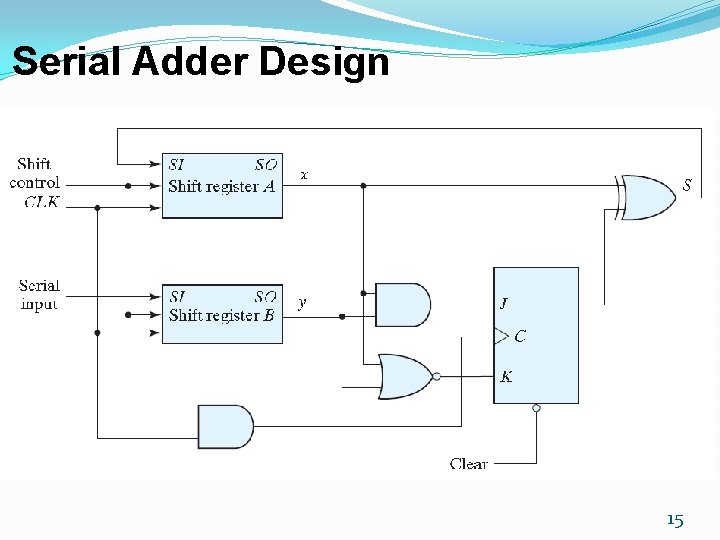

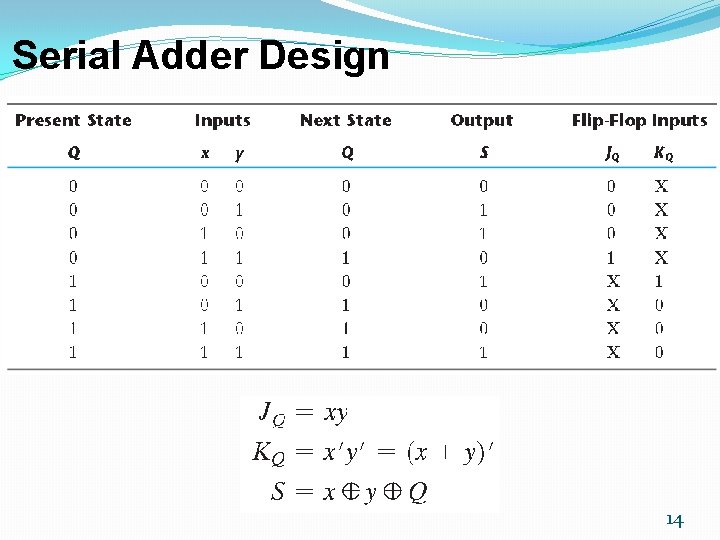

Serial Adder Design 14

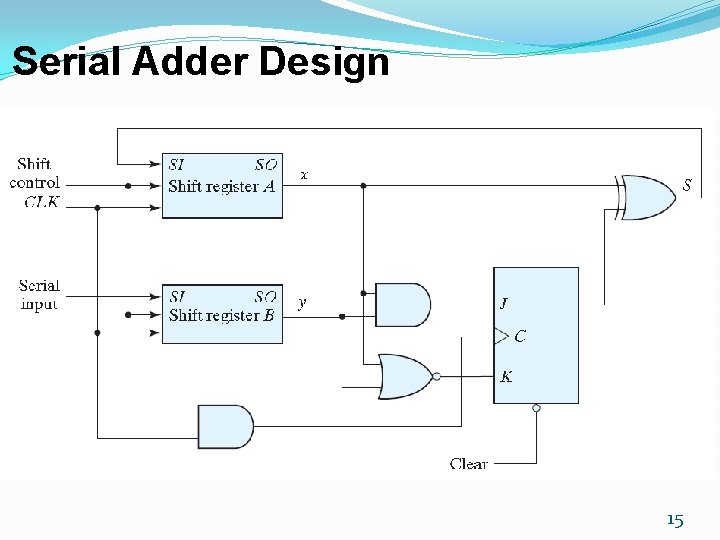

Serial Adder Design 15

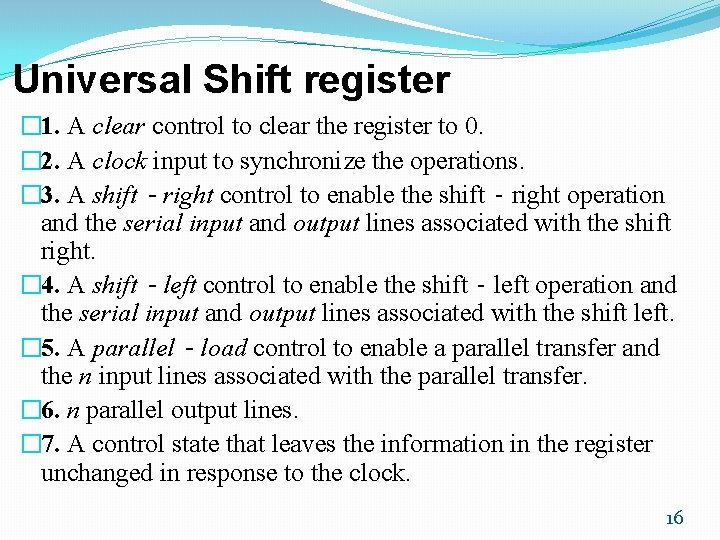

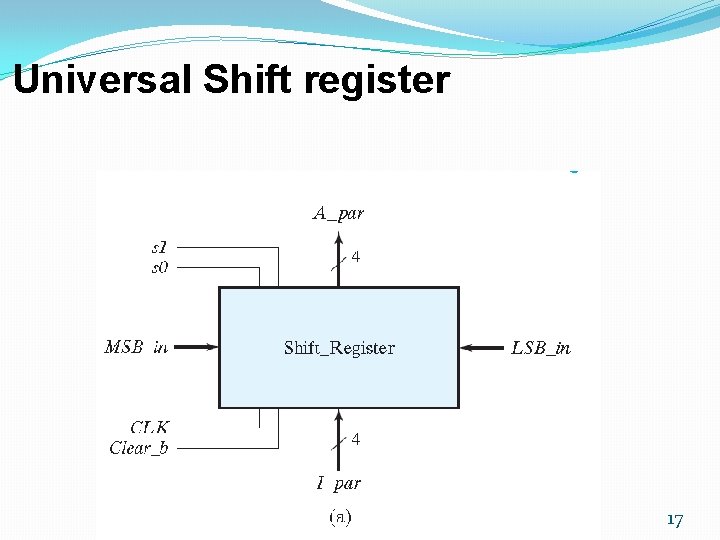

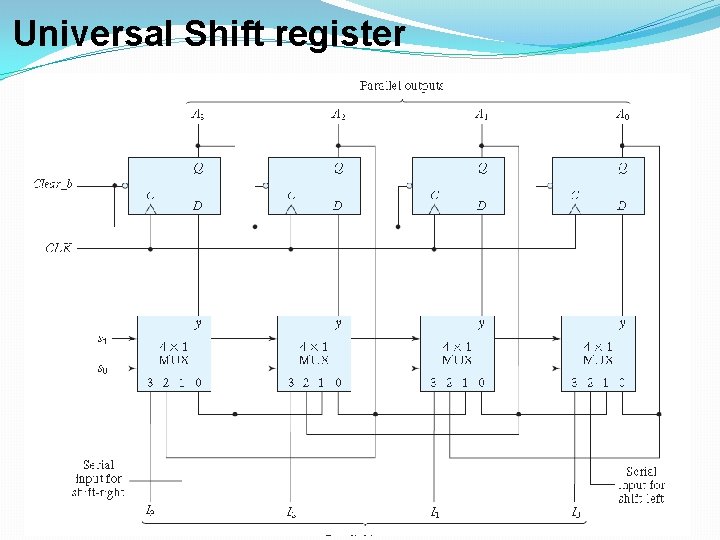

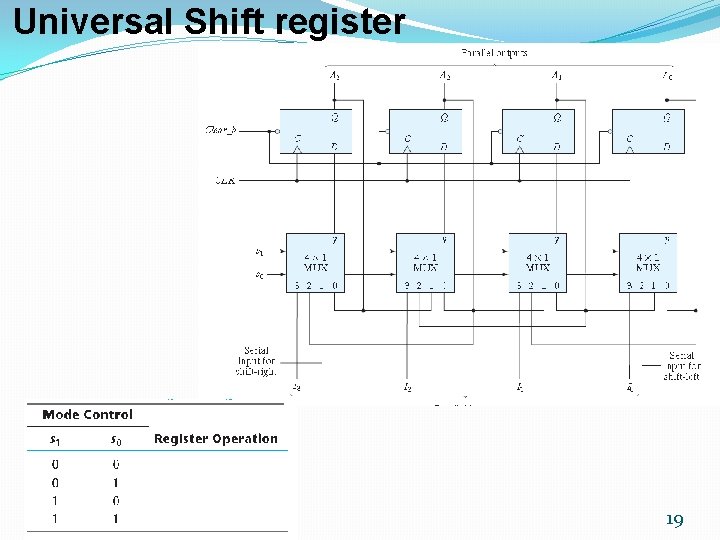

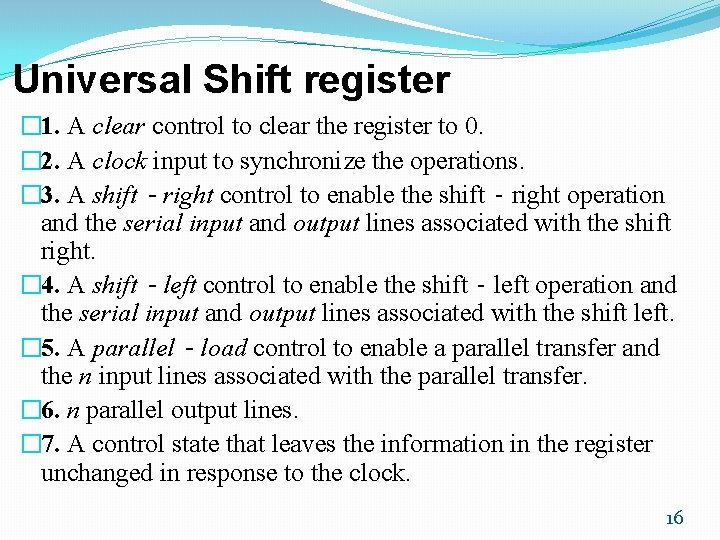

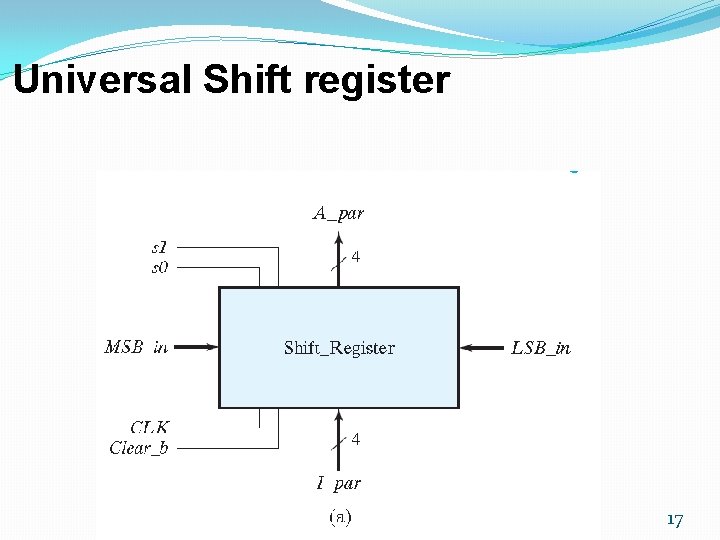

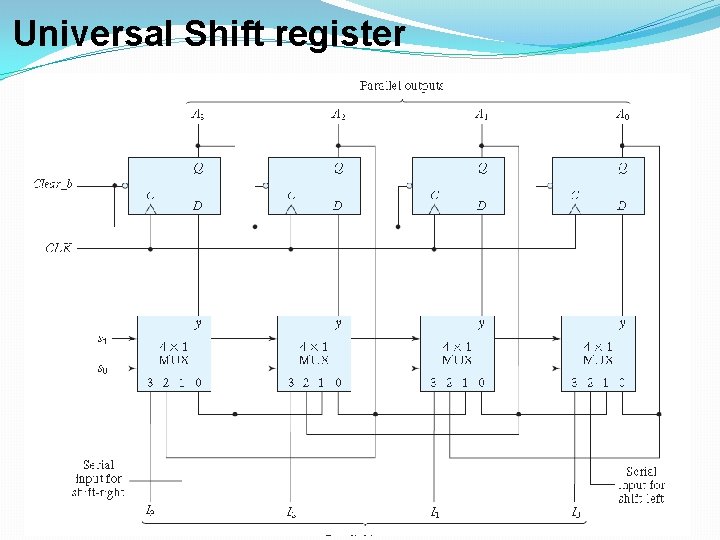

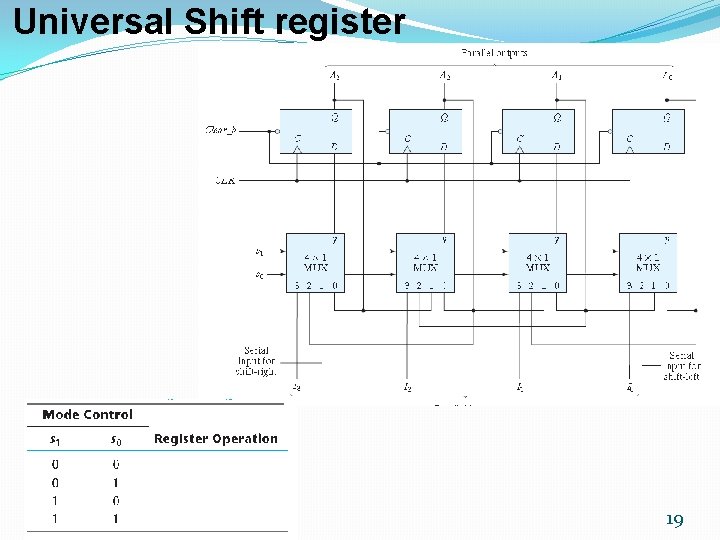

Universal Shift register � 1. A clear control to clear the register to 0. � 2. A clock input to synchronize the operations. � 3. A shift‐right control to enable the shift‐right operation and the serial input and output lines associated with the shift right. � 4. A shift‐left control to enable the shift‐left operation and the serial input and output lines associated with the shift left. � 5. A parallel‐load control to enable a parallel transfer and the n input lines associated with the parallel transfer. � 6. n parallel output lines. � 7. A control state that leaves the information in the register unchanged in response to the clock. 16

Universal Shift register 17

Universal Shift register 18

Universal Shift register 19

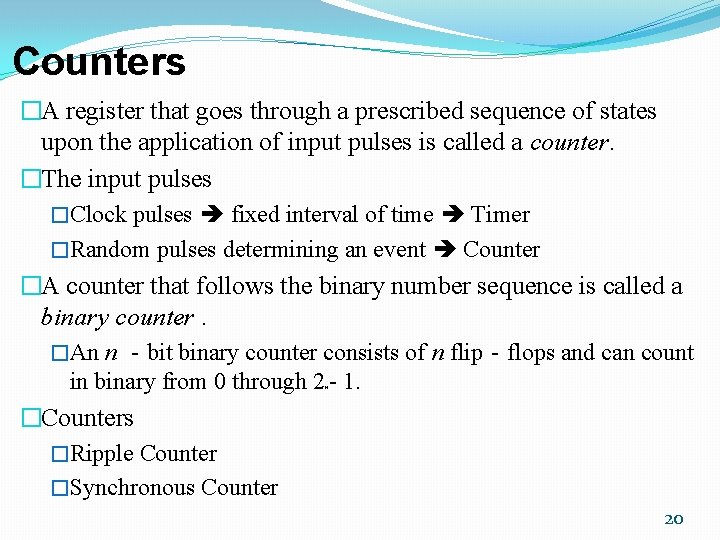

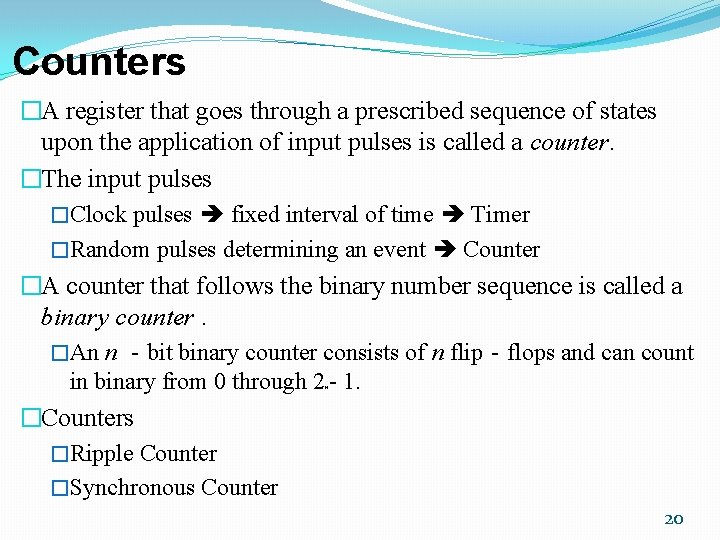

Counters �A register that goes through a prescribed sequence of states upon the application of input pulses is called a counter. �The input pulses �Clock pulses fixed interval of time Timer �Random pulses determining an event Counter �A counter that follows the binary number sequence is called a binary counter. �An n ‐bit binary counter consists of n flip‐flops and can count in binary from 0 through 2 - 1. �Counters �Ripple Counter �Synchronous Counter n 20

Ripple V. s. Synchronous Counter �Ripple counter �A flip‐flop output transition serves as a source for triggering other flip‐flops. In other words, the Clock input of some or all flip‐flops are triggered, not by the common clock pulses, but rather by the transition that occurs in other flip‐flop outputs. �Synchronous counter �the Clock inputs of all flip‐flops receive the common clock. 21

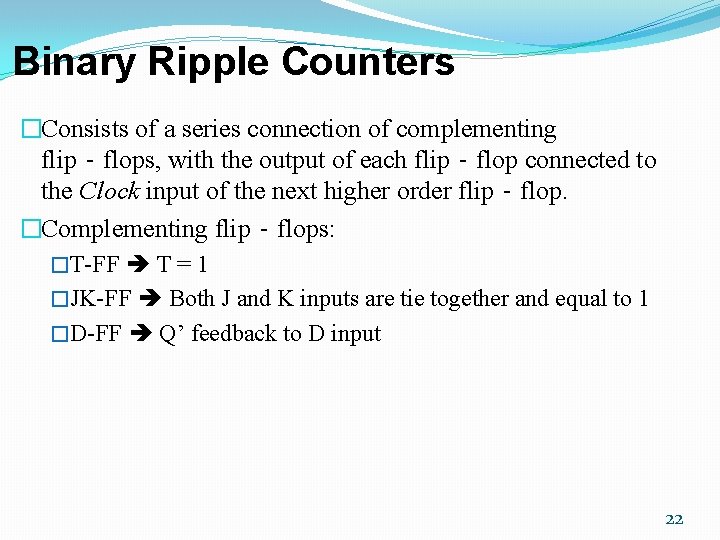

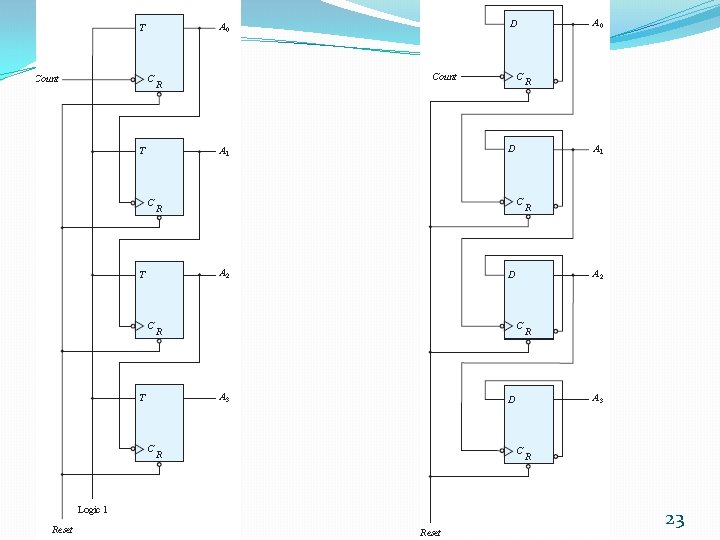

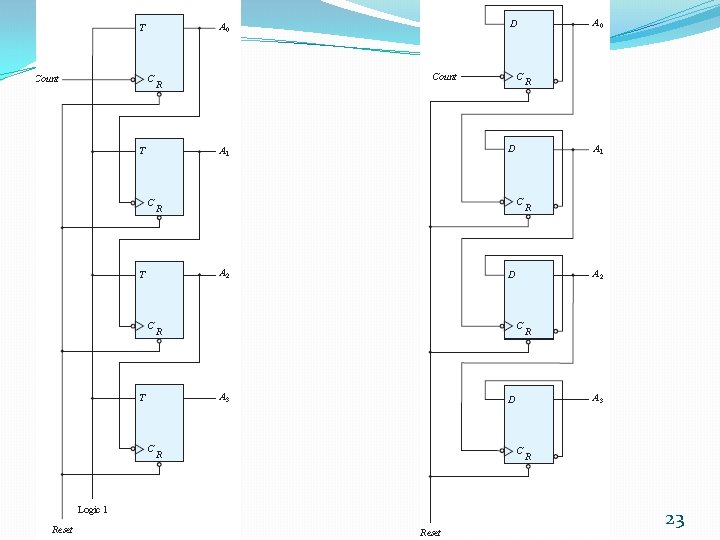

Binary Ripple Counters �Consists of a series connection of complementing flip‐flops, with the output of each flip‐flop connected to the Clock input of the next higher order flip‐flop. �Complementing flip‐flops: �T-FF T = 1 �JK-FF Both J and K inputs are tie together and equal to 1 �D-FF Q’ feedback to D input 22

23

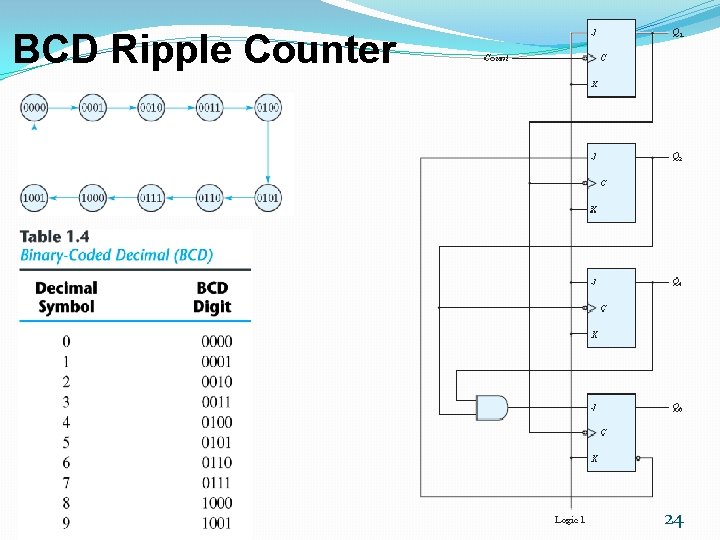

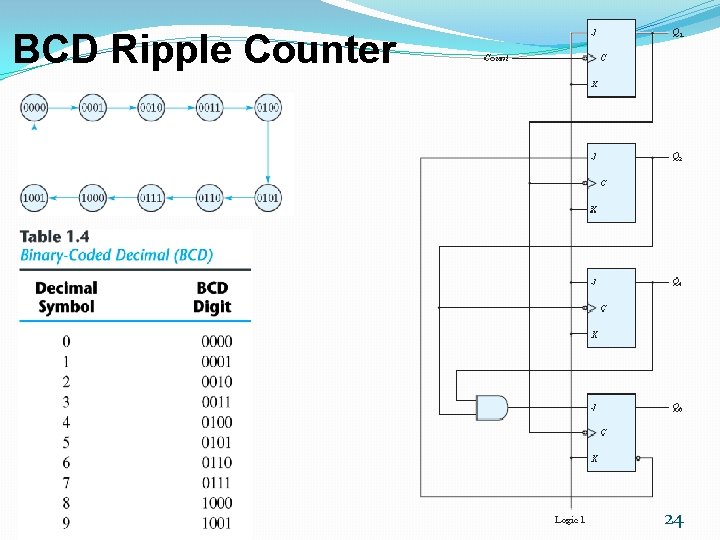

BCD Ripple Counter 24

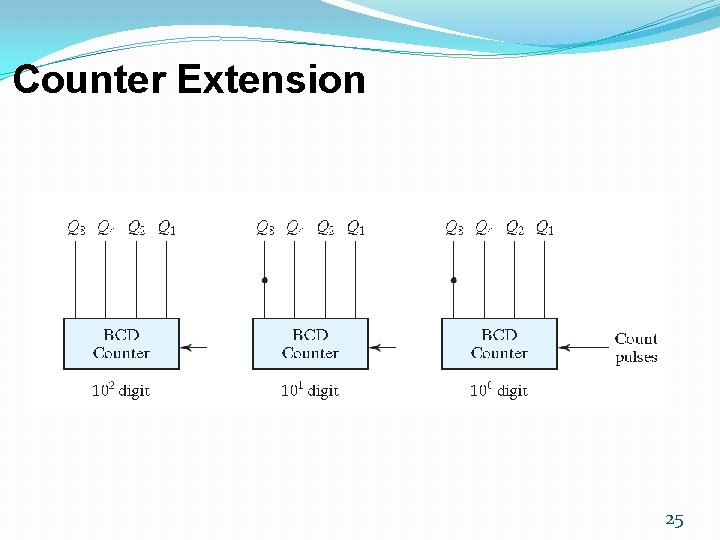

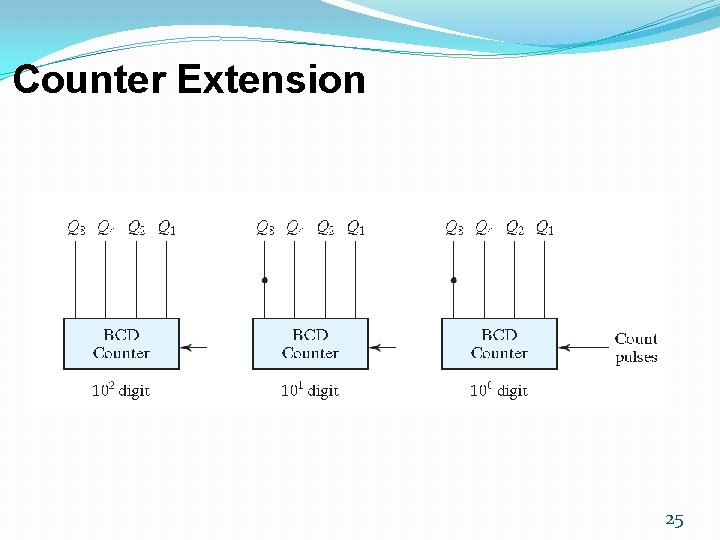

Counter Extension 25

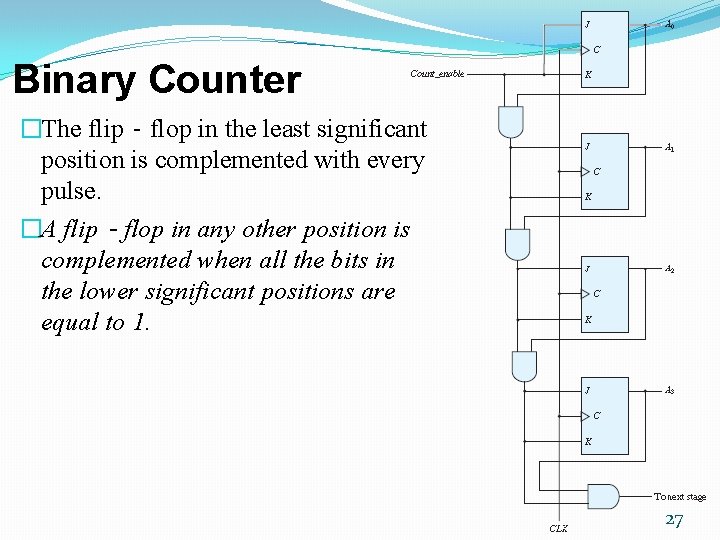

Synchronous Counters �Synchronous counters are different from ripple counters in that clock pulses are applied to the inputs of all flip‐flops. �The decision whether a flip‐flop is to be complemented is determined from the values of the data inputs, such as T or J and K at the time of the clock edge. 26

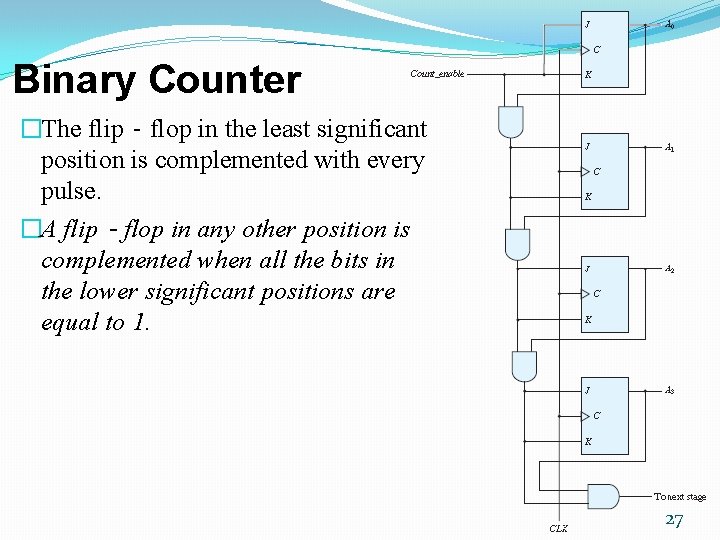

Binary Counter �The flip‐flop in the least significant position is complemented with every pulse. �A flip‐flop in any other position is complemented when all the bits in the lower significant positions are equal to 1. 27

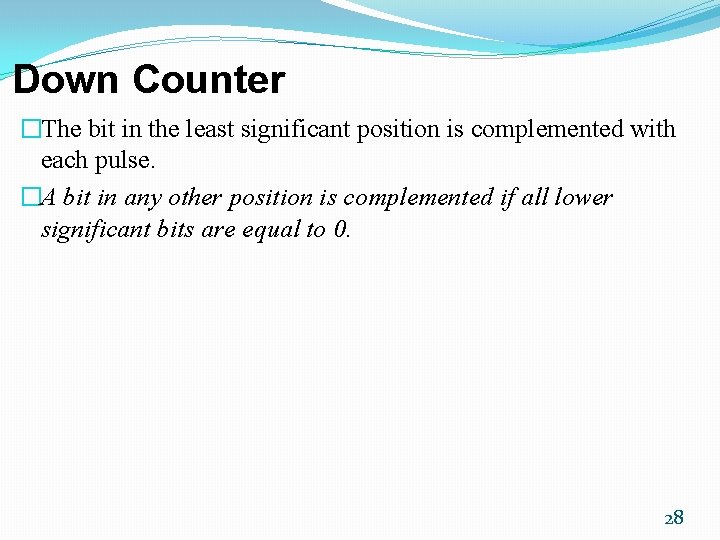

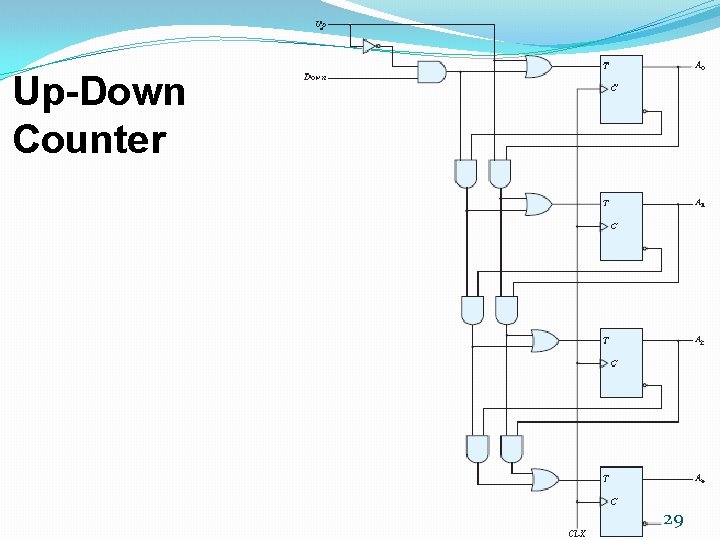

Down Counter �The bit in the least significant position is complemented with each pulse. �A bit in any other position is complemented if all lower significant bits are equal to 0. 28

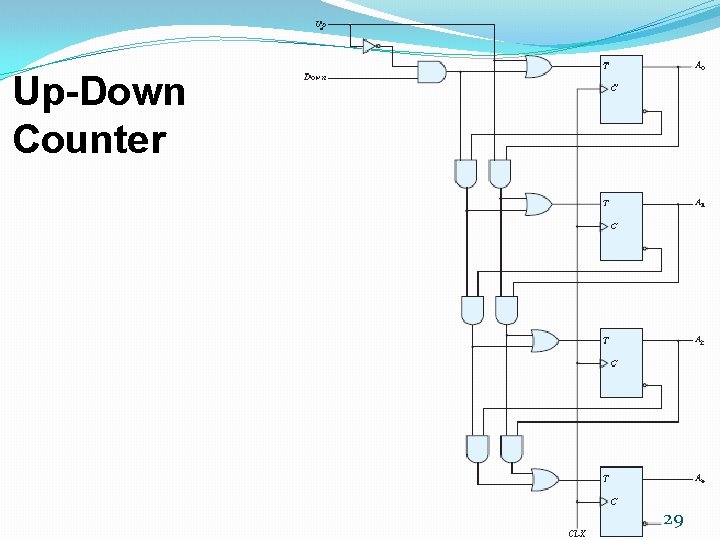

Up-Down Counter 29

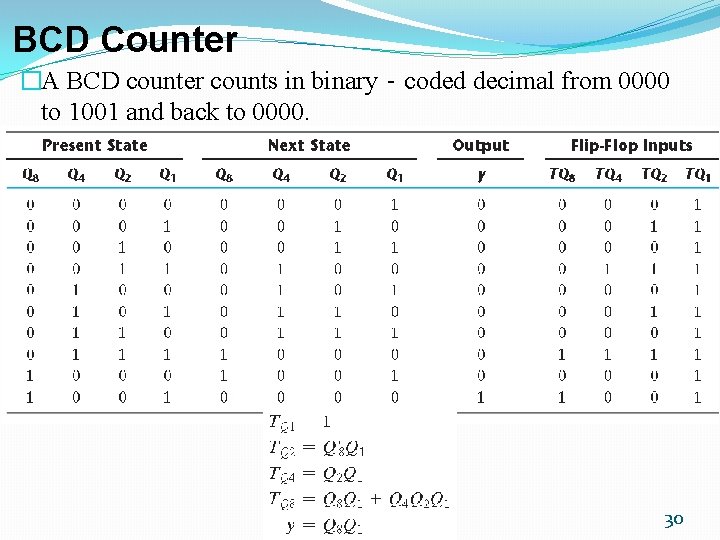

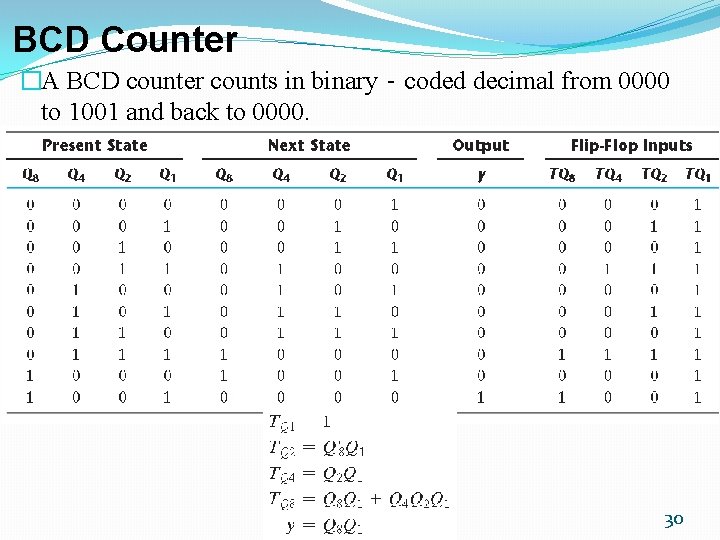

BCD Counter �A BCD counter counts in binary‐coded decimal from 0000 to 1001 and back to 0000. 30

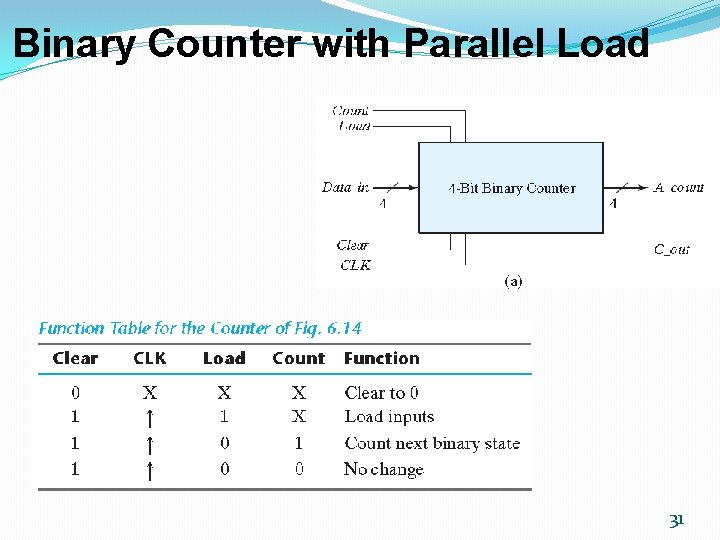

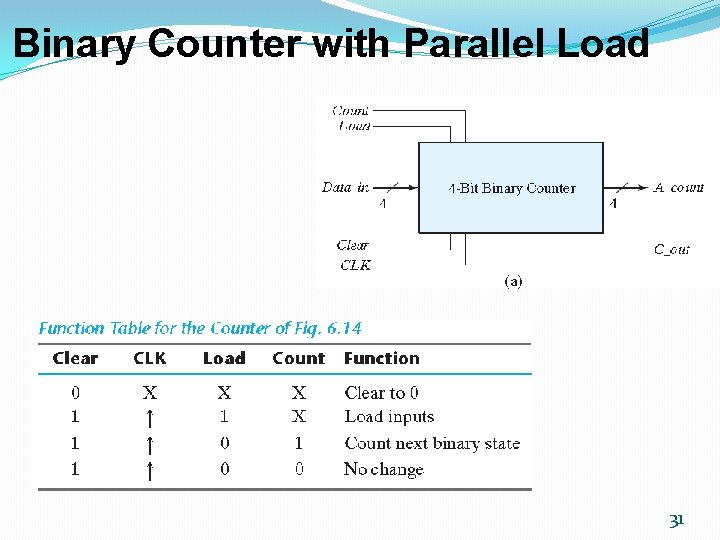

Binary Counter with Parallel Load 31

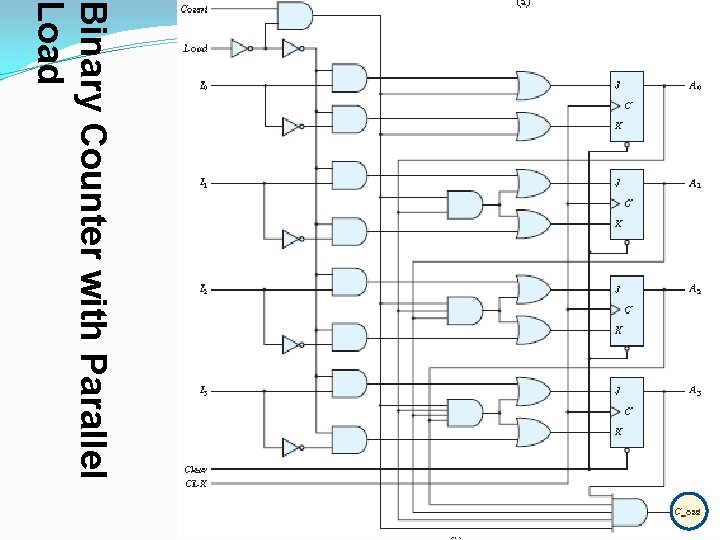

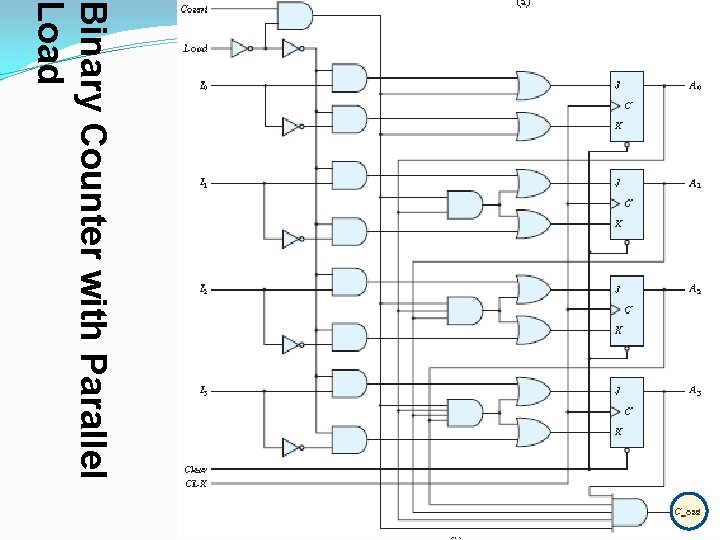

Binary Counter with Parallel Load 32

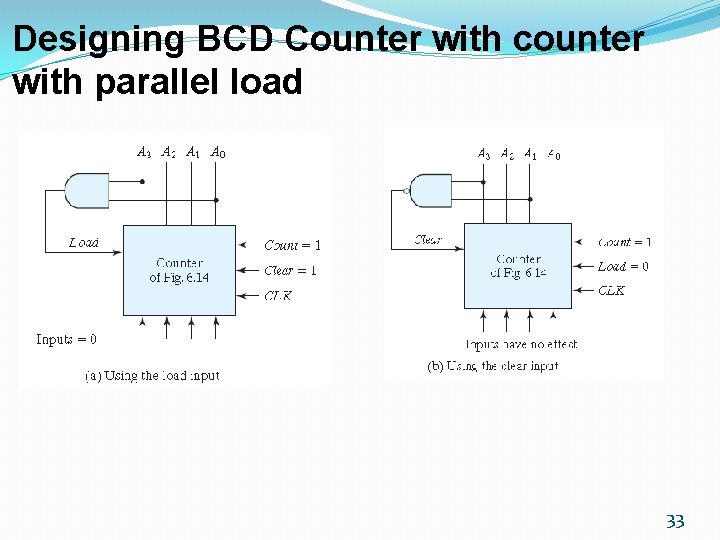

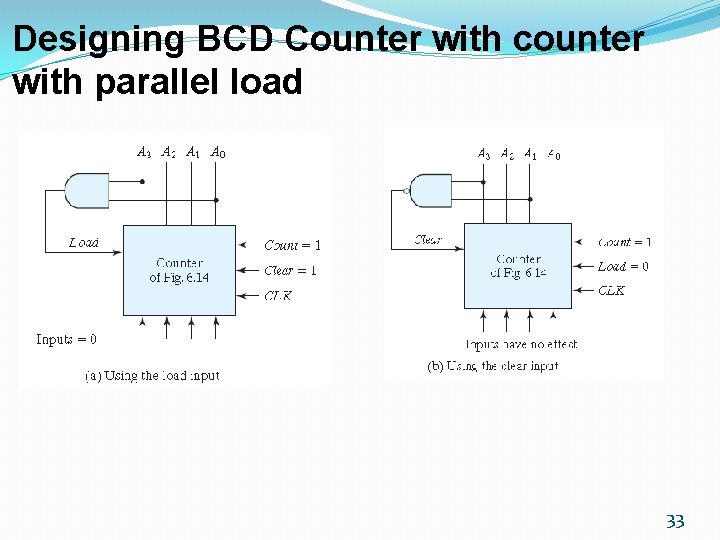

Designing BCD Counter with counter with parallel load 33

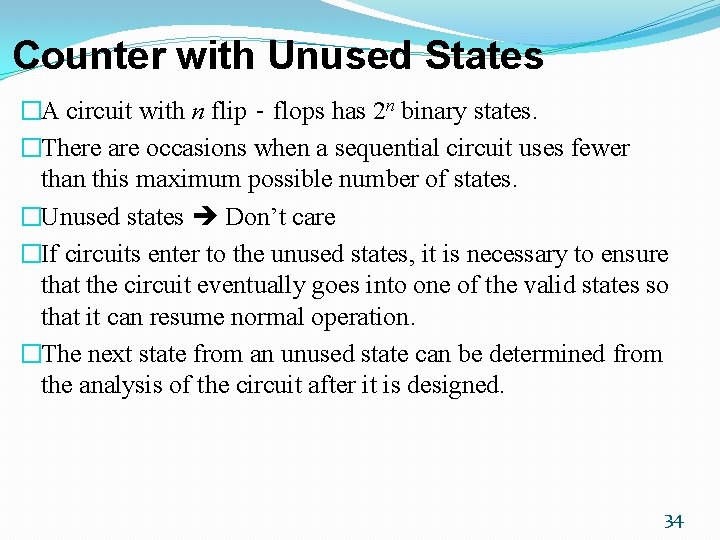

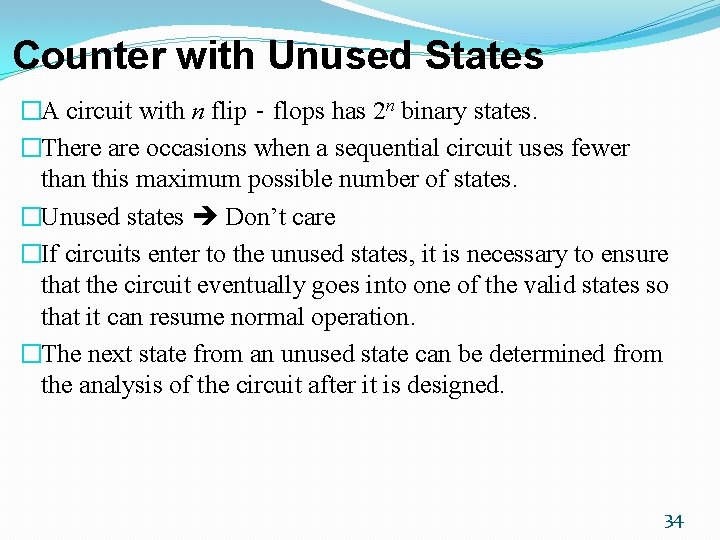

Counter with Unused States �A circuit with n flip‐flops has 2 n binary states. �There are occasions when a sequential circuit uses fewer than this maximum possible number of states. �Unused states Don’t care �If circuits enter to the unused states, it is necessary to ensure that the circuit eventually goes into one of the valid states so that it can resume normal operation. �The next state from an unused state can be determined from the analysis of the circuit after it is designed. 34

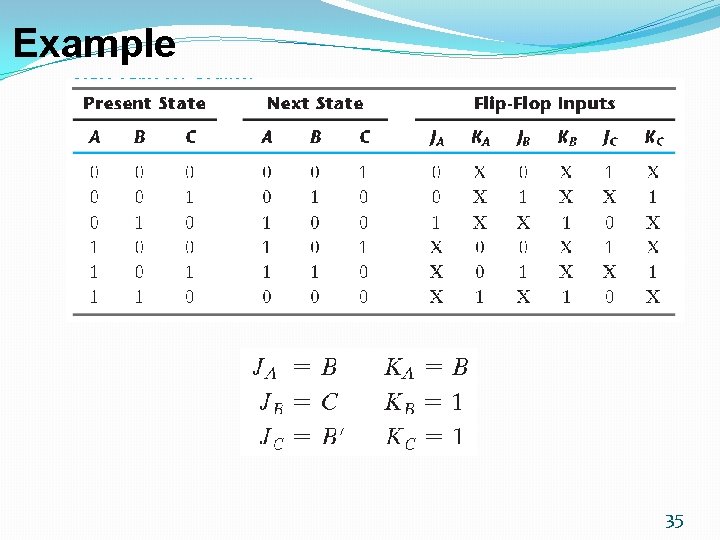

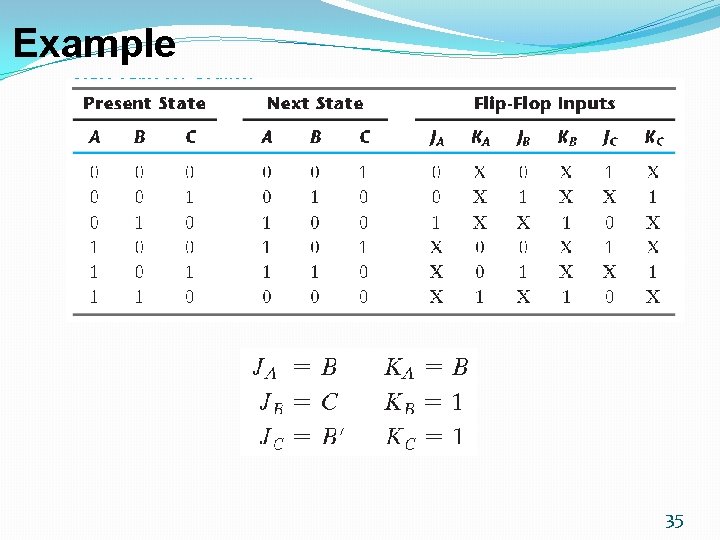

Example 35

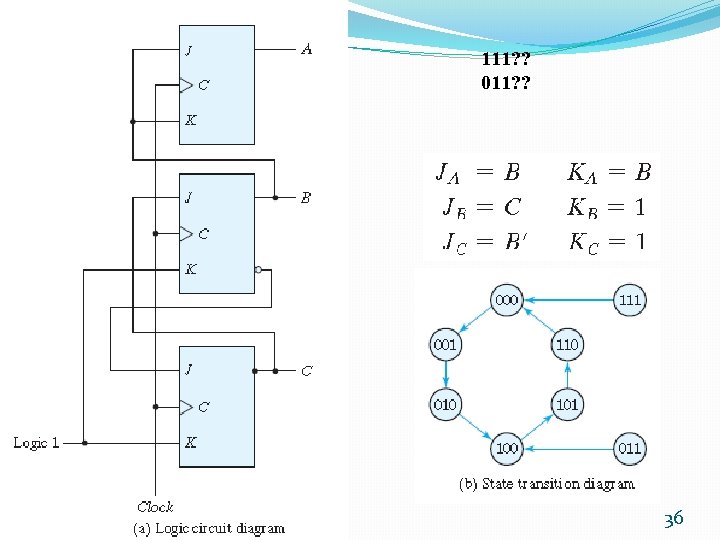

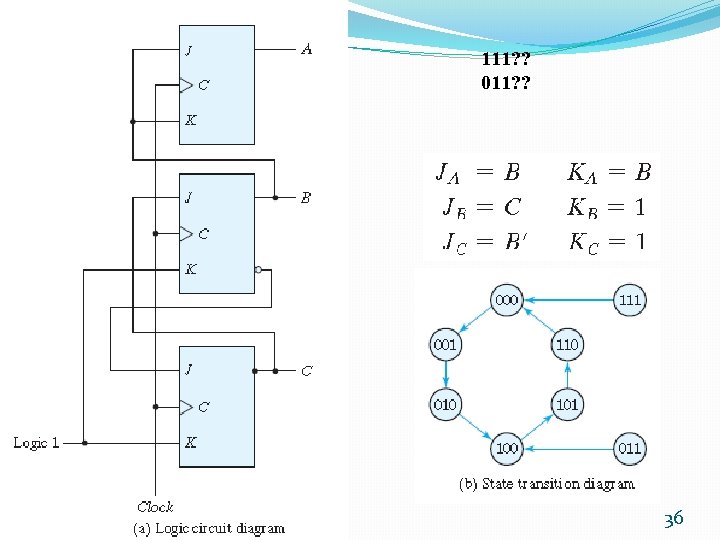

111? ? 011? ? 36

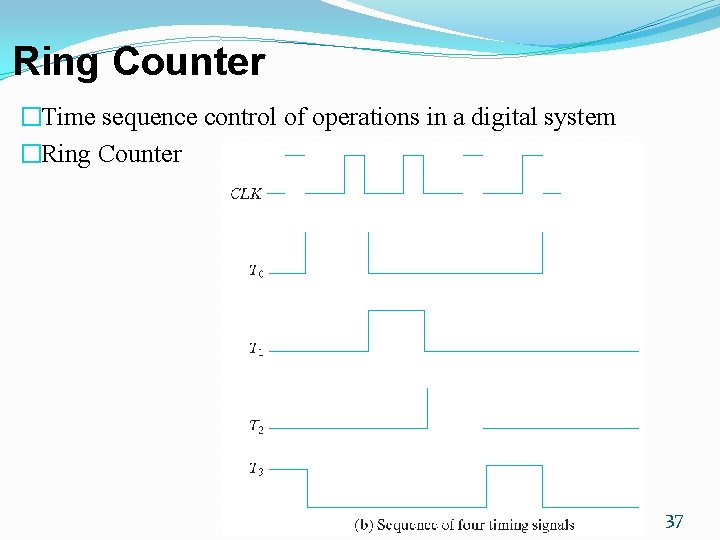

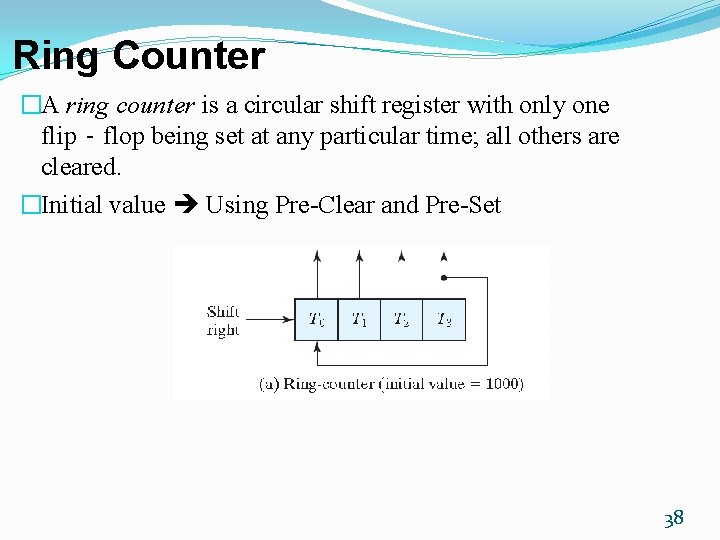

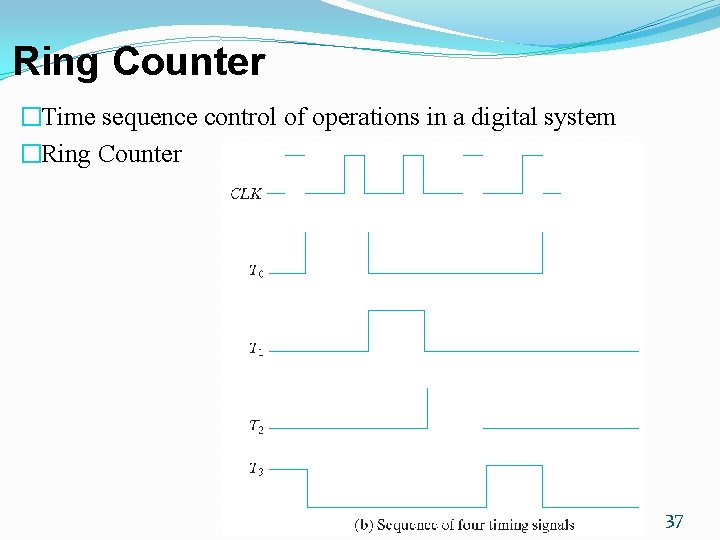

Ring Counter �Time sequence control of operations in a digital system �Ring Counter 37

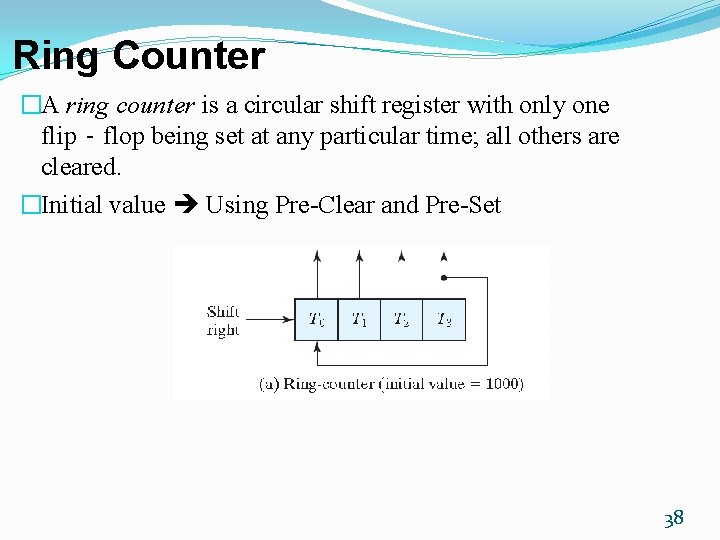

Ring Counter �A ring counter is a circular shift register with only one flip‐flop being set at any particular time; all others are cleared. �Initial value Using Pre-Clear and Pre-Set 38

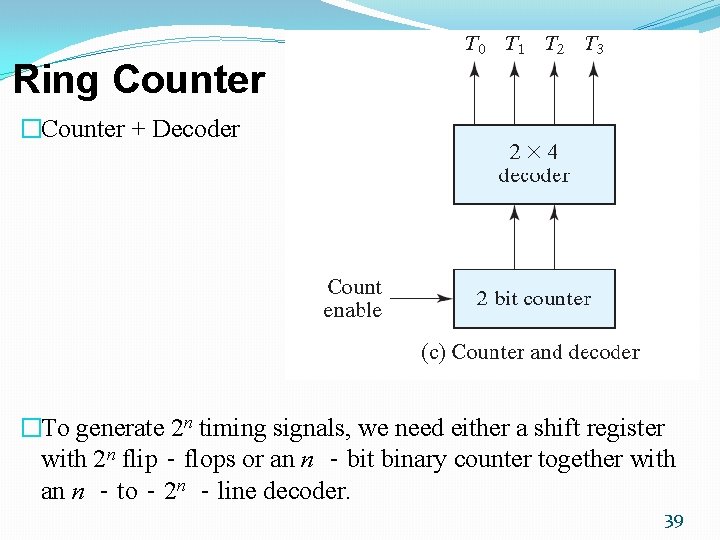

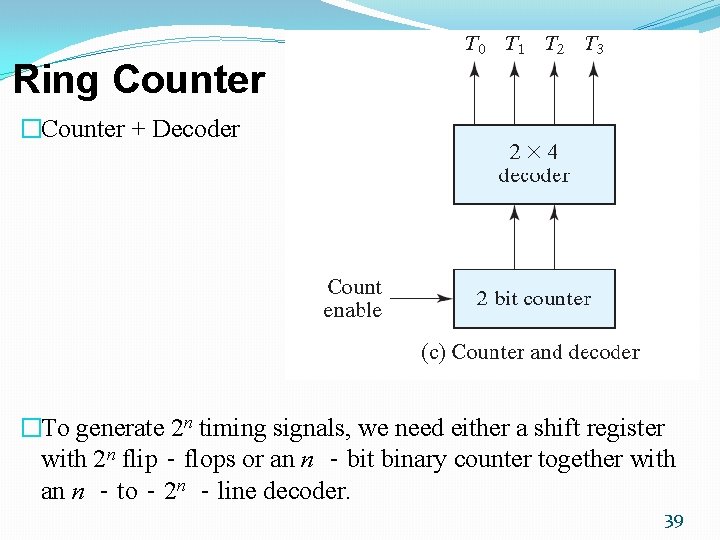

Ring Counter �Counter + Decoder �To generate 2 n timing signals, we need either a shift register with 2 n flip‐flops or an n ‐bit binary counter together with an n ‐to‐ 2 n ‐line decoder. 39

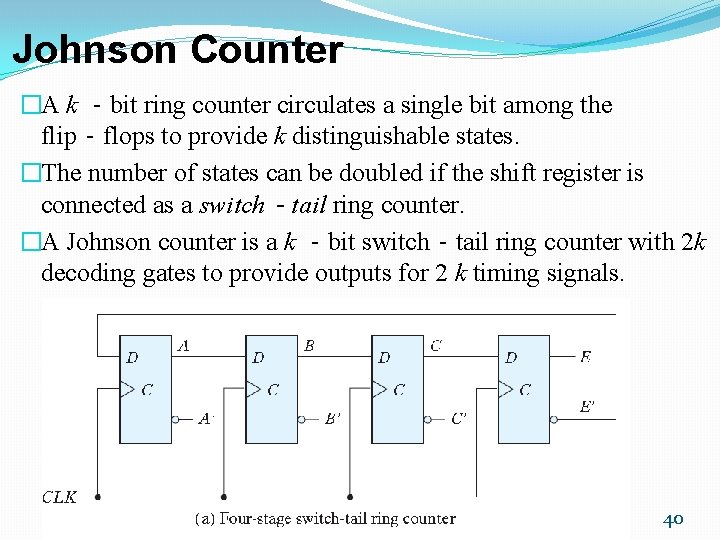

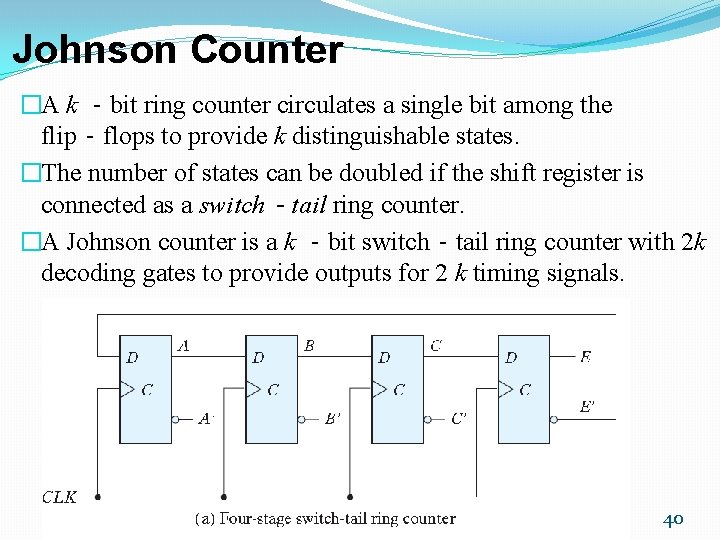

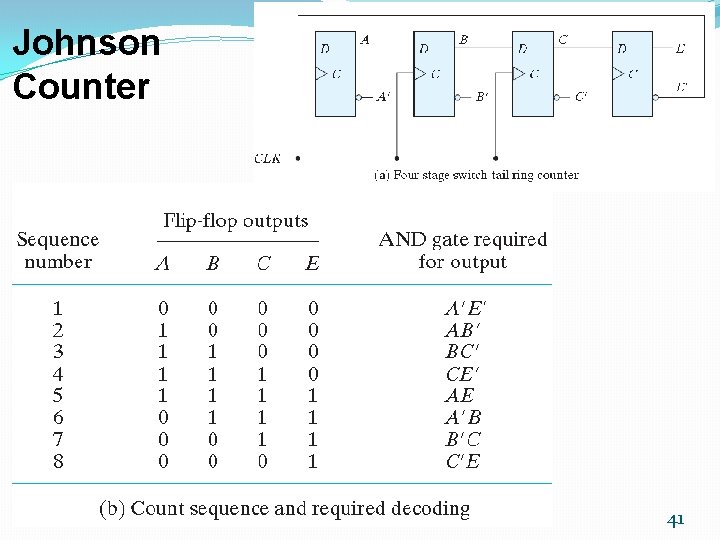

Johnson Counter �A k ‐bit ring counter circulates a single bit among the flip‐flops to provide k distinguishable states. �The number of states can be doubled if the shift register is connected as a switch‐tail ring counter. �A Johnson counter is a k ‐bit switch‐tail ring counter with 2 k decoding gates to provide outputs for 2 k timing signals. 40

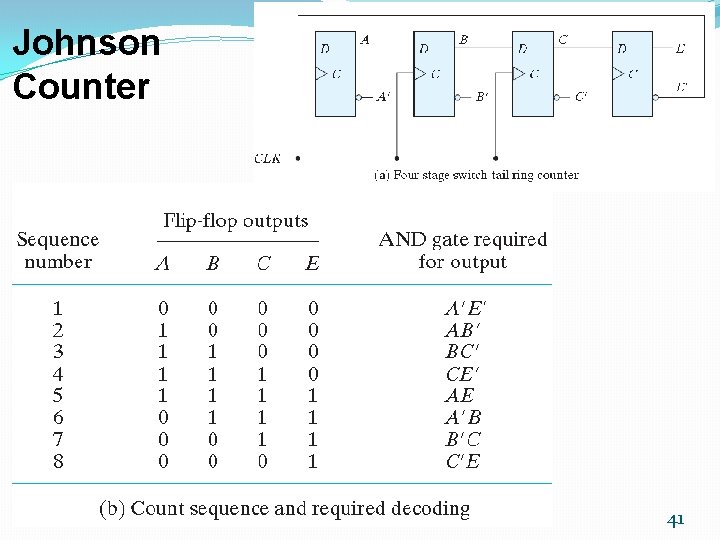

Johnson Counter 41

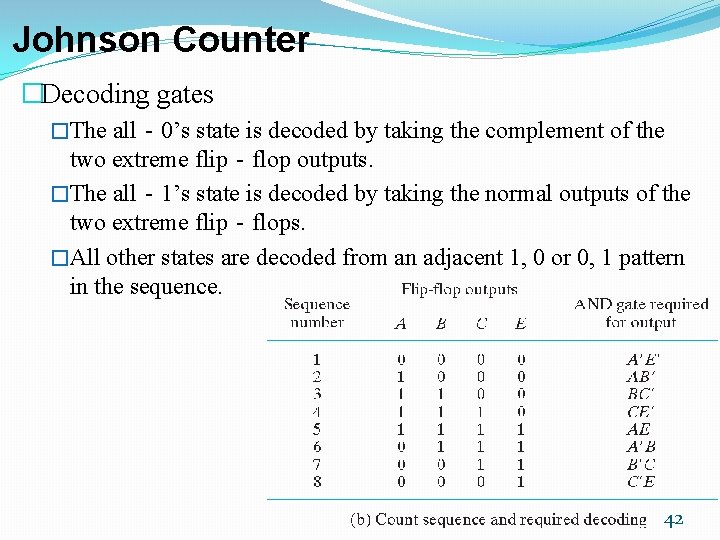

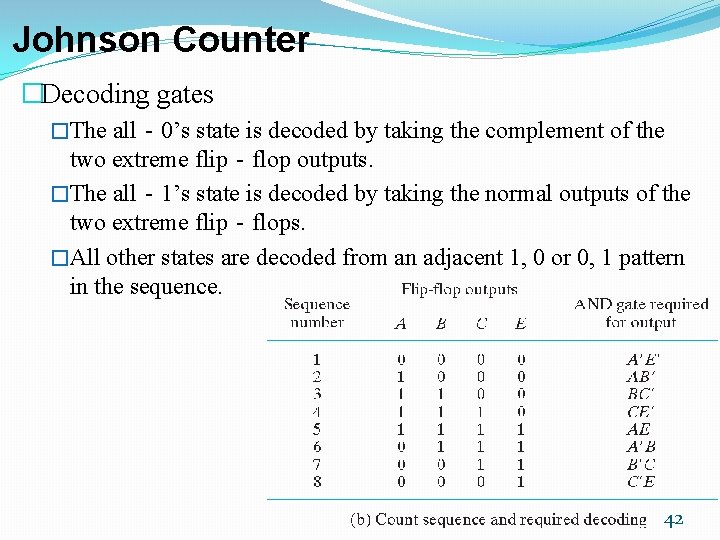

Johnson Counter �Decoding gates �The all‐ 0’s state is decoded by taking the complement of the two extreme flip‐flop outputs. �The all‐ 1’s state is decoded by taking the normal outputs of the two extreme flip‐flops. �All other states are decoded from an adjacent 1, 0 or 0, 1 pattern in the sequence. 42