1 Lecture 09 Muhammad Abbas Computer System Architecture

1 Lecture # 09 Muhammad Abbas Computer System Architecture

2 CPU Intel AMD Motorola

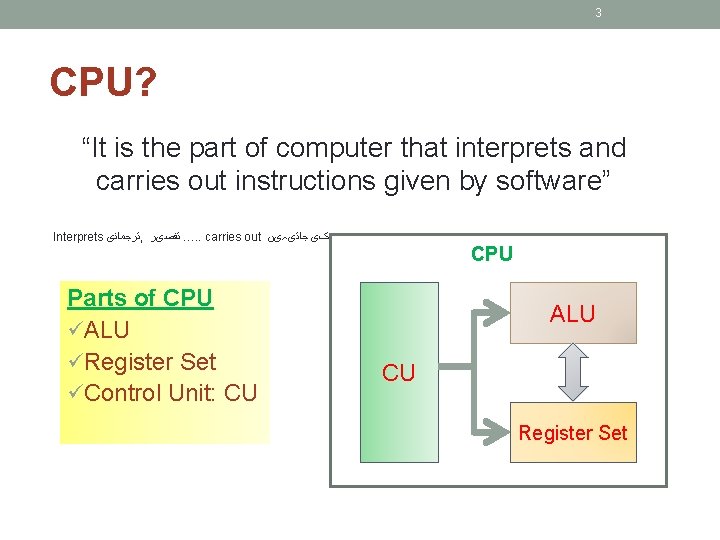

3 CPU? “It is the part of computer that interprets and carries out instructions given by software” Interprets ﺗﺮﺟﻤﺎﻧی , … ﺗﻔﺼیﺮ. . carries out کی ﺟﺎﺗی ہیں Parts of CPU üALU üRegister Set üControl Unit: CU CPU ALU CU Register Set

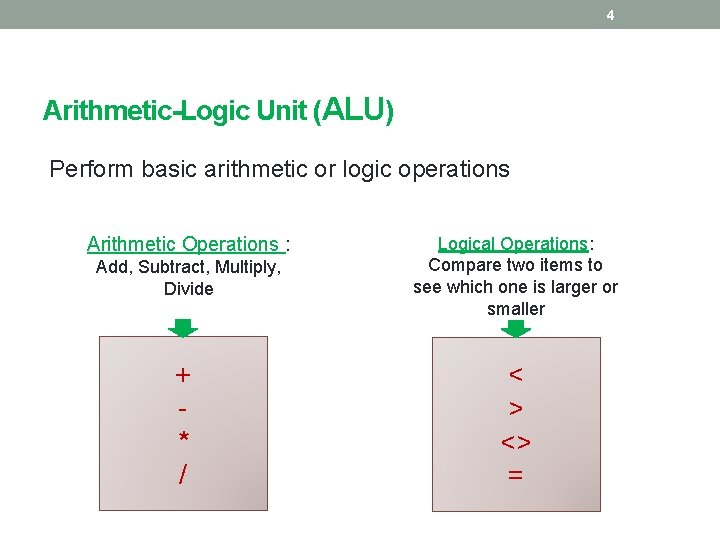

4 Arithmetic-Logic Unit (ALU) Perform basic arithmetic or logic operations Arithmetic Operations : Add, Subtract, Multiply, Divide + * / Logical Operations: Compare two items to see which one is larger or smaller < > <> =

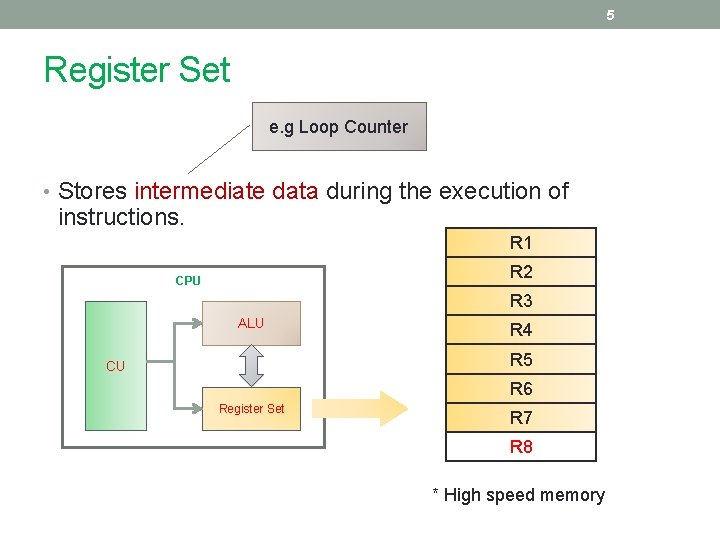

5 Register Set e. g Loop Counter • Stores intermediate data during the execution of instructions. R 1 R 2 CPU R 3 ALU R 4 R 5 CU R 6 Register Set R 7 R 8 * High speed memory

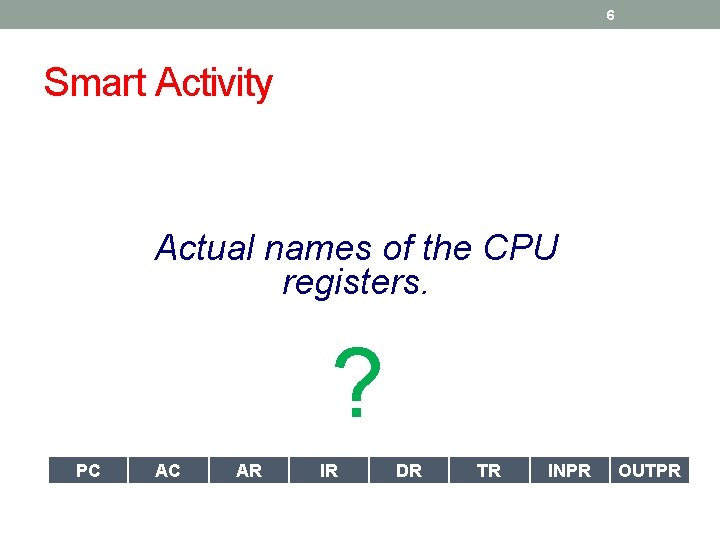

6 Smart Activity Actual names of the CPU registers. ? PC AC AR IR DR TR INPR OUTPR

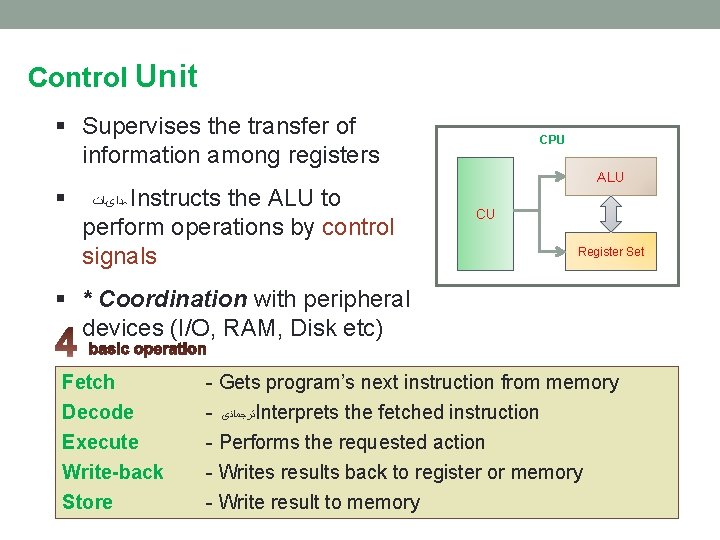

Control Unit § Supervises the transfer of information among registers § Instructs the ALU to perform operations by control signals ہﺪﺍیﺎﺕ CPU ALU CU Register Set § * Coordination with peripheral devices (I/O, RAM, Disk etc) Fetch Decode - Gets program’s next instruction from memory - ﺗﺮﺟﻤﺎﻧی Interprets the fetched instruction Execute Write-back Store - Performs the requested action - Writes results back to register or memory - Write result to memory

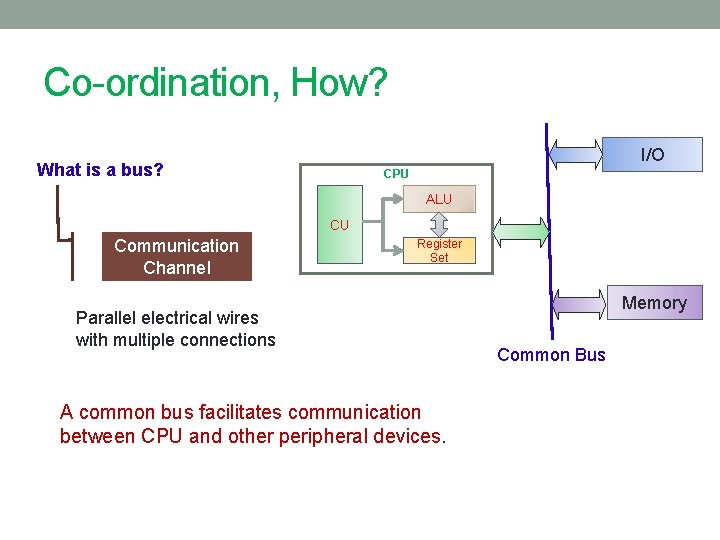

Co-ordination, How? I/O What is a bus? CPU ALU CU Communication Channel Register Set Parallel electrical wires with multiple connections A common bus facilitates communication between CPU and other peripheral devices. Memory Common Bus

9 Assignment Q(1) Submission Time: Next Monday Common Bus System vs Modern Computers’ Bus System ? ü ü ü Content must be concise: *single page Submit hard copy (printed), no file cover Plagiarism will be entertained with 0 marks. Quality will be proffered over quantity. Marks distribution: Content Quality : 08 Diagrams : 02 Total : 10

10 Remember…. • All communication with CPU registers happens through common bus system. • Registers communicate with each other for direct data transfer as well as • Special control signals are used to control the communication. Source of control signals?

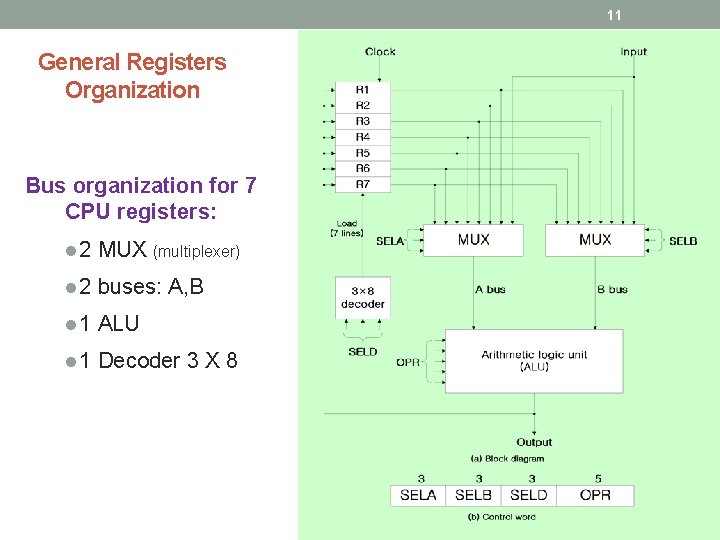

11 General Registers Organization Bus organization for 7 CPU registers: l 2 MUX (multiplexer) l 2 buses: A, B l 1 ALU l 1 Decoder 3 X 8

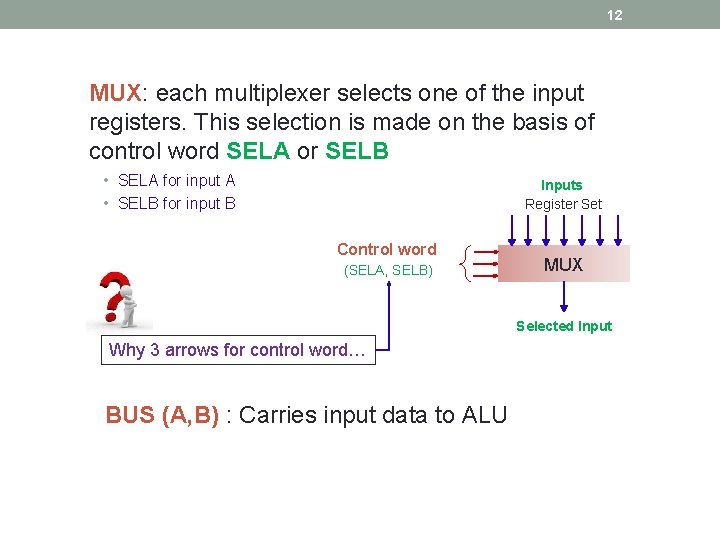

12 MUX: each multiplexer selects one of the input registers. This selection is made on the basis of control word SELA or SELB • SELA for input A • SELB for input B Inputs Register Set Control word (SELA, SELB) MUX Selected Input Why 3 arrows for control word… BUS (A, B) : Carries input data to ALU

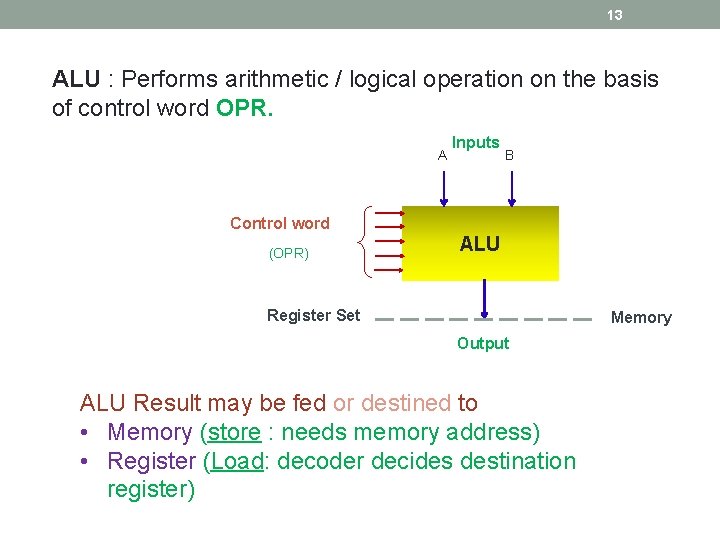

13 ALU : Performs arithmetic / logical operation on the basis of control word OPR. A Inputs B Control word (OPR) ALU Register Set Memory Output ALU Result may be fed or destined to • Memory (store : needs memory address) • Register (Load: decoder decides destination register)

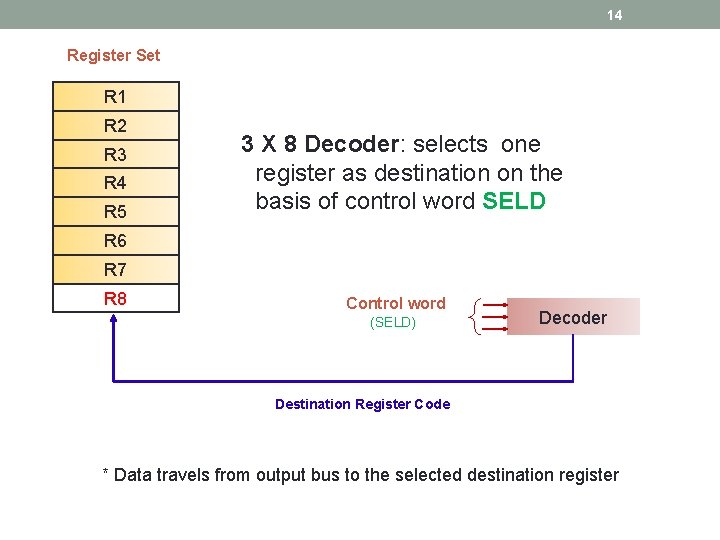

14 Register Set R 1 R 2 R 3 R 4 R 5 3 X 8 Decoder: selects one register as destination on the basis of control word SELD R 6 R 7 R 8 Control word (SELD) Decoder Destination Register Code * Data travels from output bus to the selected destination register

15 Smart mind? Consider an operation : R 3=R 1+R 2 Is it load or store operation? What will be the destination register? Try to express the given operation in your own word.

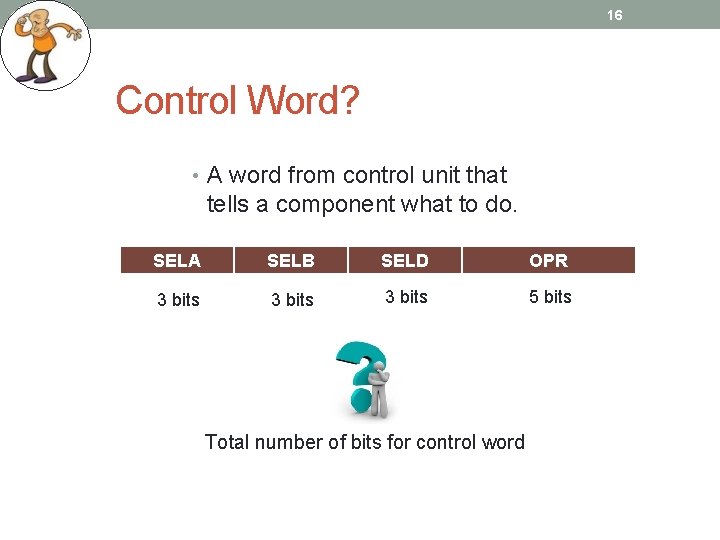

16 Control Word? • A word from control unit that tells a component what to do. SELA SELB SELD OPR 3 bits 5 bits Total number of bits for control word

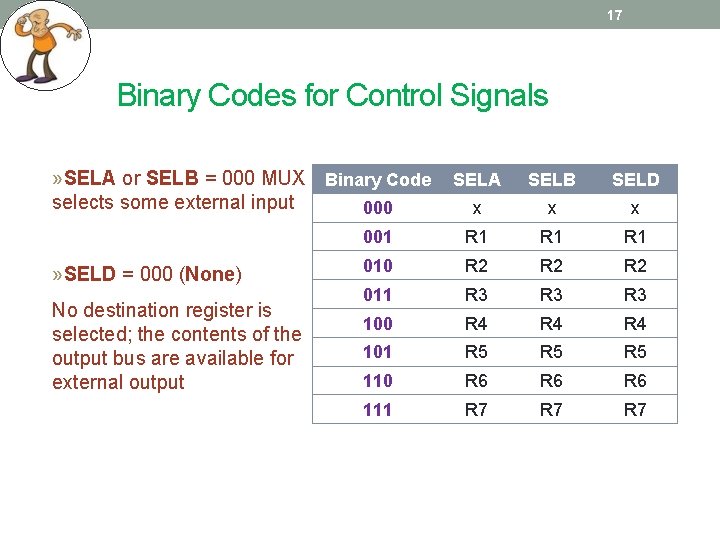

17 Binary Codes for Control Signals » SELA or SELB = 000 MUX Binary Code selects some external input 000 » SELD = 000 (None) No destination register is selected; the contents of the output bus are available for external output SELA SELB SELD x x x 001 R 1 R 1 010 R 2 R 2 011 R 3 R 3 100 R 4 R 4 101 R 5 R 5 110 R 6 R 6 111 R 7 R 7

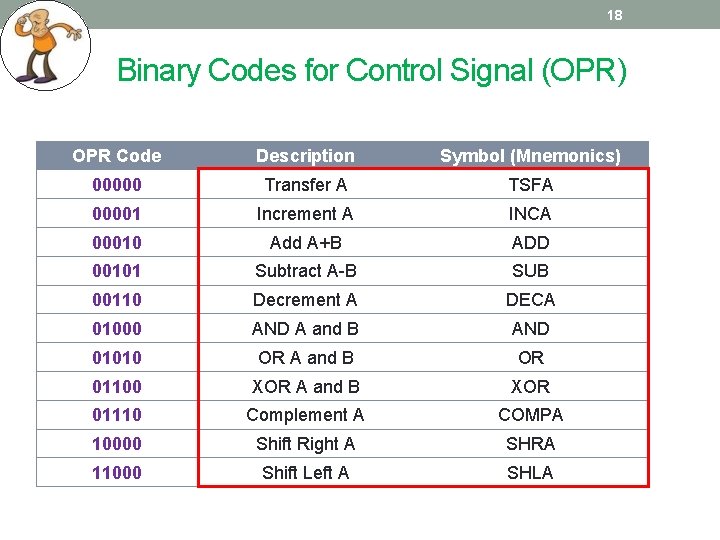

18 Binary Codes for Control Signal (OPR) OPR Code Description Symbol (Mnemonics) 00000 Transfer A TSFA 00001 Increment A INCA 00010 Add A+B ADD 00101 Subtract A-B SUB 00110 Decrement A DECA 01000 AND A and B AND 01010 OR A and B OR 01100 XOR A and B XOR 01110 Complement A COMPA 10000 Shift Right A SHRA 11000 Shift Left A SHLA

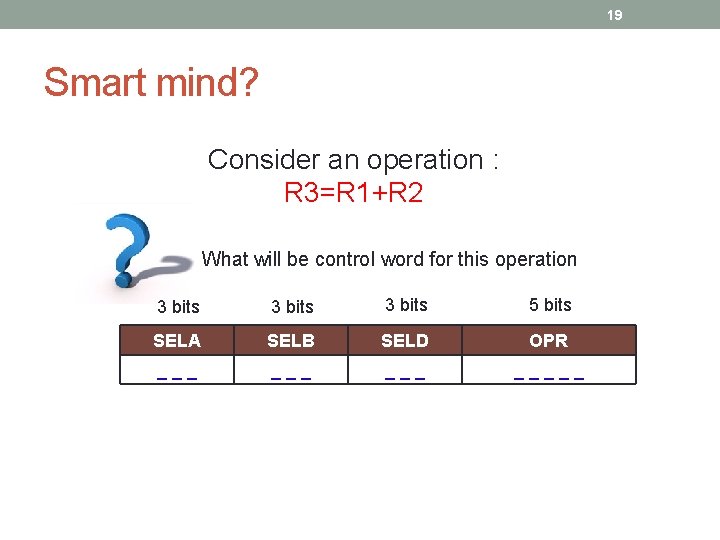

19 Smart mind? Consider an operation : R 3=R 1+R 2 What will be control word for this operation 3 bits 5 bits SELA SELB SELD OPR ___ _____

Next lecture… Stack organization

21 A h a ll iz f a H

- Slides: 21