1 Henry Selvaraj Henry Selvaraj Henry Selvaraj Henry

- Slides: 27

1 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; EEG 707 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Logic Synthesis Dr Henry Selvaraj Department of Electrical and Computer Engineering University of Nevada, Las Vegas Henry Selvaraj

2 Our Communication Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Room TBE B 324 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; 702 - 895 - 4184 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; selvaraj@ee. unlv. edu Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj

3 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Office Hours MW: between 12: 00 and 2: 00 p. m. You may also call me and fix an appointment for any other suitable time. Henry Selvaraj

4 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Subject Homepage The subject homepage is located at: http: //www. ee. unlv. edu/~selvaraj/eeg 707 Important announcements and notices will be posted in this page. You may also find some support materials for this subject. Henry Selvaraj

5 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Semester Grades will be computed as follows: 2 exams final exam/project home work/projects Total Henry Selvaraj 225 points (100+125) 150 points 125 points ______ 500 points

6 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Design Methodologies The implementation of a digital system depends on the design style. Constraints: size and role, economics and etc. Henry Selvaraj

7 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; ICs consist of transistors that are placed on the chip and are connected in such a way to realize the design. The locations and connectivity of the transistors are defined by several masks. A mask corresponds to one of the silicon compound layers that form the transistors and the interconnect layers. Henry Selvaraj

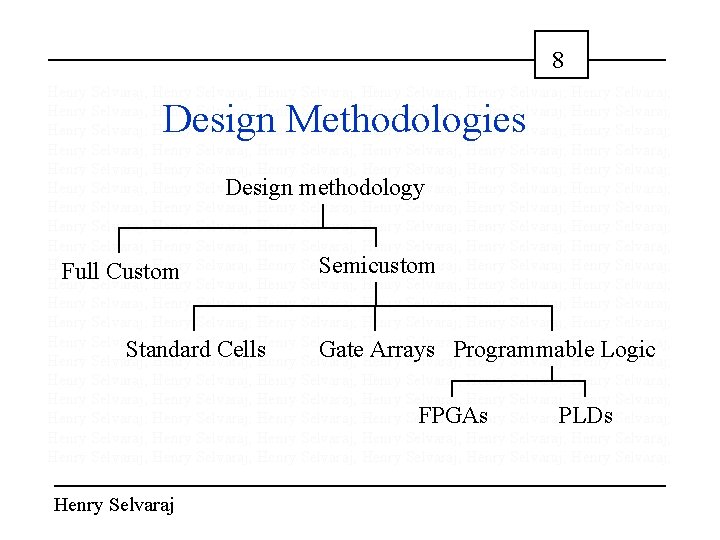

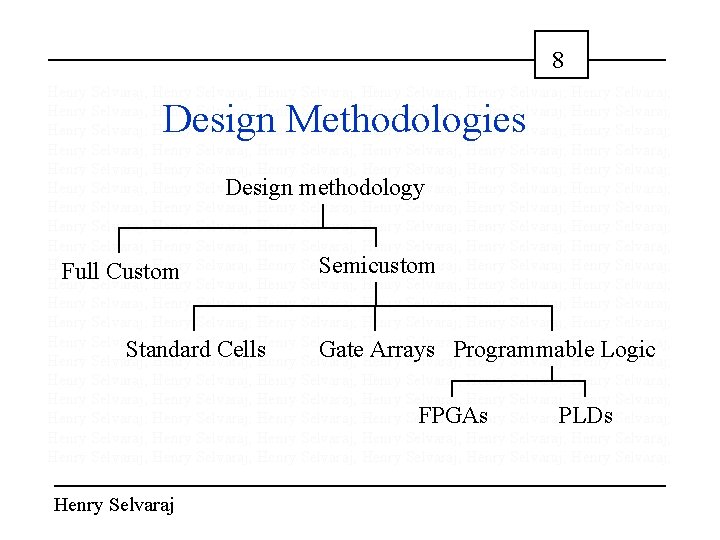

8 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Design methodology Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Semicustom Full Custom Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Standard Cells Gate Arrays Programmable Logic Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; FPGAs PLDs Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Design Methodologies Henry Selvaraj

9 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Application Specific Integrated Circuits (ASICs) can be defined as ICs designed for a particular application in low volumes or end use. Semicustom or standard ICs are field programmable (eg. Microprocessors) Henry Selvaraj

10 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Custom ICs are created using unique masks for all layers during Henry Selvaraj; Henry Selvaraj; the manufacturing process. The user controls chip density with Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; high utilization. Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Designer controls all stages of the chip layout and maximum Henry Selvaraj; Henry Selvaraj; design flexibility and high performance are possible. Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Only highly trained engineers are engaged in design. Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Developmental time is long and costs are extremely high. Henry Selvaraj; Henry Selvaraj; The high cost of design and testing can be successfully Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; amortized over the high volume. Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Custom ICs Henry Selvaraj

11 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Field Programmable Devices Like gate arrays, field programmable devices are prefabricated. However, the logic is implemented by electrically programming the interconnects and personalizing the basic cells, typically at the user’s place. Henry Selvaraj

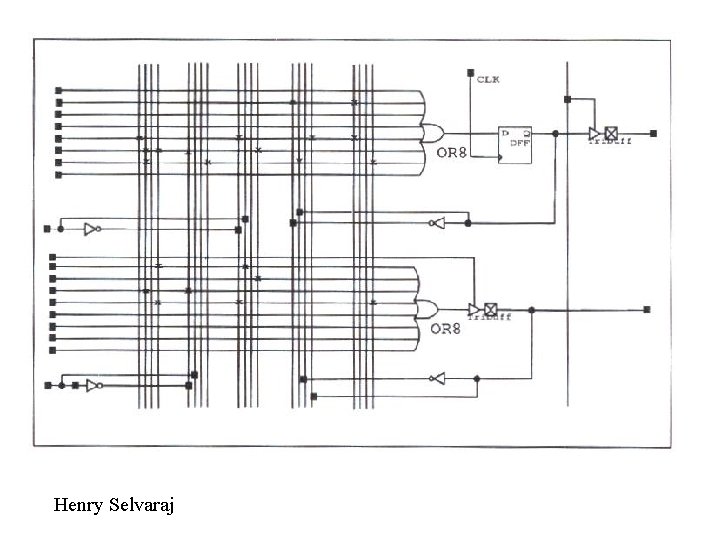

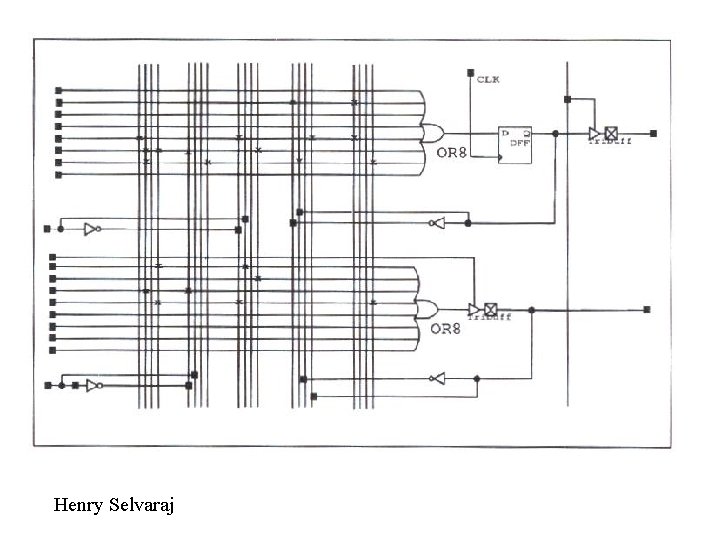

12 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Programmable Logic Devices (PLDs) PLDs consist of programmable AND arrays and programmable OR gates that are followed by flip-flops. Initially, PLDs used to be fabricated with bipolar technology; however, complementary metal-oxide semiconductors (CMOSs) are more popular now. Henry Selvaraj

13 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj

14 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Field Programmable Gate Array (FPGA) FPGAs combine the architecture of gate arrays with programmability of PLDs. Some of the FPGA real estate is occupied by vendor logic to implement the field programmability feature of the FPGA, and a large portion of the die is for programmable routing. Henry Selvaraj

15 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; The logic block (known also as LC, CLB and etc. ) consists of some universal gates, that is gates that can be programmed to represent any function. The connectivity between blocks is programmed via different types of devices, SRAM (static random-access memory), EEPROM, or antifuse. Henry Selvaraj

16 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Two basic architectures: • Matrix based: CLBs form islands in a matrix with horizontal and vertical channels. Eg. : Xilinx and Quick. Logic • CLBs form rows separated by routing channels like in a maskprogrammable gate array. Eg. : Actel Henry Selvaraj

17 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; (eg. A circuit with 250 TTL 7400 SSI chips (1000 NAND gates) can Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; be replaced by a Xilinx 3000 series chip. ) Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Advantages of of FPGAs • Replacement of SSI and MSI chips • Availability of parts off the shelf • rapid turnaround • low risk • reprogrammability Henry Selvaraj

18 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Limitation of FPGAs - your opportunities The FPGA -based circuit delay depends on the performance of the design implementation tools. The mapping of the logic design into the FPGA’s architecture requires sophisticated design implementation (CAD) tools. Henry Selvaraj

19 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; The Design cycle 1. entering the design in the form of schematic, netlist, logic expressions or hardware description languages 2. simulating the design for functional verification 3. mapping the design into the FPGA architecture 4. placing and routing the FPGA design Henry Selvaraj

20 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; 5. extracting delay parameters of the routed design 6. resimulating for timing verification 7. generating the FPGA device configuration format 8. configuring or programming the device 9. testing the product for undesirable functional behavior Henry Selvaraj

21 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; For every FPFA, the vendor provides design implementation tools to perform steps 3 through 8. Steps 1 and 2 can be performed using simulation software like PALASM, ABEL or VHDL editors/simulators. Henry Selvaraj

22 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Synthesis Simply put, synthesis is the translation of a design representation to a form that is amendable to minimal realization. High level synthesis: eg. VHDL to RTL Logic Synthesis: RTL-gate-level representation Henry Selvaraj

23 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Factors that can influence the design: • architacture • gate density • routing resources • programming method Henry Selvaraj

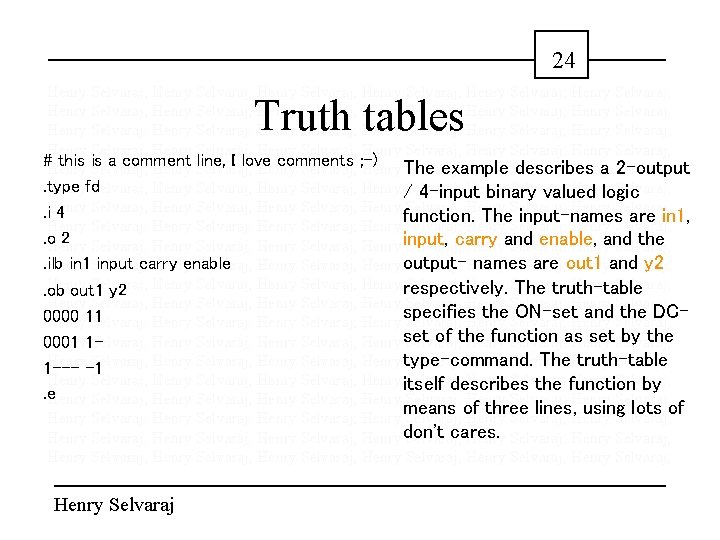

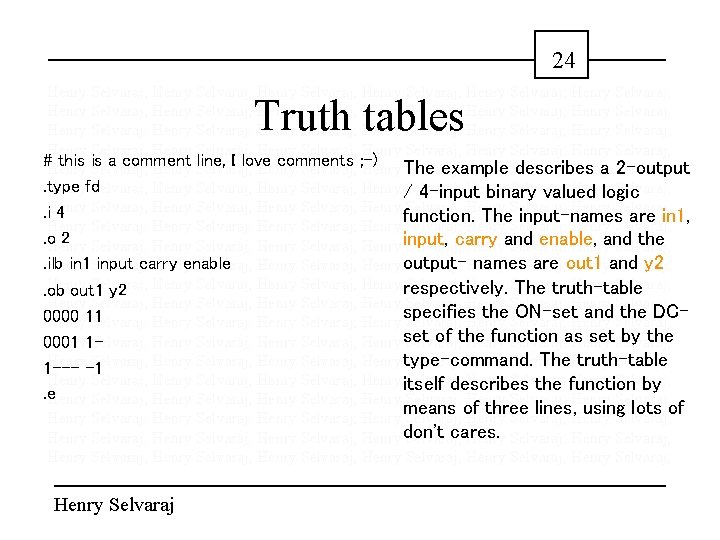

24 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; #Henry Selvaraj; Henry Selvaraj; this is a comment line, I love comments ; -) The example describes a 2 -output. type fd Henry Selvaraj; Henry Selvaraj; / 4 -input binary valued logic. i. Henry Selvaraj; Henry Selvaraj; 4 function. The input-names are in 1, Henry Selvaraj; Henry Selvaraj; . o. Henry Selvaraj; Henry Selvaraj; 2 input, carry and enable, and the. ilb in 1 input carry enable output- names are out 1 and y 2 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; respectively. The truth-table. ob out 1 y 2 Henry Selvaraj; Henry Selvaraj; specifies the ON-set and the DC 0000 11 Henry Selvaraj; Henry Selvaraj; set of the function as set by the Henry Selvaraj; Henry Selvaraj; 0001 1 Henry Selvaraj; Henry Selvaraj; type-command. The truth-table 1 ---1 Henry Selvaraj; Henry Selvaraj; itself describes the function by. e. Henry Selvaraj; Henry Selvaraj; means of three lines, using lots of Henry Selvaraj; Henry Selvaraj; don't cares. Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Truth tables Henry Selvaraj

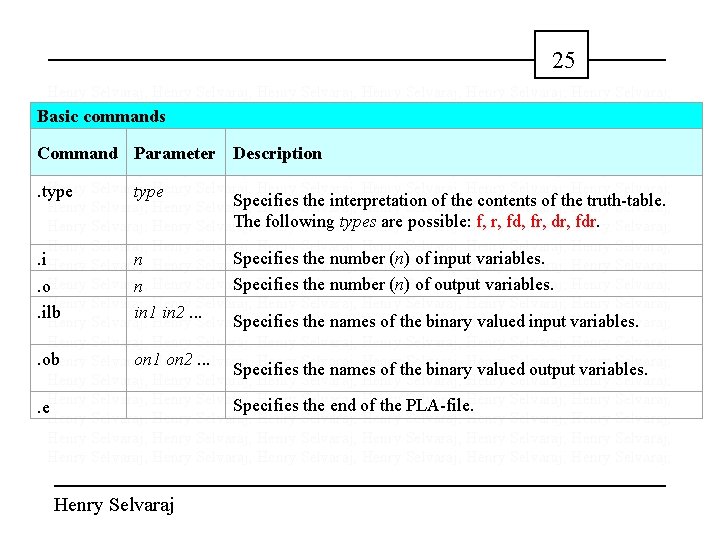

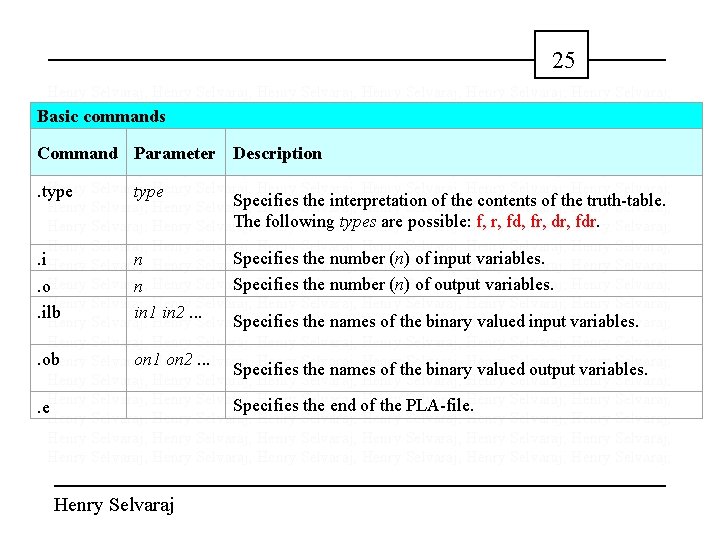

25 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Basic commands Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Command Parameter Description Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; . type Specifies the interpretation of the contents of the truth-table. Henry Selvaraj; Henry Selvaraj; The following types are possible: f, r, fd, fr, dr, fdr. Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Specifies the number (n) of input variables. . i Henry Selvaraj; Henry Selvaraj; n Specifies the number (n) of output variables. . o Henry Selvaraj; Henry Selvaraj; n Henry Selvaraj; Henry Selvaraj; . ilb in 1 in 2. . . Specifies the names of the binary valued input variables. Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; . ob on 1 on 2. . . Henry Selvaraj; Henry Selvaraj; Specifies the names of the binary valued output variables. Henry Selvaraj; Henry Selvaraj; Specifies the end of the PLA-file. . e Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj

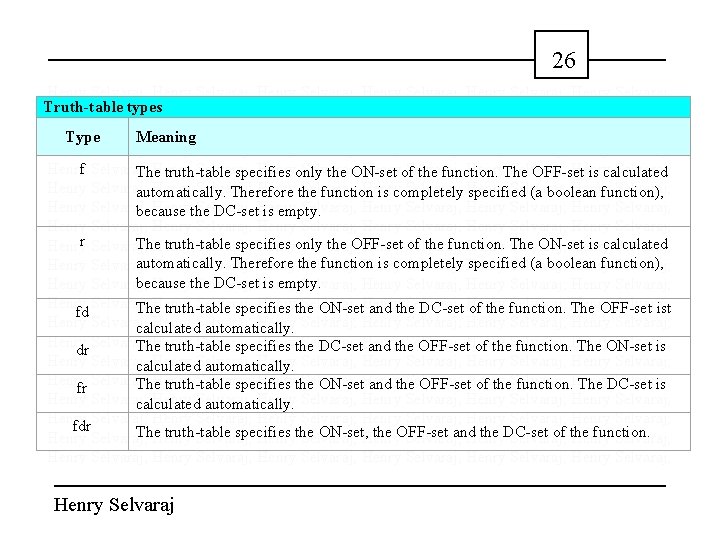

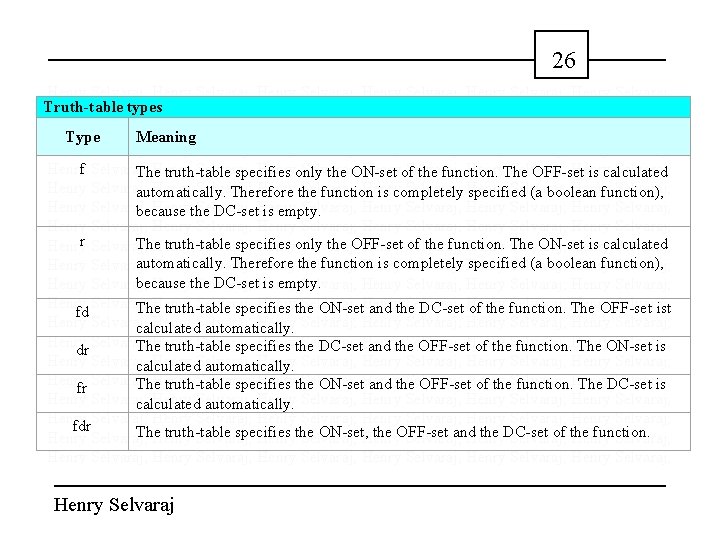

26 Henry Selvaraj; Henry Selvaraj; Truth-table types Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Type Meaning Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; f The truth-table specifies only the ON-set of the function. The OFF-set is calculated Henry Selvaraj; Henry Selvaraj; automatically. Therefore the function is completely specified (a boolean function), Henry Selvaraj; Henry Selvaraj; because the DC-set is empty. Henry Selvaraj; Henry Selvaraj; r The truth-table specifies only the OFF-set of the function. The ON-set is calculated Henry Selvaraj; Henry Selvaraj; automatically. Therefore the function is completely specified (a boolean function), Henry Selvaraj; Henry Selvaraj; because the DC-set is empty. Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; The truth-table specifies the ON-set and the DC-set of the function. The OFF-set ist fd Henry Selvaraj; Henry Selvaraj; calculated automatically. Henry Selvaraj; Henry Selvaraj; The truth-table specifies the DC-set and the OFF-set of the function. The ON-set is dr Henry Selvaraj; Henry Selvaraj; calculated automatically. Henry Selvaraj; Henry Selvaraj; The truth-table specifies the ON-set and the OFF-set of the function. The DC-set is fr Henry Selvaraj; Henry Selvaraj; calculated automatically. Henry Selvaraj; Henry Selvaraj; fdr The truth-table specifies the ON-set, the OFF-set and the DC-set of the function. Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj

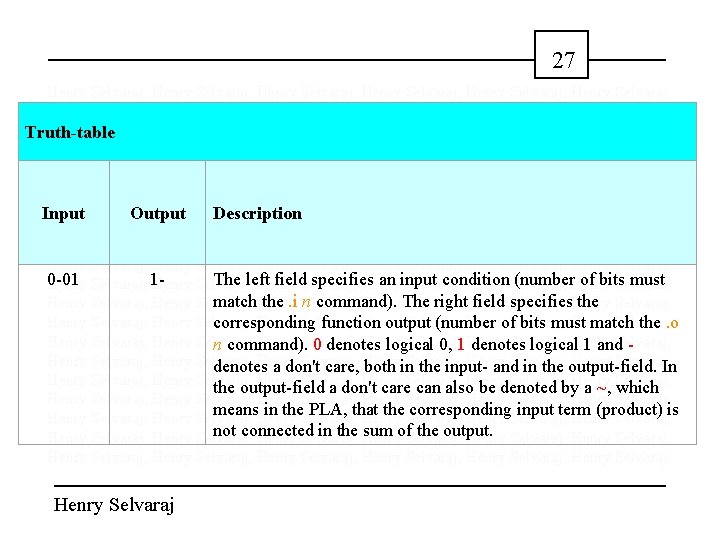

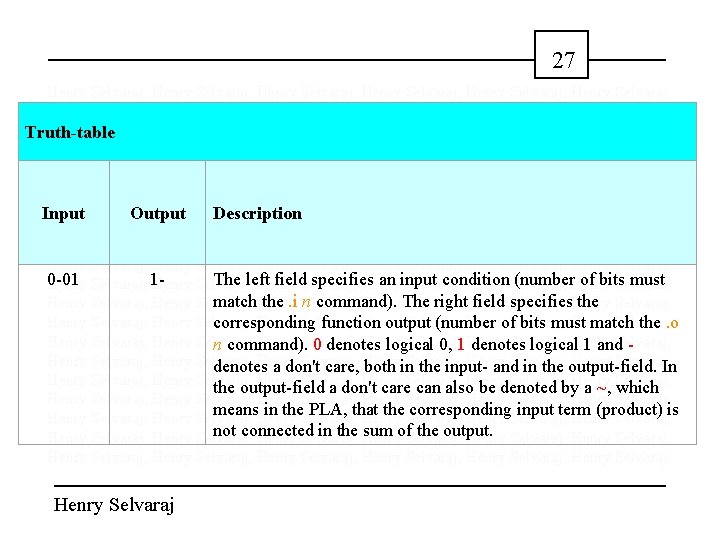

27 Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Truth-table Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Input Output Description Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; The left field specifies an input condition (number of bits must 0 -01 1 - Henry Selvaraj; Henry Selvaraj; match the. i n command). The right field specifies the Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; corresponding function output (number of bits must match the. o Henry Selvaraj; Henry Selvaraj; n command). 0 denotes logical 0, 1 denotes logical 1 and - Henry Selvaraj; Henry Selvaraj; denotes a don't care, both in the input- and in the output-field. In Henry Selvaraj; Henry Selvaraj; the output-field a don't care can also be denoted by a ~, which Henry Selvaraj; Henry Selvaraj; means in the PLA, that the corresponding input term (product) is Henry Selvaraj; Henry Selvaraj; not connected in the sum of the output. Henry Selvaraj; Henry Selvaraj; Henry Selvaraj; Henry Selvaraj