1 Exemplo 1 Projecto simples implementado em VHDL

- Slides: 26

1

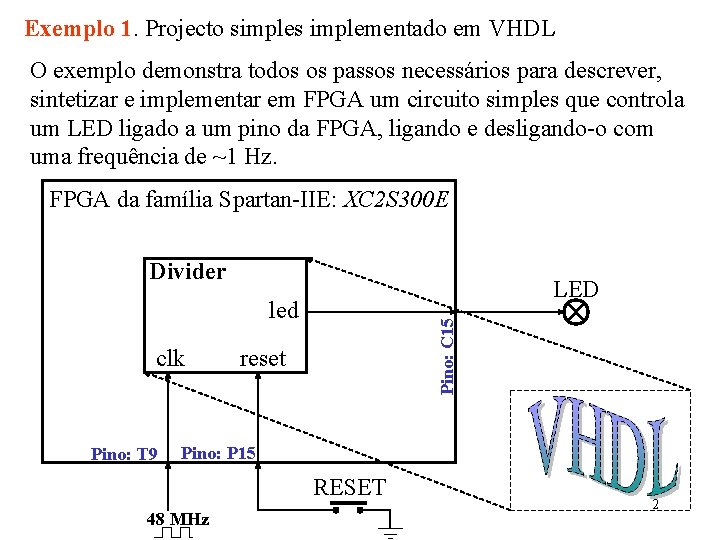

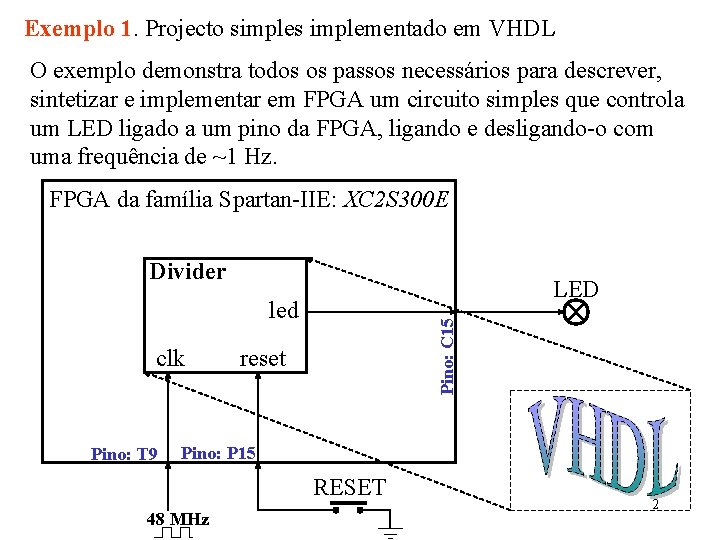

Exemplo 1. Projecto simples implementado em VHDL O exemplo demonstra todos os passos necessários para descrever, sintetizar e implementar em FPGA um circuito simples que controla um LED ligado a um pino da FPGA, ligando e desligando-o com uma frequência de ~1 Hz. FPGA da família Spartan-IIE: XC 2 S 300 E Divider LED clk Pino: T 9 Pino: C 15 led reset Pino: P 15 RESET 48 MHz 2

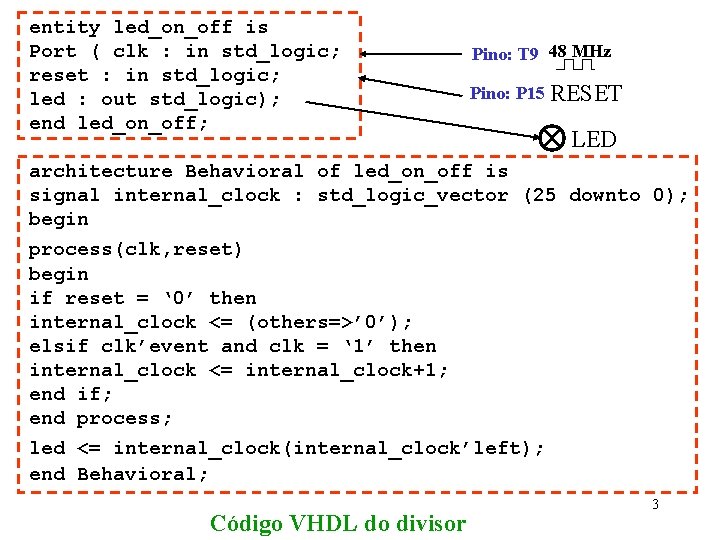

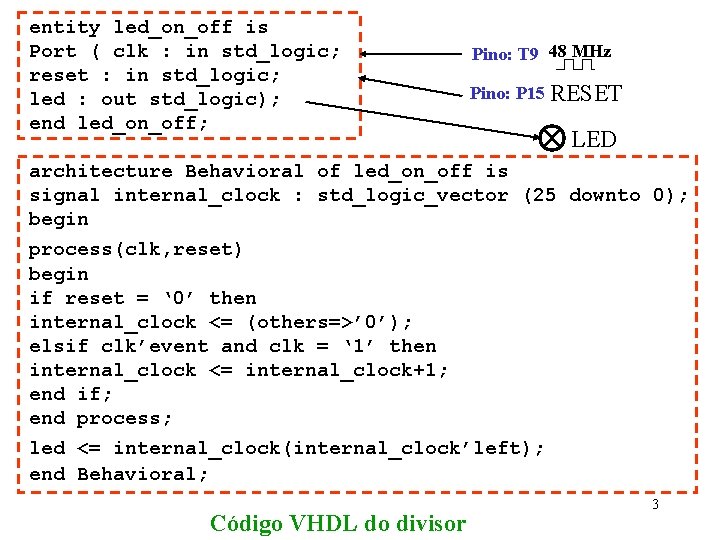

entity led_on_off is Port ( clk : in std_logic; reset : in std_logic; led : out std_logic); end led_on_off; Pino: T 9 48 MHz Pino: P 15 RESET LED architecture Behavioral of led_on_off is signal internal_clock : std_logic_vector (25 downto 0); begin process(clk, reset) begin if reset = ‘ 0’ then internal_clock <= (others=>’ 0’); elsif clk’event and clk = ‘ 1’ then internal_clock <= internal_clock+1; end if; end process; led <= internal_clock(internal_clock’left); end Behavioral; Código VHDL do divisor 3

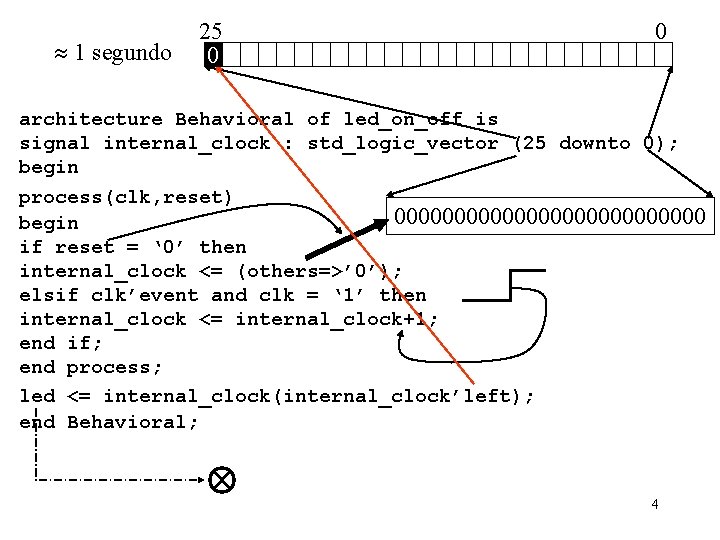

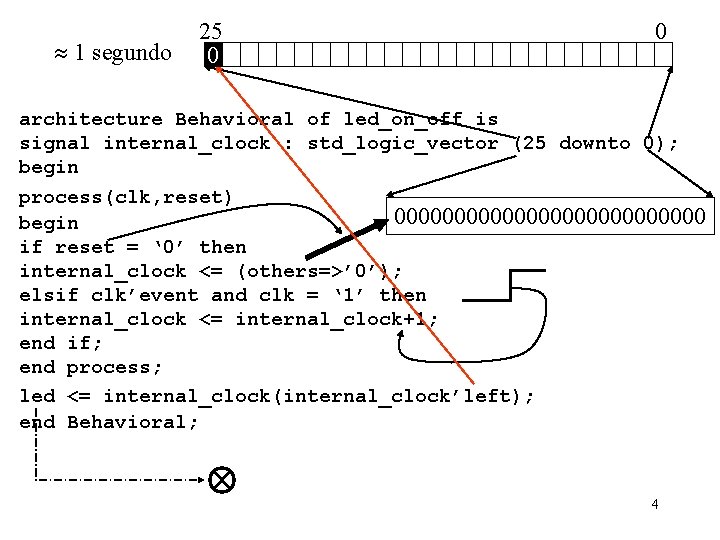

1 segundo 25 10 0 architecture Behavioral of led_on_off is signal internal_clock : std_logic_vector (25 downto 0); begin process(clk, reset) 0000000000000 begin if reset = ‘ 0’ then internal_clock <= (others=>’ 0’); elsif clk’event and clk = ‘ 1’ then internal_clock <= internal_clock+1; end if; end process; led <= internal_clock(internal_clock’left); end Behavioral; 4

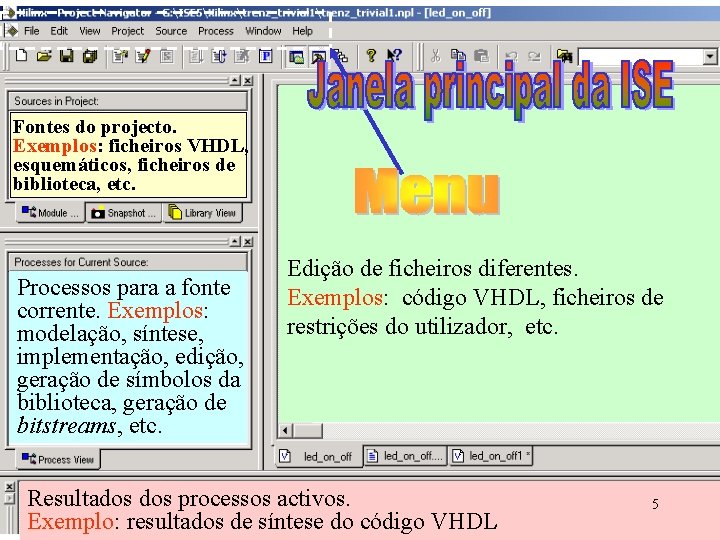

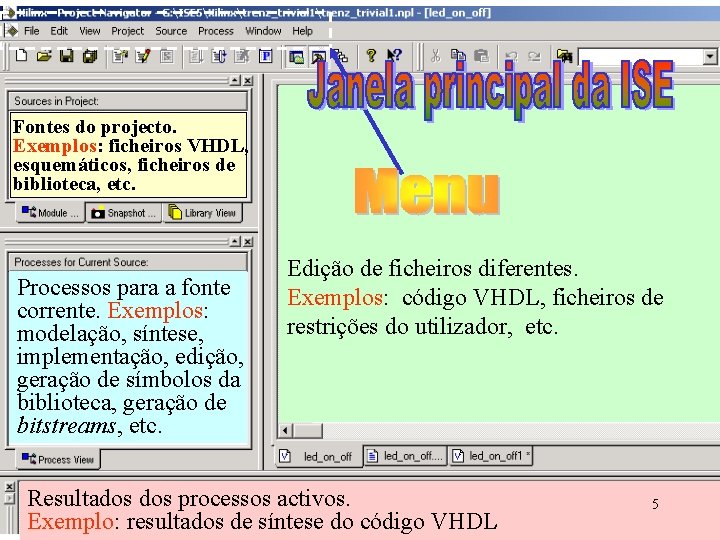

Fontes do projecto. Exemplos: ficheiros VHDL, esquemáticos, ficheiros de biblioteca, etc. Processos para a fonte corrente. Exemplos: modelação, síntese, implementação, edição, geração de símbolos da biblioteca, geração de bitstreams, etc. Edição de ficheiros diferentes. Exemplos: código VHDL, ficheiros de restrições do utilizador, etc. Resultados processos activos. Exemplo: resultados de síntese do código VHDL 5

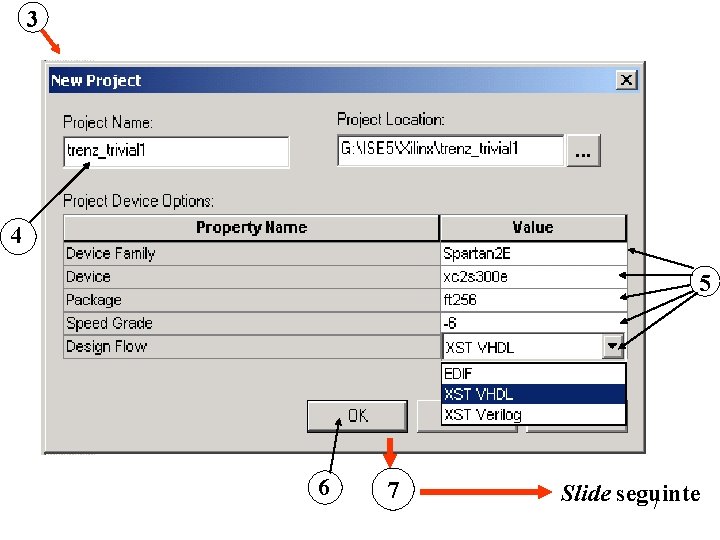

Comece aqui 1 2 3 6 Slide seguinte

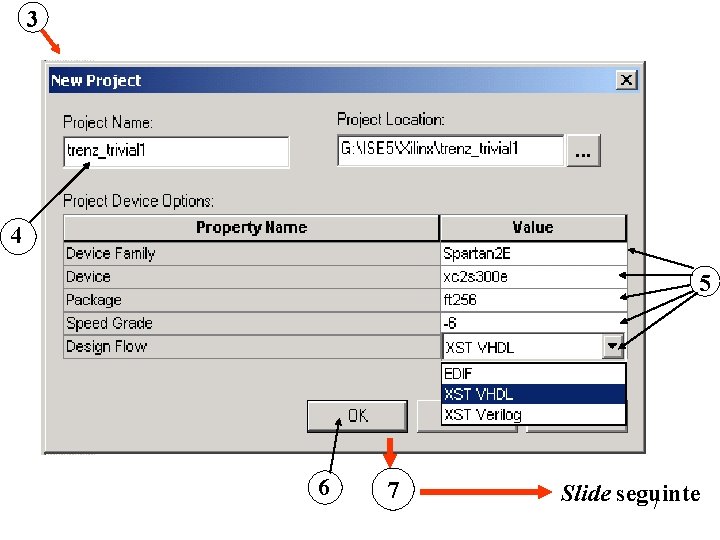

3 4 5 6 7 Slide seguinte 7

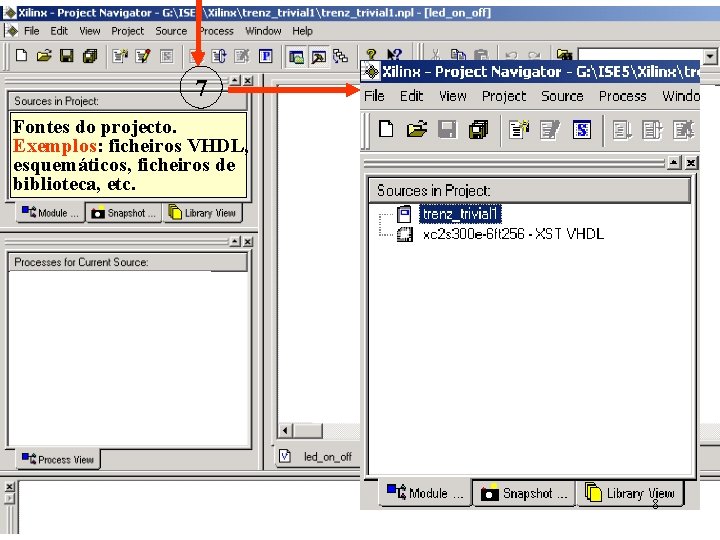

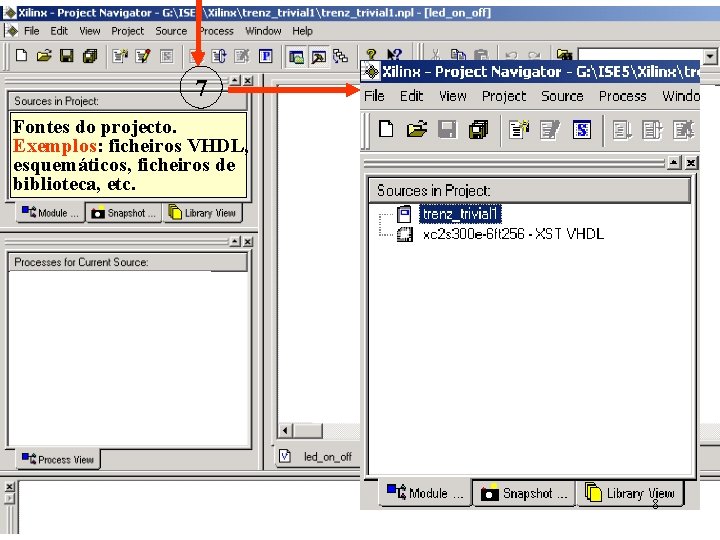

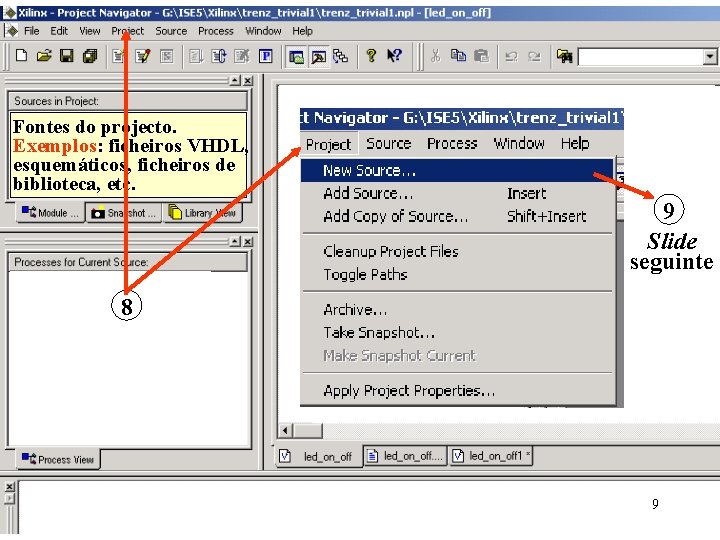

7 Fontes do projecto. Exemplos: ficheiros VHDL, esquemáticos, ficheiros de biblioteca, etc. 8

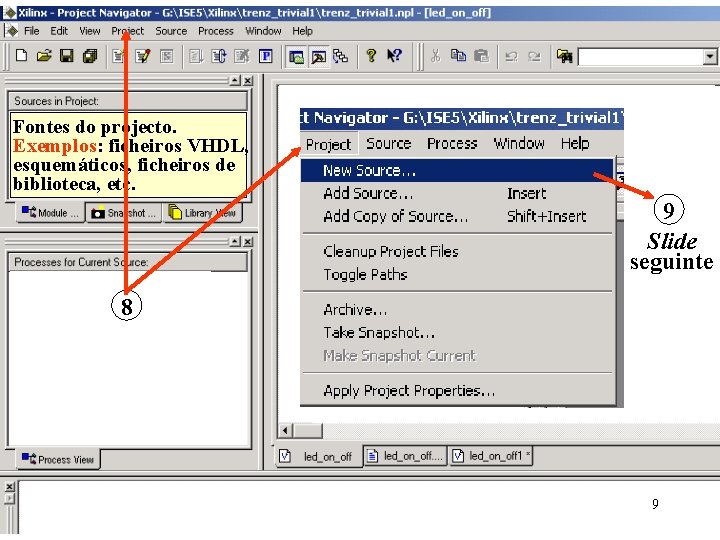

Fontes do projecto. Exemplos: ficheiros VHDL, esquemáticos, ficheiros de biblioteca, etc. 9 Slide seguinte 8 9

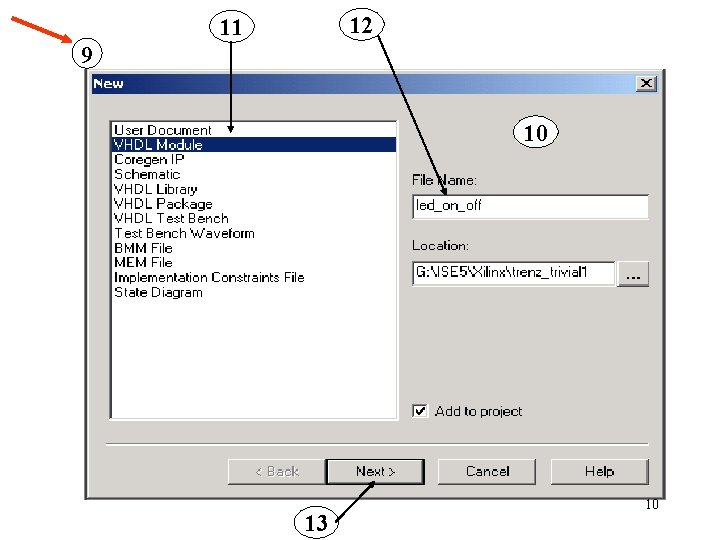

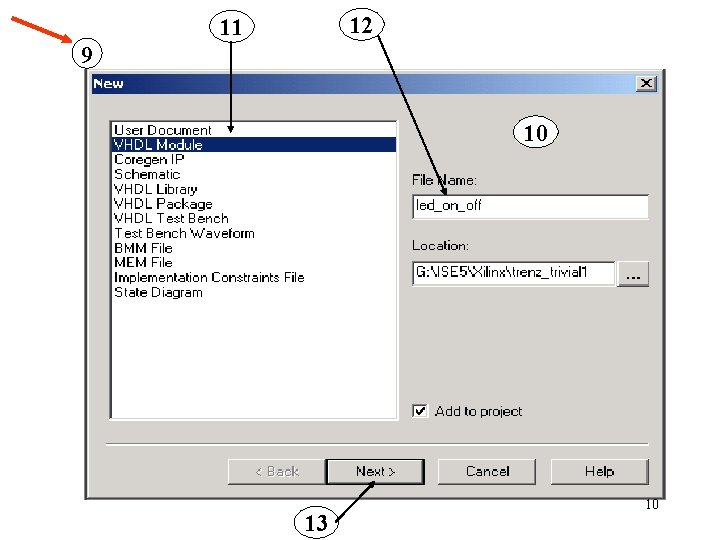

12 11 9 10 13 10

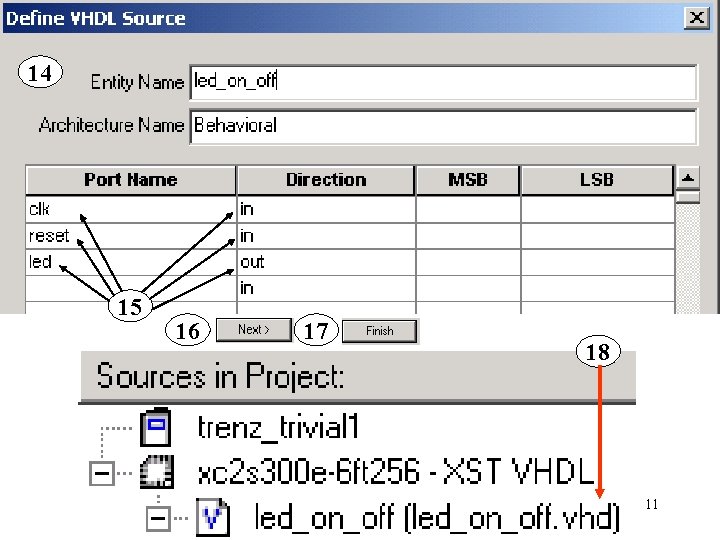

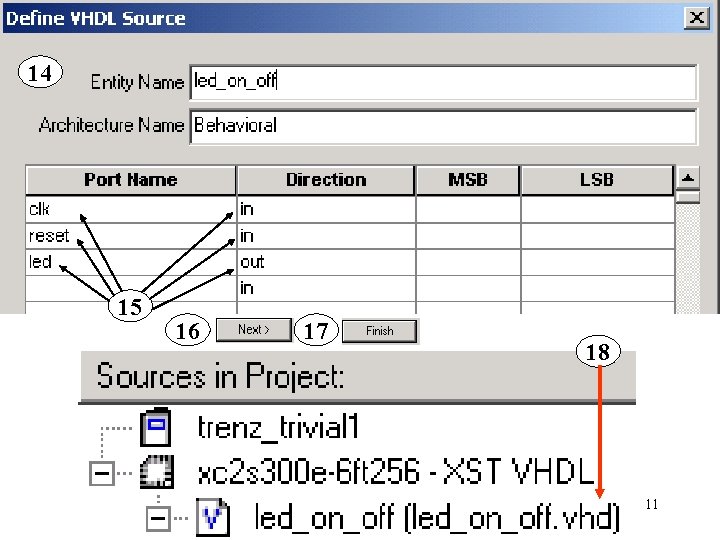

14 15 16 17 18 11

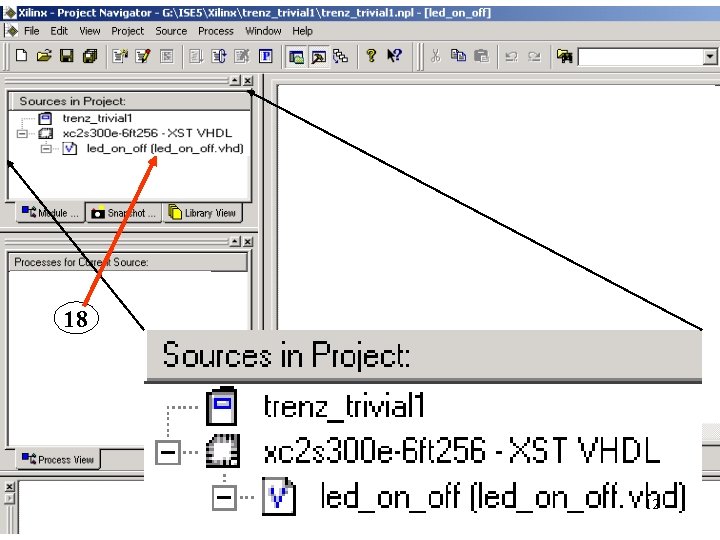

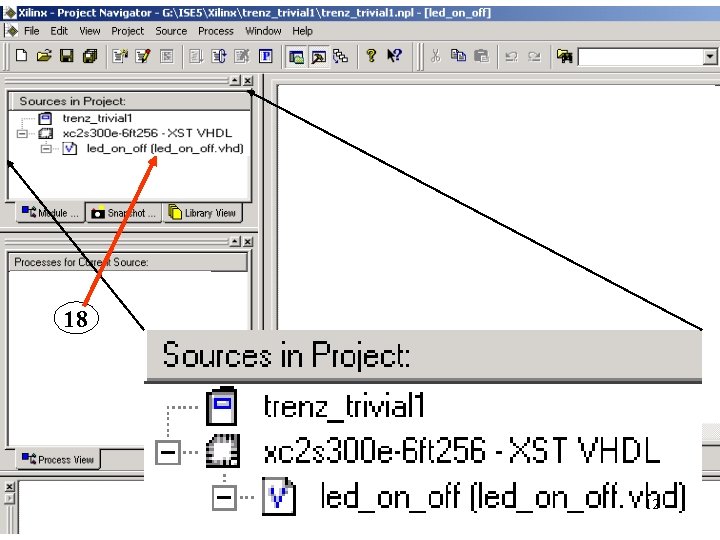

18 12

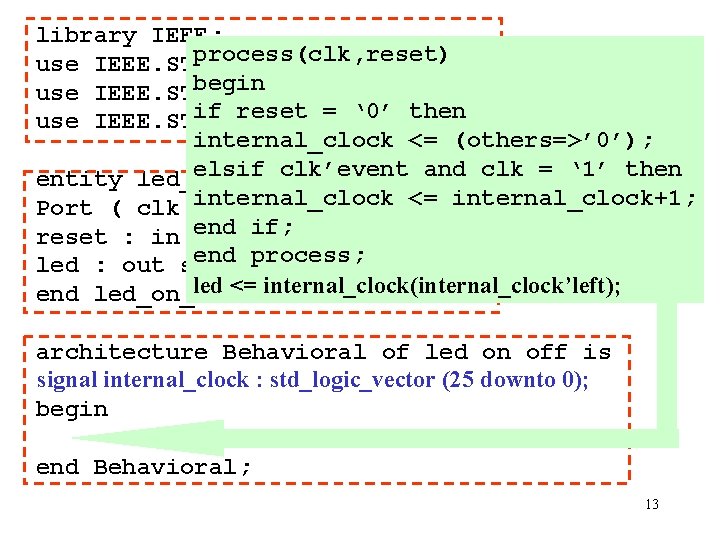

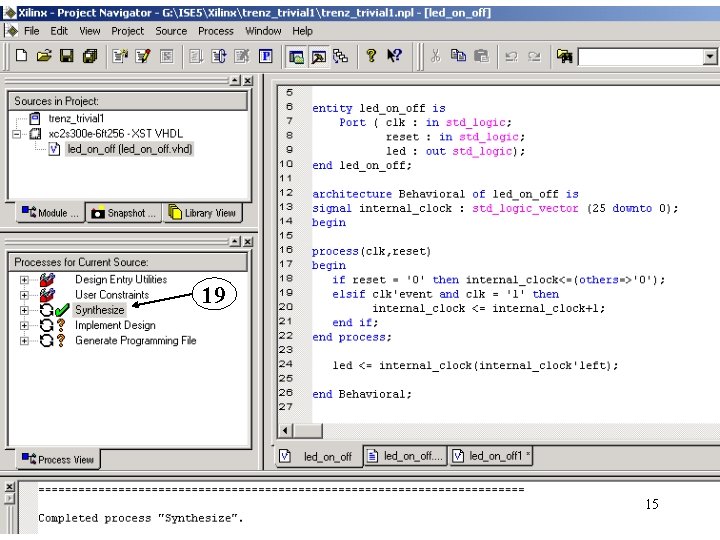

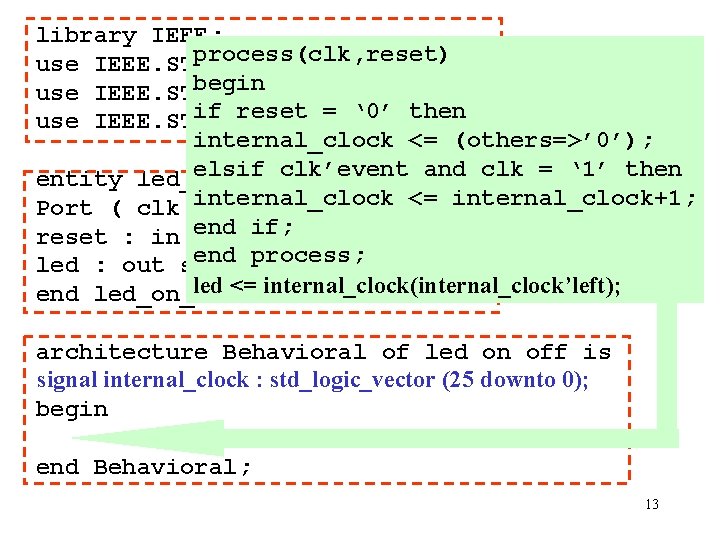

library IEEE; process(clk, reset) use IEEE. STD_LOGIC_1164. ALL; begin use IEEE. STD_LOGIC_ARITH. ALL; if reset = ‘ 0’ then use IEEE. STD_LOGIC_UNSIGNED. ALL; internal_clock <= (others=>’ 0’); elsif clk’event and clk = ‘ 1’ then entity led_on_off is Port ( clk internal_clock : in std_logic; <= internal_clock+1; if; reset : in end std_logic; end process; led : out std_logic); led <= internal_clock(internal_clock’left); end led_on_off; architecture Behavioral of led_on_off is signal internal_clock : std_logic_vector (25 downto 0); begin end Behavioral; 13

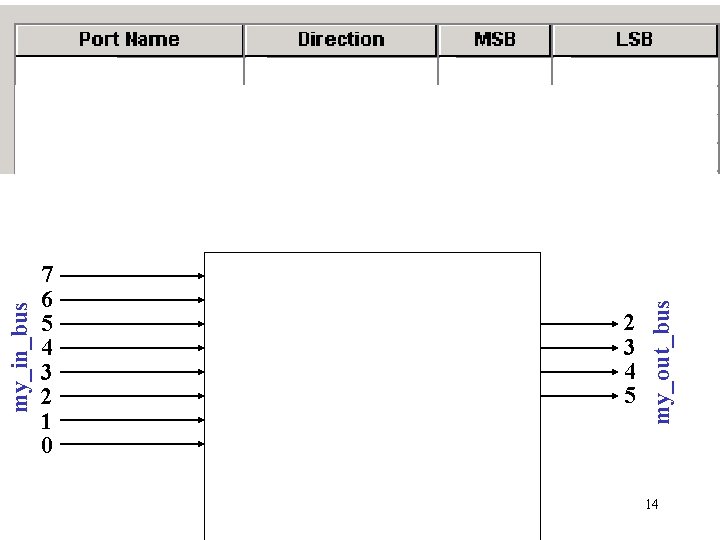

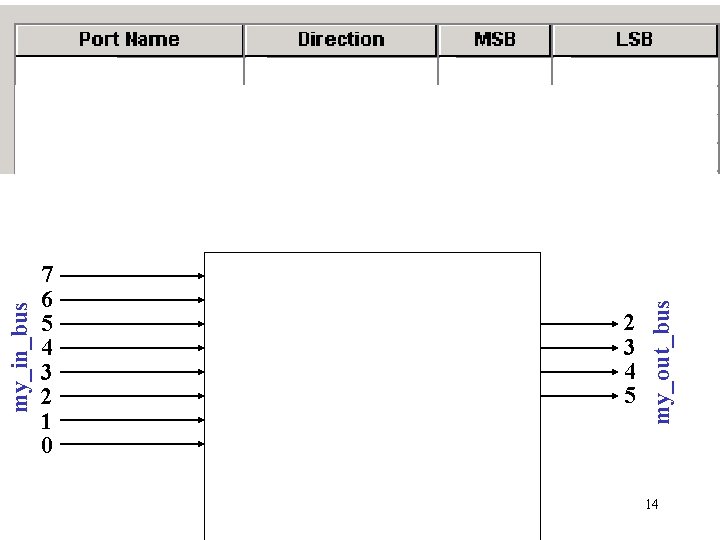

my_in_bus 7 6 5 4 3 2 1 0 my_out_bus 2 3 4 5 14

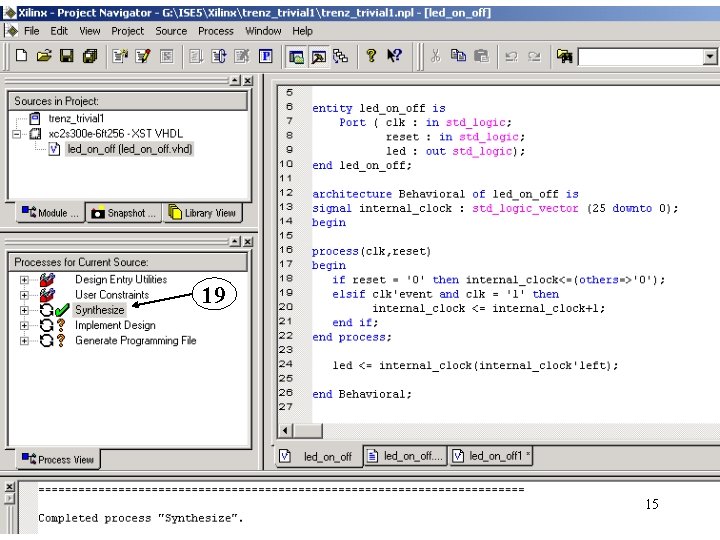

19 15

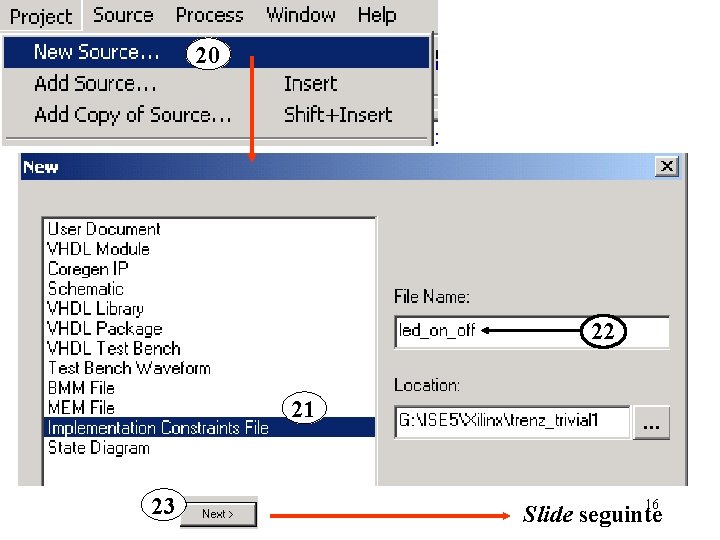

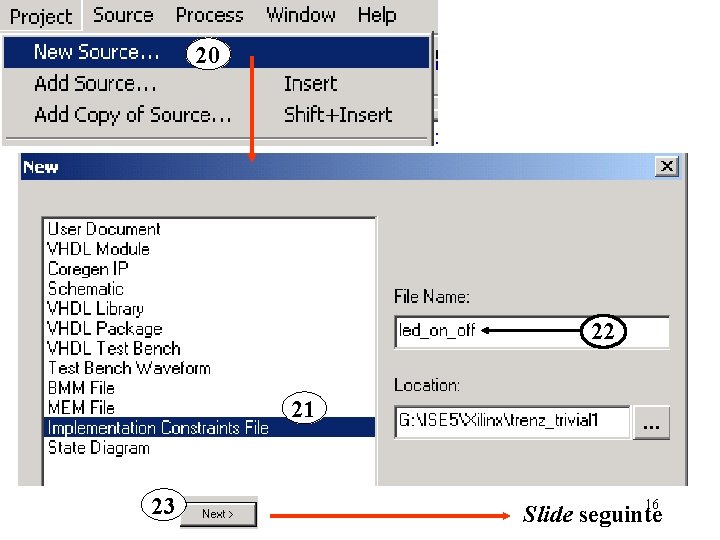

20 22 21 23 16 Slide seguinte

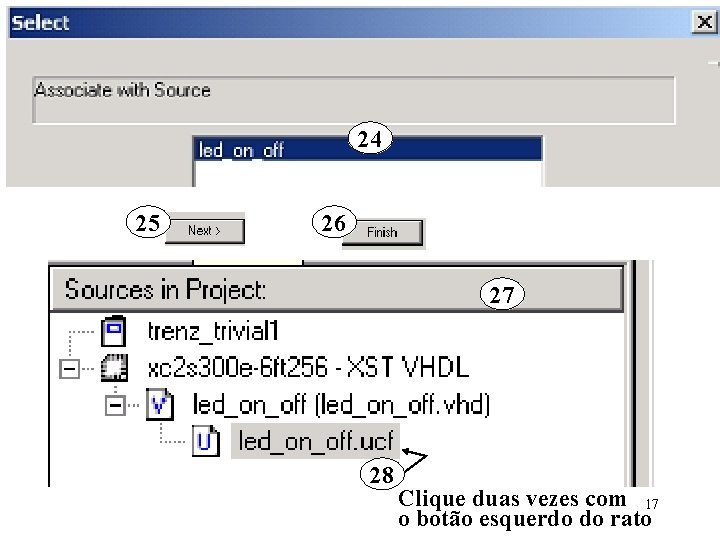

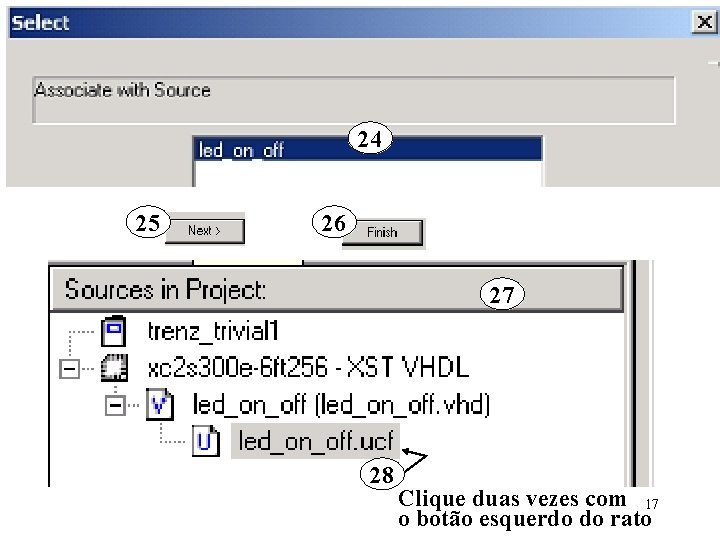

24 25 26 27 28 Clique duas vezes com 17 o botão esquerdo do rato

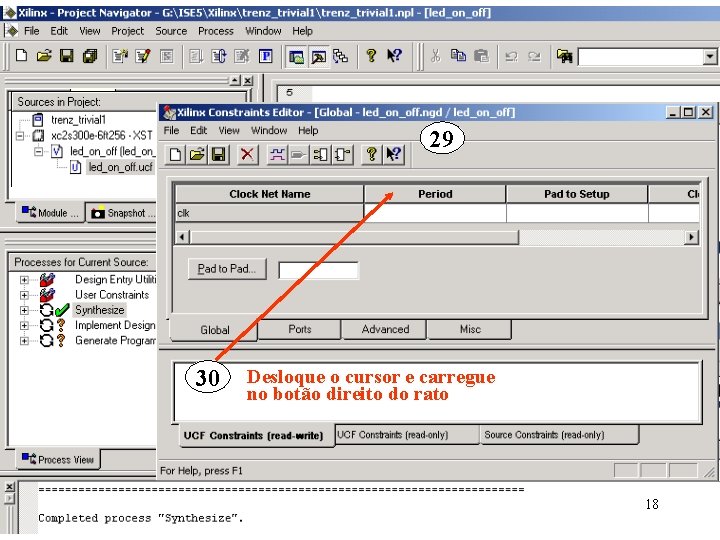

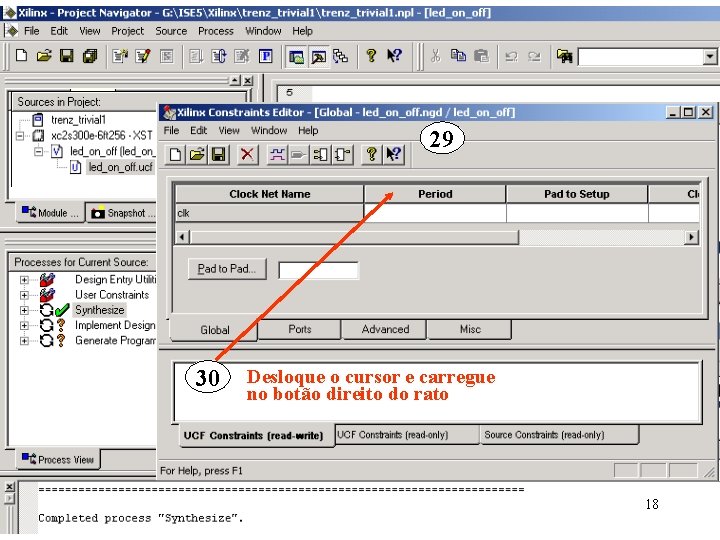

29 30 Desloque o cursor e carregue no botão direito do rato 18

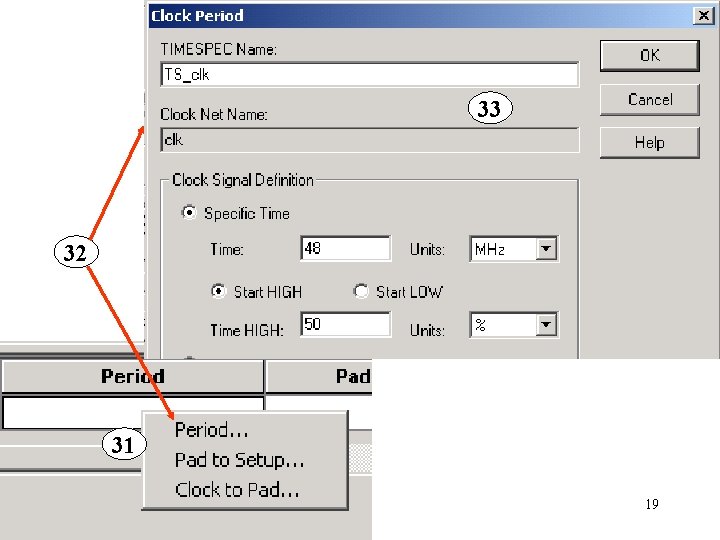

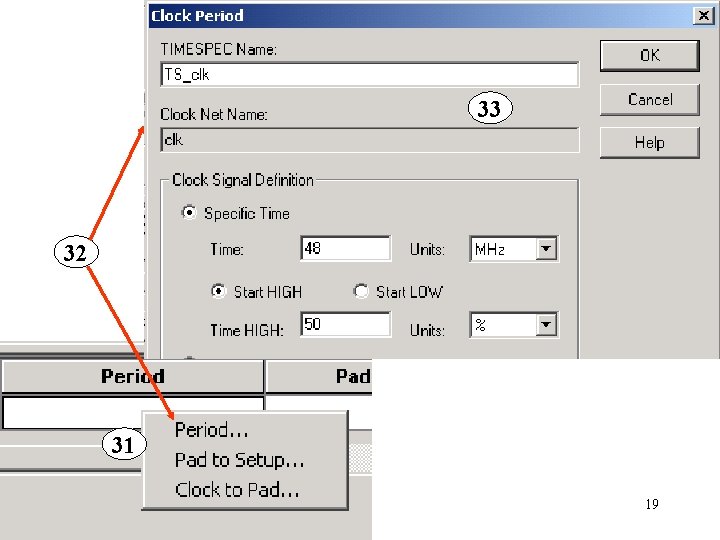

33 32 31 19

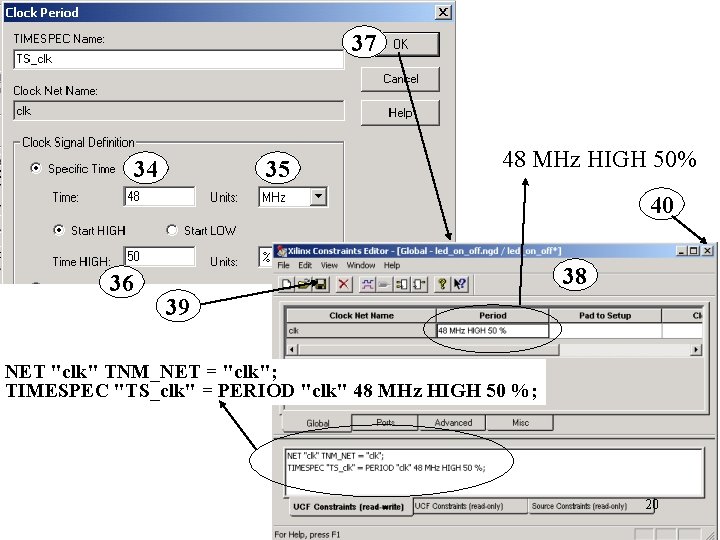

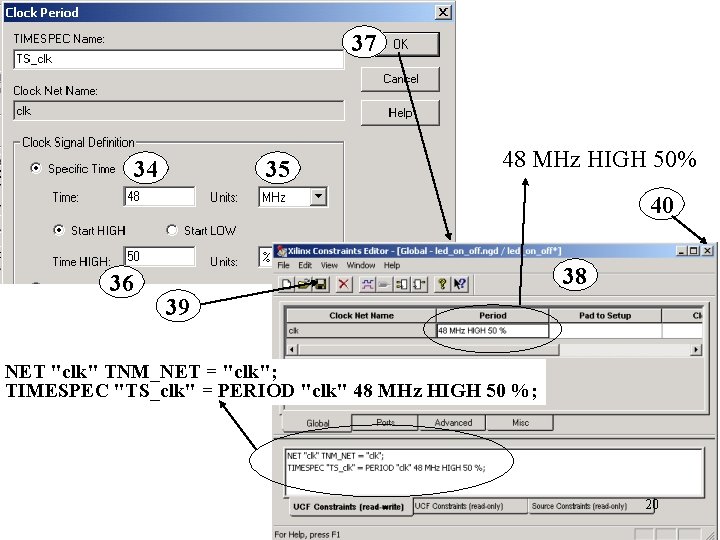

37 34 35 48 MHz HIGH 50% 40 36 38 39 NET "clk" TNM_NET = "clk"; TIMESPEC "TS_clk" = PERIOD "clk" 48 MHz HIGH 50 %; 20

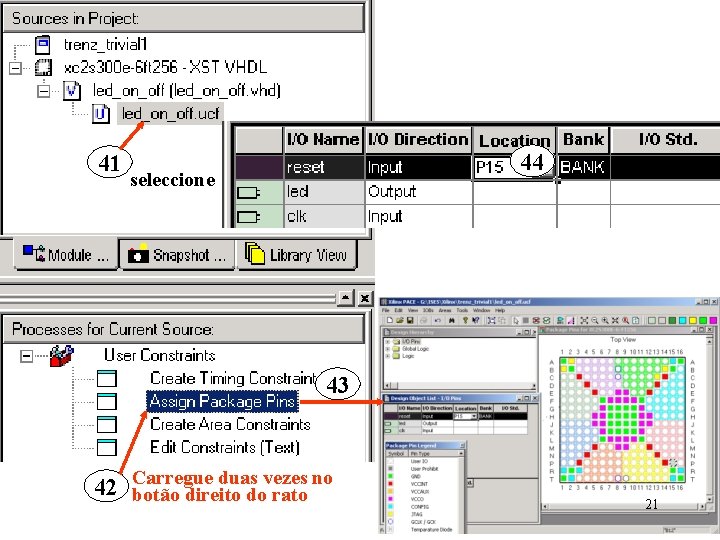

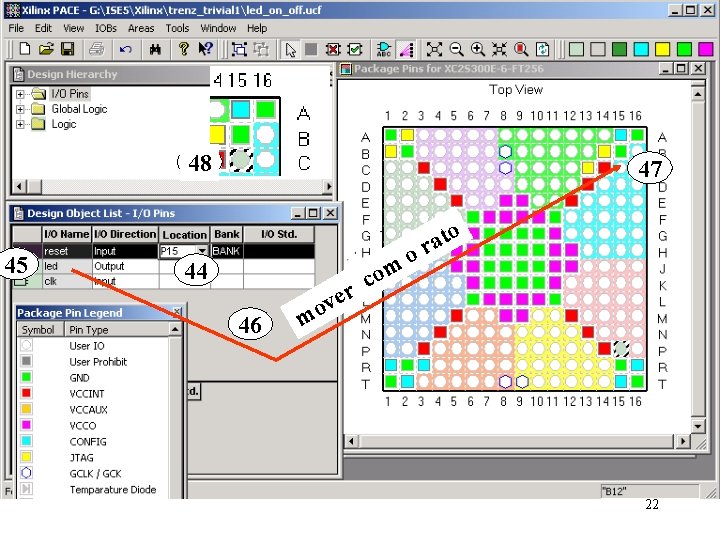

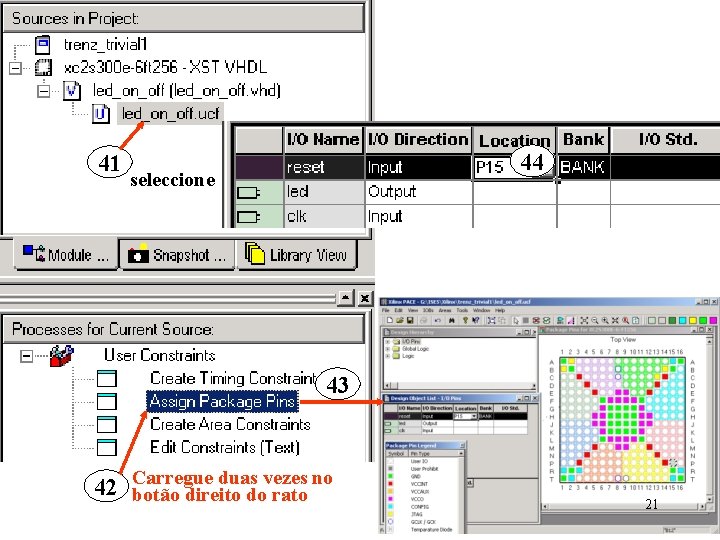

41 44 seleccione 43 duas vezes no 42 Carregue botão direito do rato 21

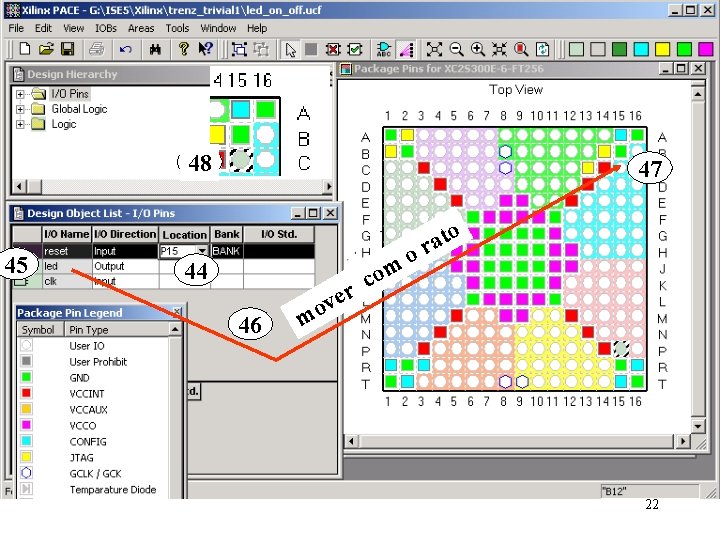

48 45 47 44 46 om c er v mo o o t a r 22

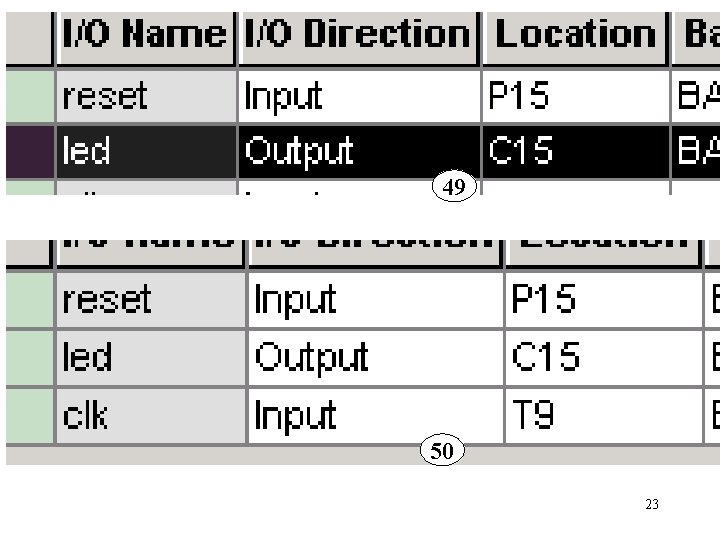

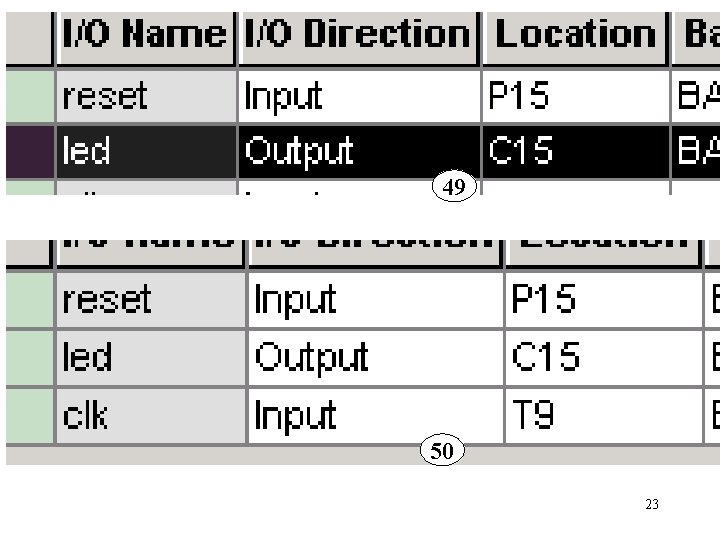

49 50 23

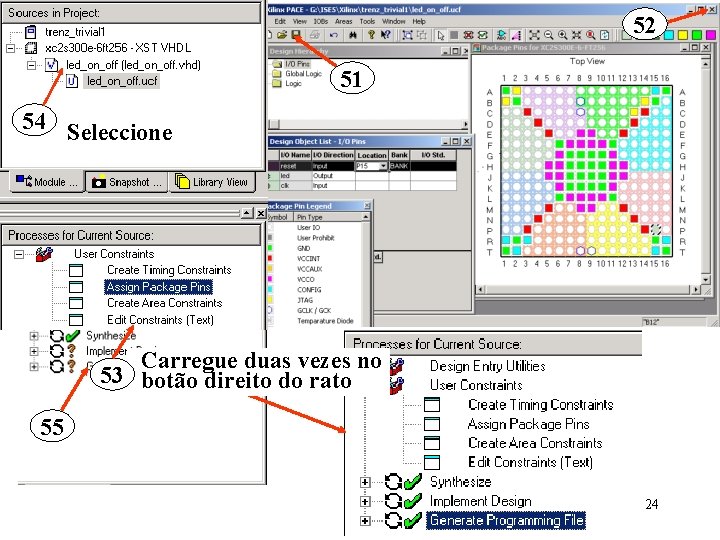

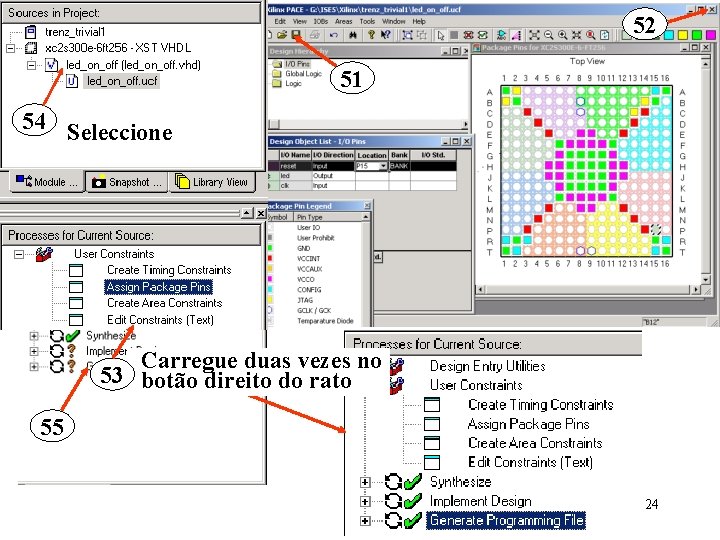

52 51 54 Seleccione Carregue duas vezes no 53 botão direito do rato 55 24

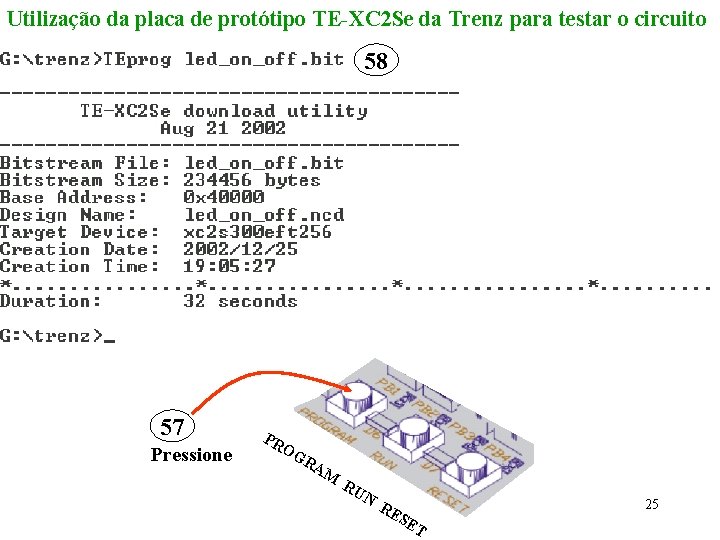

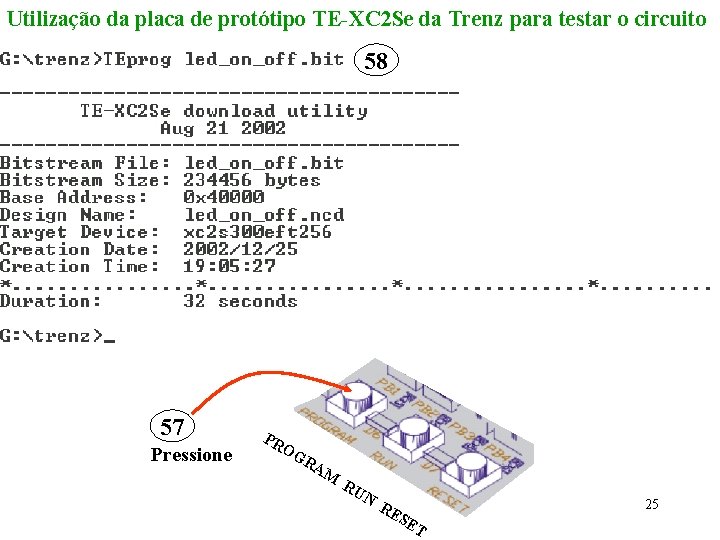

Utilização da placa de protótipo TE-XC 2 Se da Trenz para testar o circuito 58 57 Pressione PR OG RA M RU N RE 25 SE T

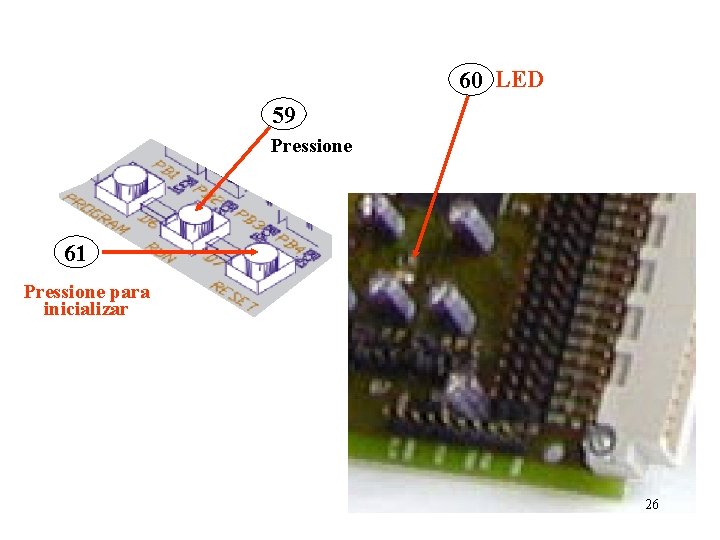

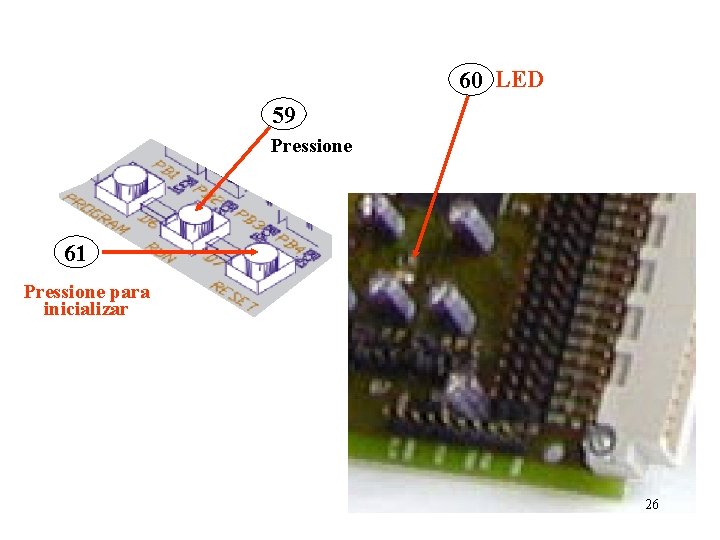

60 LED 59 Pressione 61 Pressione para inicializar 26