1 ECE 1352 F Topic Presentation ADPLL By

1 ECE 1352 F – Topic Presentation - ADPLL By Selvakkumaran S

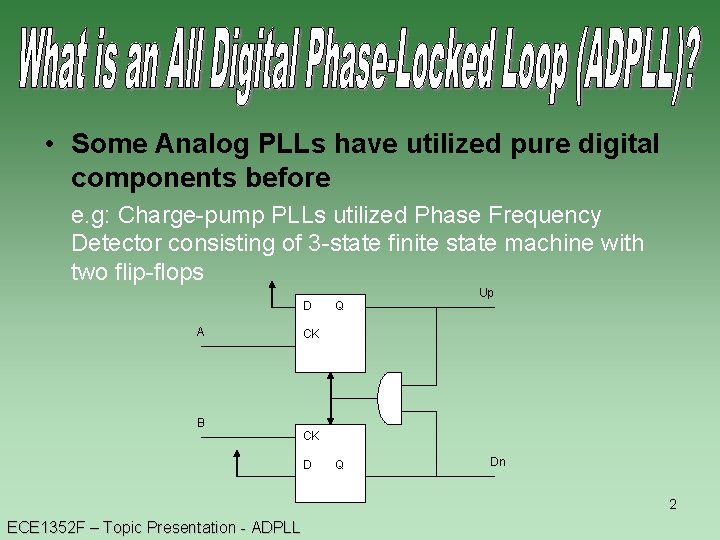

• Some Analog PLLs have utilized pure digital components before e. g: Charge-pump PLLs utilized Phase Frequency Detector consisting of 3 -state finite state machine with two flip-flops D A B Q Up CK CK D Q Dn 2 ECE 1352 F – Topic Presentation - ADPLL

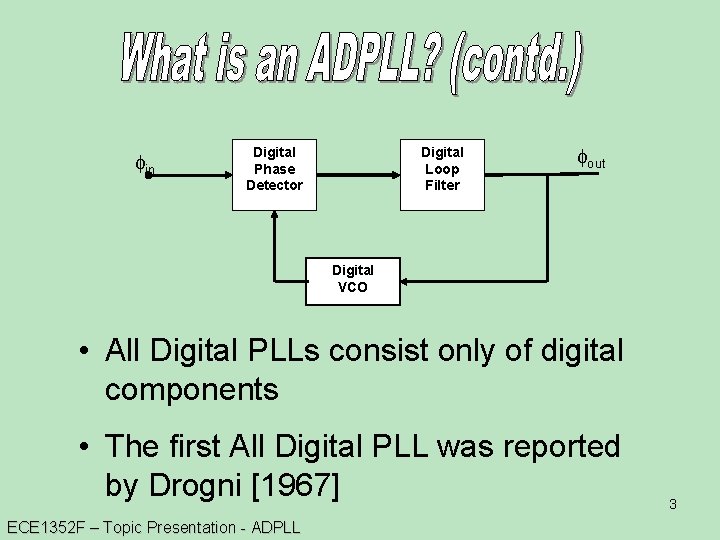

fin Digital Phase Detector Digital Loop Filter fout Digital VCO • All Digital PLLs consist only of digital components • The first All Digital PLL was reported by Drogni [1967] ECE 1352 F – Topic Presentation - ADPLL 3

Why All Digital PLL? Improvements in digital designs *Progress in increasing *Progress in reducing • Performance • Size • Speed • Cost • Reliability * Portability/ Reusability * Programmability * Testability ECE 1352 F – Topic Presentation - ADPLL 4

Why All Digital PLL? Solves Problems Related to Analog PLLs(APLL) • • Sensitivity to DC Drifts Component Saturations Difficulties building higher order loops Initial calibration and periodic adjustments 5 ECE 1352 F – Topic Presentation - ADPLL

Issues of ADPLLs versus APLLs • Limitation on operating speed • Chip area • Power Consumption • Worse jitter performance due to D/A converter resolution limitation * Note: The above issues need further exploration[7] as some papers have reported better ADPLL performance. 6 ECE 1352 F – Topic Presentation - ADPLL

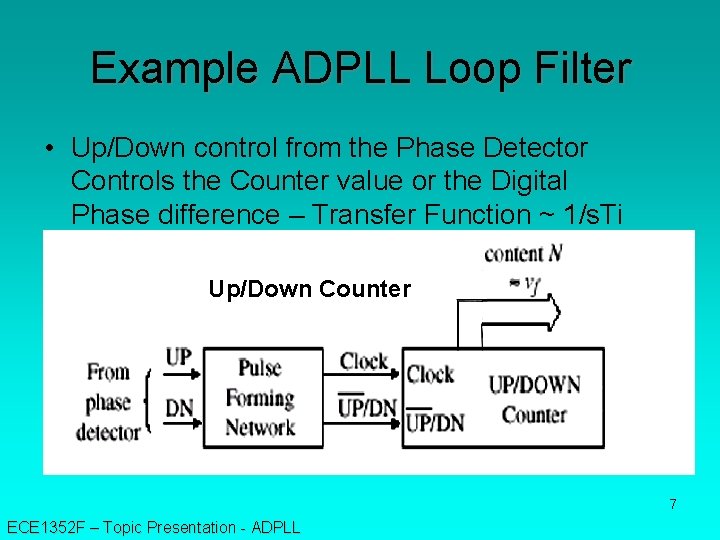

Example ADPLL Loop Filter • Up/Down control from the Phase Detector Controls the Counter value or the Digital Phase difference – Transfer Function ~ 1/s. Ti Up/Down Counter 7 ECE 1352 F – Topic Presentation - ADPLL

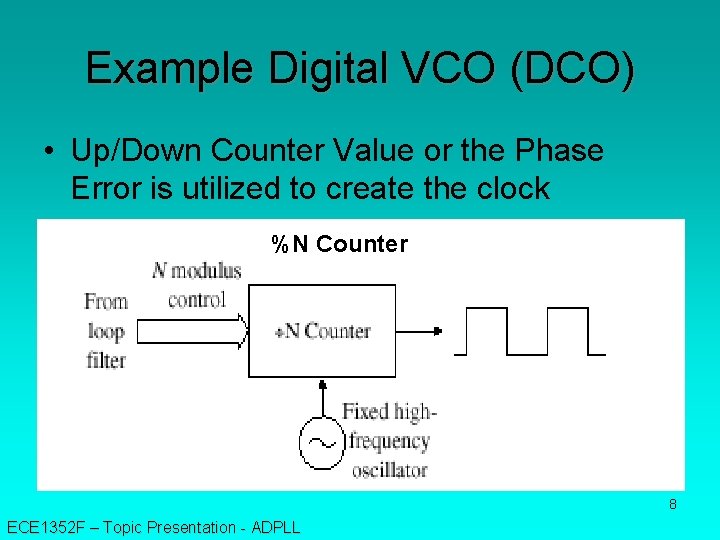

Example Digital VCO (DCO) • Up/Down Counter Value or the Phase Error is utilized to create the clock %N Counter 8 ECE 1352 F – Topic Presentation - ADPLL

![ADPLL Design Analysis Z-transform technique [5, 6] • z domain transfer function • Solutions ADPLL Design Analysis Z-transform technique [5, 6] • z domain transfer function • Solutions](http://slidetodoc.com/presentation_image_h2/84d48c54c776297957ad77b8840113ba/image-9.jpg)

ADPLL Design Analysis Z-transform technique [5, 6] • z domain transfer function • Solutions within the unit circle ensures stability 9 ECE 1352 F – Topic Presentation - ADPLL

![ADPLL Design Example 1[2] 10 ECE 1352 F – Topic Presentation - ADPLL ADPLL Design Example 1[2] 10 ECE 1352 F – Topic Presentation - ADPLL](http://slidetodoc.com/presentation_image_h2/84d48c54c776297957ad77b8840113ba/image-10.jpg)

ADPLL Design Example 1[2] 10 ECE 1352 F – Topic Presentation - ADPLL

![3. 3 V Supply Process Results [2] 0. 35 m 0. 25 m Approach 3. 3 V Supply Process Results [2] 0. 35 m 0. 25 m Approach](http://slidetodoc.com/presentation_image_h2/84d48c54c776297957ad77b8840113ba/image-11.jpg)

3. 3 V Supply Process Results [2] 0. 35 m 0. 25 m Approach AD Cell Based 0. 60 m Analog Semi(1. 9 V) digital 0. 60 m 0. 50 m AD Cell Based All. Digital Area(mm 2) 0. 71 0. 09 0. 83 2. 75 0. 71 Power(m. W) 100 25 105 315 39. 6 @400 MHz @800 MHz @100 MHz <16 <25 <50 @500 MHz Max. lock <46 Time(cycles) <720 Range MHz 45 -510 8. 5 -660 300 -800 360 -800 50 -550 Output Jitter 70 ps 149 ps 80 ps 60 ps 125 ps 11

![Results[2] • • • Shorter Locking in time Better Jitter Performance Better Portability (cell-based Results[2] • • • Shorter Locking in time Better Jitter Performance Better Portability (cell-based](http://slidetodoc.com/presentation_image_h2/84d48c54c776297957ad77b8840113ba/image-12.jpg)

Results[2] • • • Shorter Locking in time Better Jitter Performance Better Portability (cell-based design) Reduced circuit complexity Reduced Design Time Note: Some other papers have reported ADPLLs area and power statistics better than APLLs 12 ECE 1352 F – Topic Presentation - ADPLL

![ADPLL Design Example 2[6] A Second order ADPLL H(z)= C 2(Z-1)+C 1 (Z-1)2+C 2(Z-1)+C ADPLL Design Example 2[6] A Second order ADPLL H(z)= C 2(Z-1)+C 1 (Z-1)2+C 2(Z-1)+C](http://slidetodoc.com/presentation_image_h2/84d48c54c776297957ad77b8840113ba/image-13.jpg)

ADPLL Design Example 2[6] A Second order ADPLL H(z)= C 2(Z-1)+C 1 (Z-1)2+C 2(Z-1)+C 1 H(S)= 2 hwn. S + wn 2 S 2 + 2 hwn. S + wn 2 13 ECE 1352 F – Topic Presentation - ADPLL

![Acquisition Behaviour[6] *ADPLL shows a better performance in terms of the acquisition time 14 Acquisition Behaviour[6] *ADPLL shows a better performance in terms of the acquisition time 14](http://slidetodoc.com/presentation_image_h2/84d48c54c776297957ad77b8840113ba/image-14.jpg)

Acquisition Behaviour[6] *ADPLL shows a better performance in terms of the acquisition time 14 ECE 1352 F – Topic Presentation - ADPLL

![Phase Jitter Behaviour[6] 15 ECE 1352 F – Topic Presentation - ADPLL Phase Jitter Behaviour[6] 15 ECE 1352 F – Topic Presentation - ADPLL](http://slidetodoc.com/presentation_image_h2/84d48c54c776297957ad77b8840113ba/image-15.jpg)

Phase Jitter Behaviour[6] 15 ECE 1352 F – Topic Presentation - ADPLL

![Results[6] • • • Larger lock-in range (~4. 5 x APLL) Larger Hold-in Range Results[6] • • • Larger lock-in range (~4. 5 x APLL) Larger Hold-in Range](http://slidetodoc.com/presentation_image_h2/84d48c54c776297957ad77b8840113ba/image-16.jpg)

Results[6] • • • Larger lock-in range (~4. 5 x APLL) Larger Hold-in Range than APLL Smaller RMS Phase Jitter Digital approach to design Software configurability/ programmability 16 ECE 1352 F – Topic Presentation - ADPLL

• • • Stability Fast Acquisition Time Large hold-in range Large lock-in range Better phase jitter performance No need for off-chip components Technology portability Testability Programmability Simpler design and faster simulation ECE 1352 F – Topic Presentation - ADPLL 17

Future of ADPLL • Digital IP (Intellectual Property) vendors are already creating ADPLL products • As technology progress happens skew problems will require ADPLLs within the design components to synchronize the clock signal between various blocks 18 ECE 1352 F – Topic Presentation - ADPLL

1. Behzad Razavi, Design of Analog CMOS Integrated Circuits, Mc. Graw-Hill, 2001 2. Ching-Che Chung and Chen-Yi Lee, “An All-Digital Phase. Locked Loop for High Speed Clock Generation, IEEE J. Solid. State Circuits, vol 38, No. 2, pp 347 -351, February 2003 3. Thomas Olsson and Peter Nilsson, “A Digitally Controlled PLL Using a Standard Cell Library”, Lund University, Sweden, www. es. lth. se/home/ton 4. Roland E. Best, Phase-Locked Loops, Design, Simulation and Applications, 4 th Ed, Mc. Graw-Hill, 1999 (Chapter 4, pp 177228) 5. Venceslav F, Kroupa, Phase Lock Loops and Frequency Synthesis, Wiley, 2003, (Chapter 10, pp 231 -254) 19 ECE 1352 F – Topic Presentation - ADPLL

6. 7. Y. R. Shayan, T. Le-Ngoc, “All Digital phase-locked loop: concepts, design and applications”, IEE Procedings, Vol. 136, Pt. F. No. 1, pp 53 -56, February 1989 Dao-Long Chen, “A Power and Area Efficient CMOS Clock/Data Recovery Circuit for High-Speed Serial Interfaces, IEEE J. of Solid-state Circuits, Vol. 31, No 8, pp 1170 -1176, August 1996 20 ECE 1352 F – Topic Presentation - ADPLL

21

- Slides: 21