1 D DCT Verilog HDL Lab H C

1 -D DCT 專題 Verilog HDL & Lab H. C. Chen / NUU, Taiwan

1 -D DCT 專題 l 分散式算術 (Distributed Arithmetic: DA) l 1 -D DCT Design Verilog HDL & Lab H. C. Chen / NUU, Taiwan

分散式算術 Distributed Arithmetic (DA) Verilog HDL & Lab H. C. Chen / NUU, Taiwan

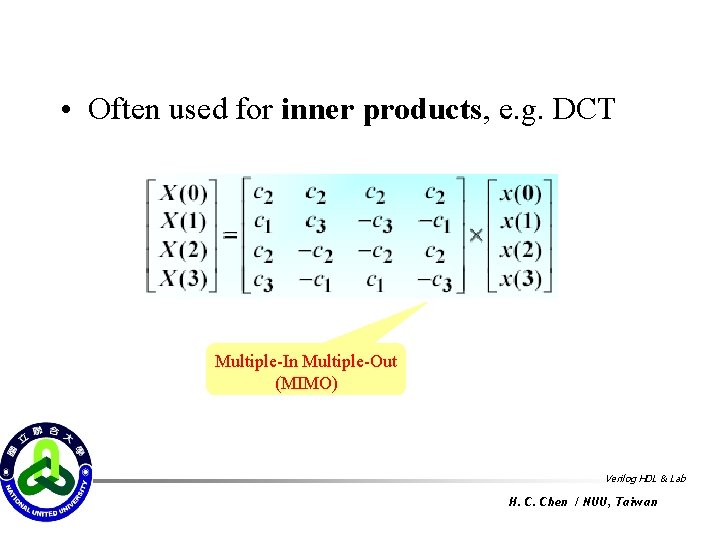

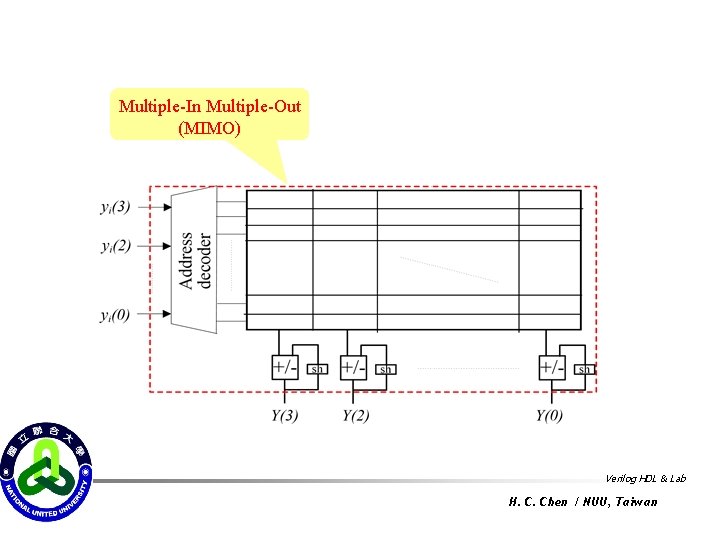

• Often used for inner products, e. g. DCT Multiple-In Multiple-Out (MIMO) Verilog HDL & Lab H. C. Chen / NUU, Taiwan

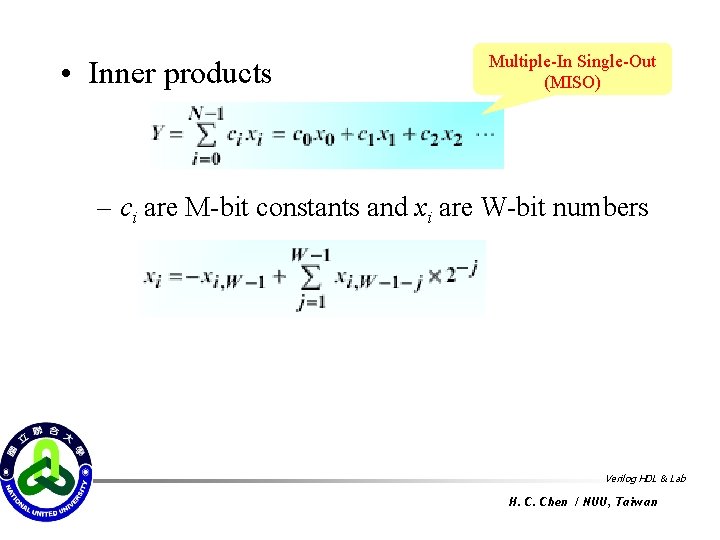

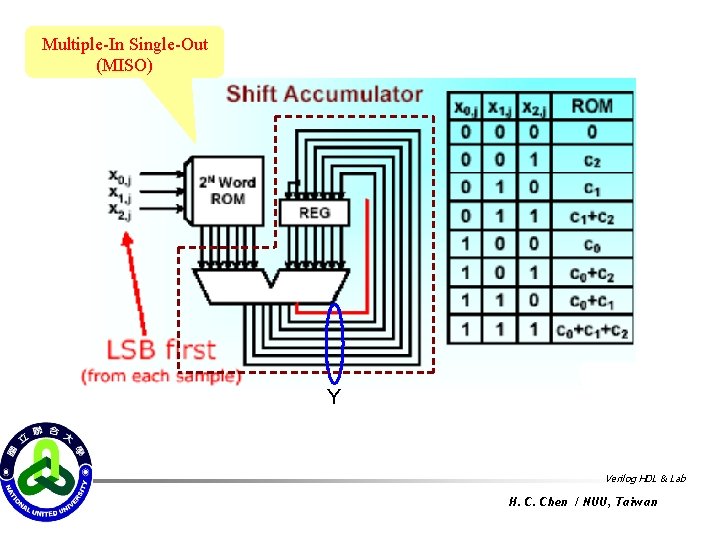

• Inner products Multiple-In Single-Out (MISO) – ci are M-bit constants and xi are W-bit numbers Verilog HDL & Lab H. C. Chen / NUU, Taiwan

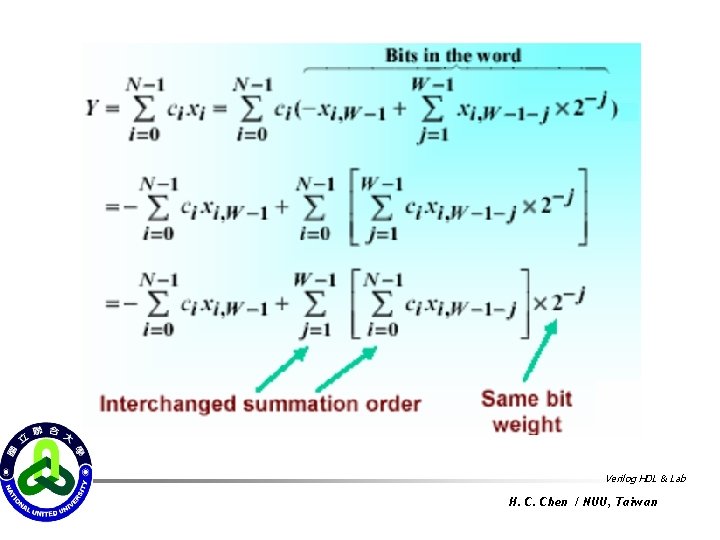

Verilog HDL & Lab H. C. Chen / NUU, Taiwan

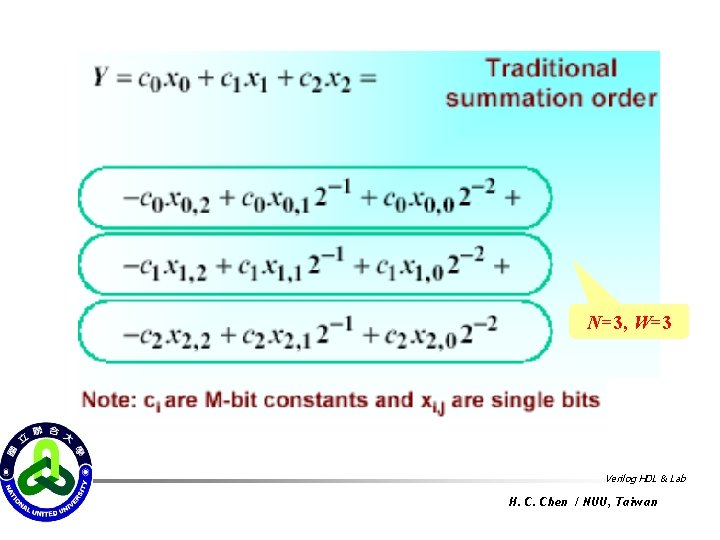

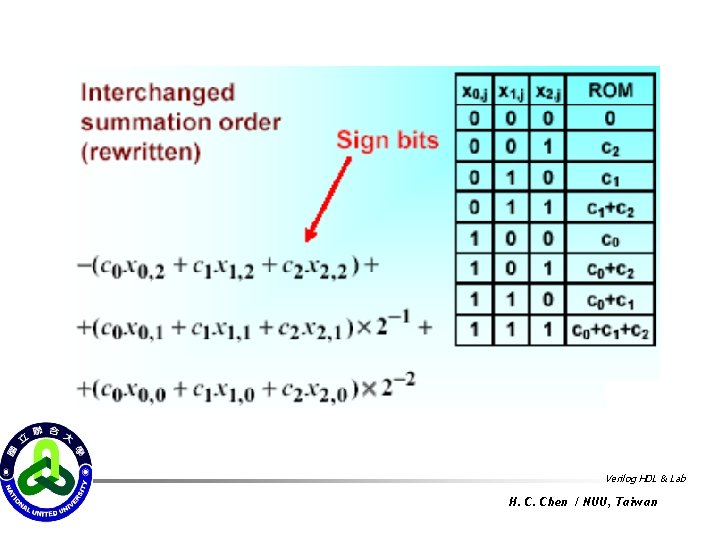

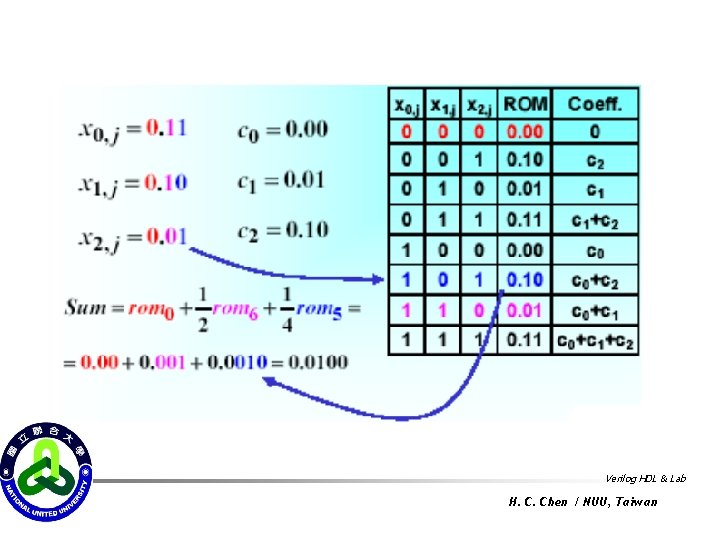

N=3, W=3 Verilog HDL & Lab H. C. Chen / NUU, Taiwan

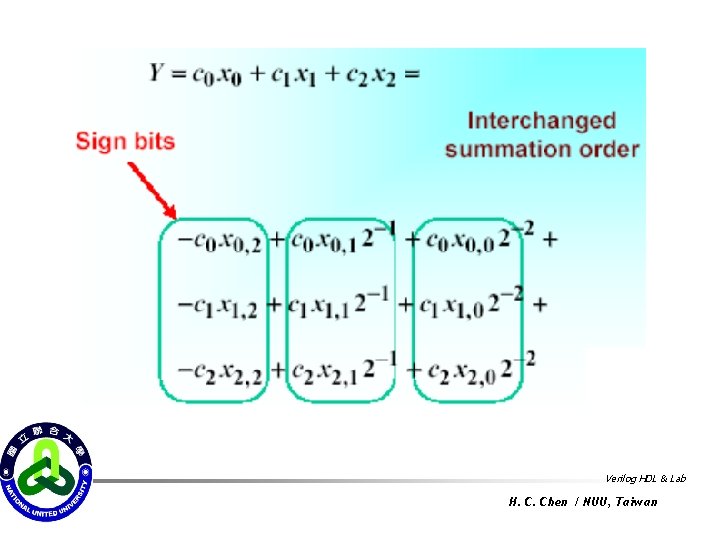

Verilog HDL & Lab H. C. Chen / NUU, Taiwan

Verilog HDL & Lab H. C. Chen / NUU, Taiwan

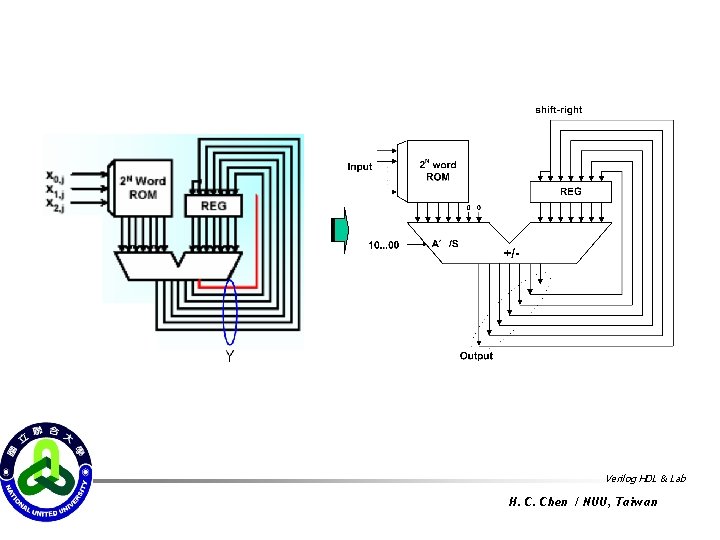

Multiple-In Single-Out (MISO) Y Verilog HDL & Lab H. C. Chen / NUU, Taiwan

Multiple-In Multiple-Out (MIMO) Verilog HDL & Lab H. C. Chen / NUU, Taiwan

Verilog HDL & Lab H. C. Chen / NUU, Taiwan

Verilog HDL & Lab H. C. Chen / NUU, Taiwan

1 -D DCT Design Verilog HDL & Lab H. C. Chen / NUU, Taiwan

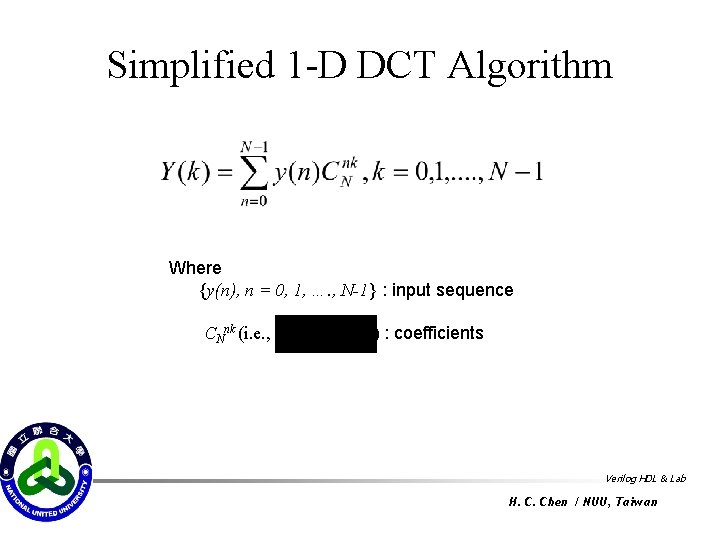

Simplified 1 -D DCT Algorithm Where {y(n), n = 0, 1, …. , N-1} : input sequence CNnk (i. e. , ) : coefficients Verilog HDL & Lab H. C. Chen / NUU, Taiwan

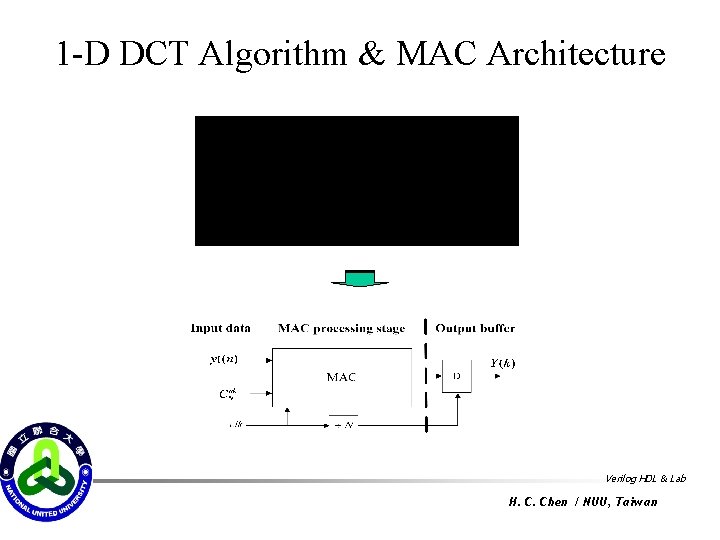

1 -D DCT Algorithm & MAC Architecture Verilog HDL & Lab H. C. Chen / NUU, Taiwan

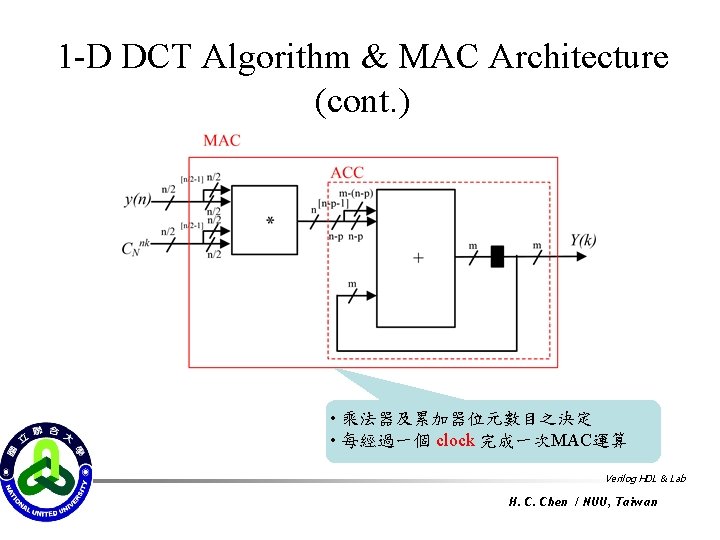

1 -D DCT Algorithm & MAC Architecture (cont. ) • 乘法器及累加器位元數目之決定 • 每經過一個 clock 完成一次MAC運算 Verilog HDL & Lab H. C. Chen / NUU, Taiwan

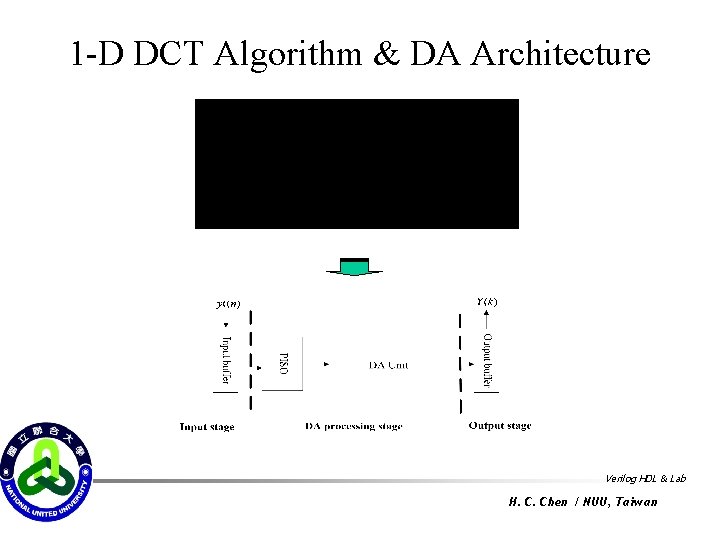

1 -D DCT Algorithm & DA Architecture Verilog HDL & Lab H. C. Chen / NUU, Taiwan

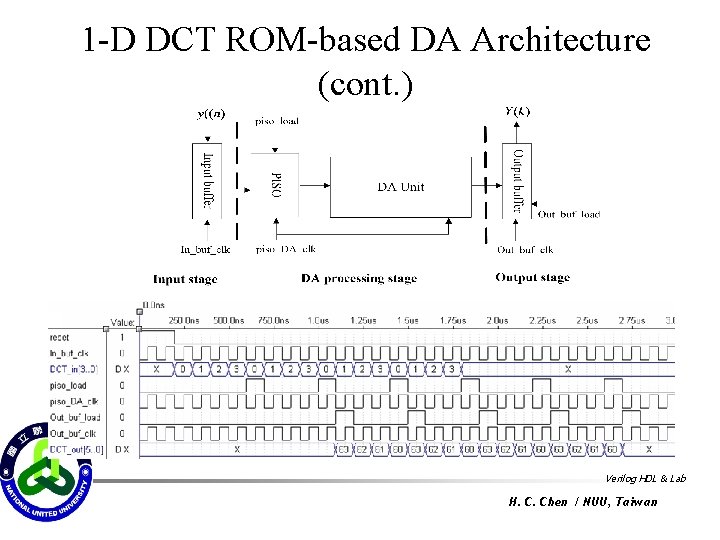

1 -D DCT ROM-based DA Architecture (cont. ) Verilog HDL & Lab H. C. Chen / NUU, Taiwan

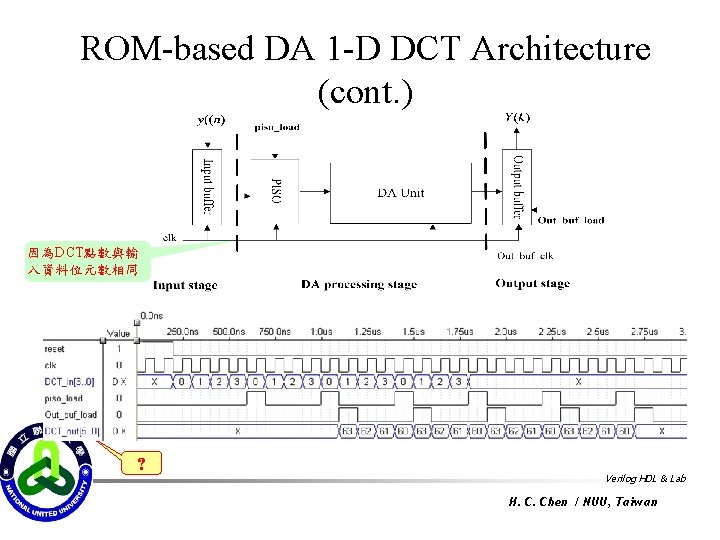

ROM-based DA 1 -D DCT Architecture (cont. ) 因為DCT點數與輸 入資料位元數相同 ? Verilog HDL & Lab H. C. Chen / NUU, Taiwan

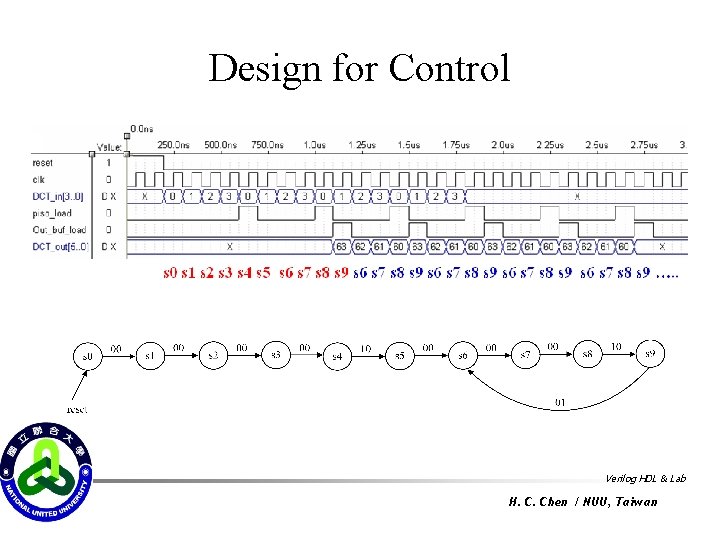

Design for Control Verilog HDL & Lab H. C. Chen / NUU, Taiwan

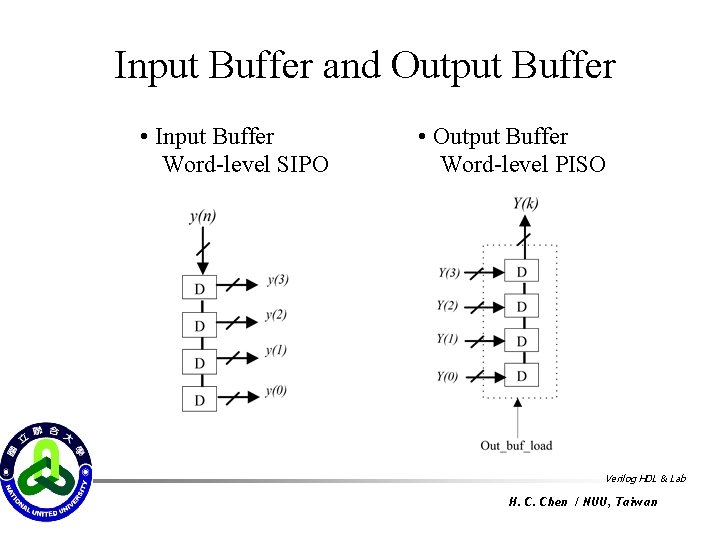

Input Buffer and Output Buffer • Input Buffer Word-level SIPO • Output Buffer Word-level PISO Verilog HDL & Lab H. C. Chen / NUU, Taiwan

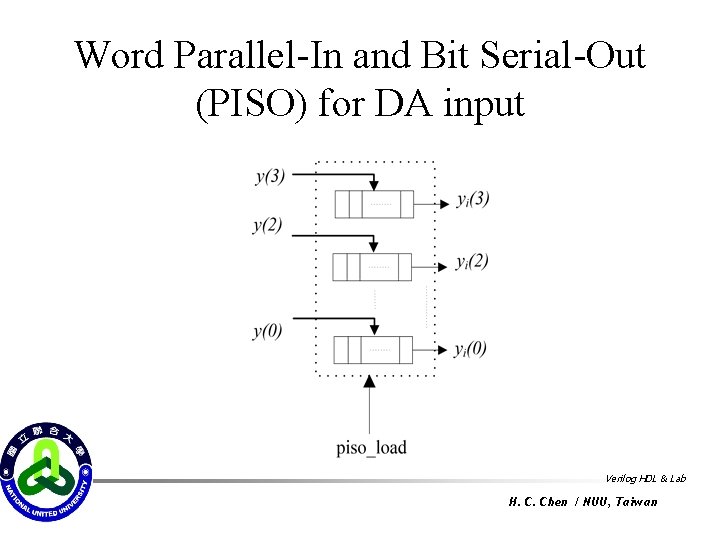

Word Parallel-In and Bit Serial-Out (PISO) for DA input Verilog HDL & Lab H. C. Chen / NUU, Taiwan

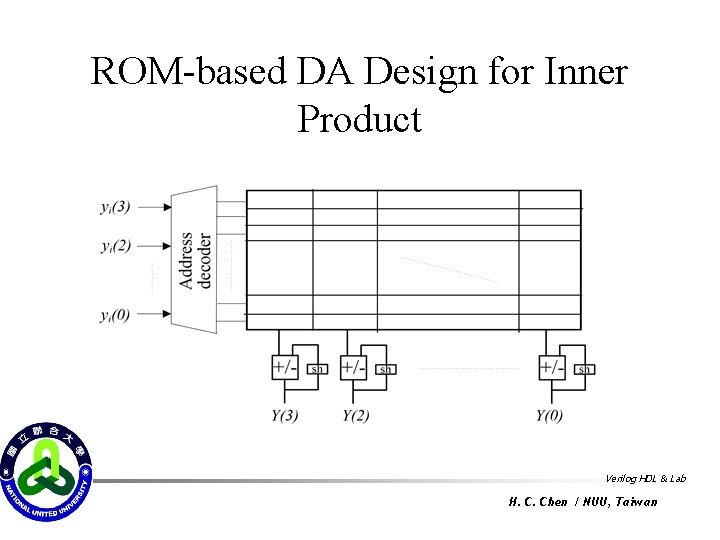

ROM-based DA Design for Inner Product Verilog HDL & Lab H. C. Chen / NUU, Taiwan

參考資料 l Stanley A. White, “Application of Distributed Arithmetic to Digital Signal Processing: A Tutorial Review, ” IEEE ASSP Magazine, pp. 4 -18, 1989. Verilog HDL & Lab H. C. Chen / NUU, Taiwan

- Slides: 25