1 CHAPITRE 2 Architecture des ordinateurs 2 Architecture

- Slides: 45

1 CHAPITRE 2 Architecture des ordinateurs

2 Architecture • Architecture externe (spécification) • Services fournis à l’utilisateur • Types de données et représentation • Modes d’adressage • Instructions machine • Mécanismes d’entrée/sortie • Architecture interne (organisation) • Description physique des composantes et les interconnexions • Organisation interne du processeur • Gestions des conflits de ressources, etc. • Il peut exister plusieurs implémentations d’une même architecture (plusieurs organisations pour une spécification)

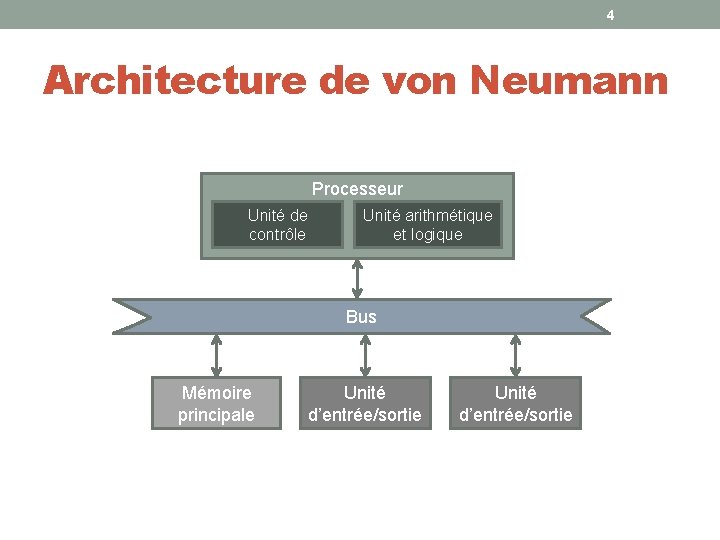

3 Architecture de von Neumann • Présentée dans les années 1940 • Un processeur central • Unité de contrôle • Unité arithmétique et logique • Mémoire principale • Unités d’entrée/sortie • Les composants sont reliés par un canal de communications (bus) constitué d’un ensemble de lignes (n) électriques parallèles.

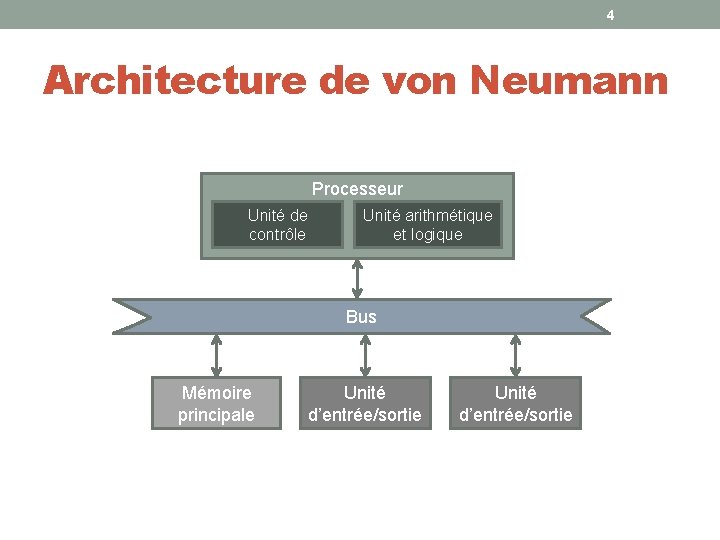

4 Architecture de von Neumann Processeur Unité de contrôle Unité arithmétique et logique Bus Mémoire principale Unité d’entrée/sortie

5 Architecture de von Neumann • Processeur • Gère l’allocation du BUS • Décode et exécute les instructions • Possède une petite mémoire locale (registres) • Accès très rapide • Contiennent temporairement les opérandes instructions (données)

6 Architecture de von Neumann • Mémoire centrale • Constituée de cellules qui contiennent le programme et ses données • Permet le transfert de données • Mémoire Registre (Chargement) • Registre Mémoire (Stockage) • Chaque cellule a une adresse • Accès beaucoup plus lent que les registres

7 Architecture de von Neumann • Unité d’entrée/sortie • Contrôle les périphériques (moniteur, souris, clavier, lecteur, etc. ) • Programmation généralement complexe • Échange de données entre le périphérique et le processeur • Définit par un ensemble de règles, appelé protocole de communication • Habituellement très lent (en comparaison des registres et de la mémoire)

8 Architecture de von Neumann • Le programme et ses données sont toujours emmagasinés en mémoire principale • Les instructions ne peuvent être exécutées en mémoire principale • Traitement global d’une instruction • Extraction de la mémoire • Décodage • Exécution • Stockage des résultats

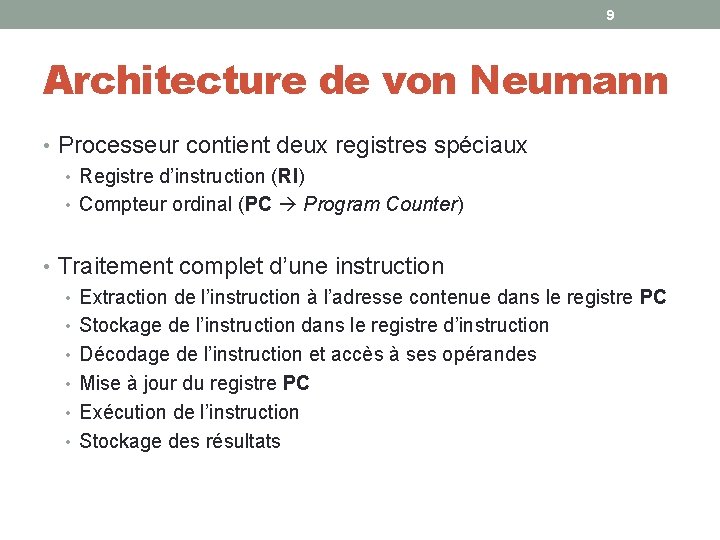

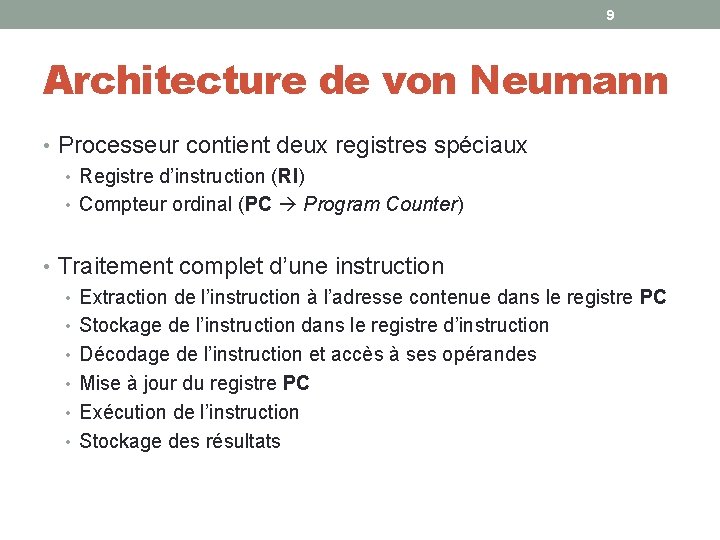

9 Architecture de von Neumann • Processeur contient deux registres spéciaux • Registre d’instruction (RI) • Compteur ordinal (PC Program Counter) • Traitement complet d’une instruction • Extraction de l’instruction à l’adresse contenue dans le registre PC • Stockage de l’instruction dans le registre d’instruction • Décodage de l’instruction et accès à ses opérandes • Mise à jour du registre PC • Exécution de l’instruction • Stockage des résultats

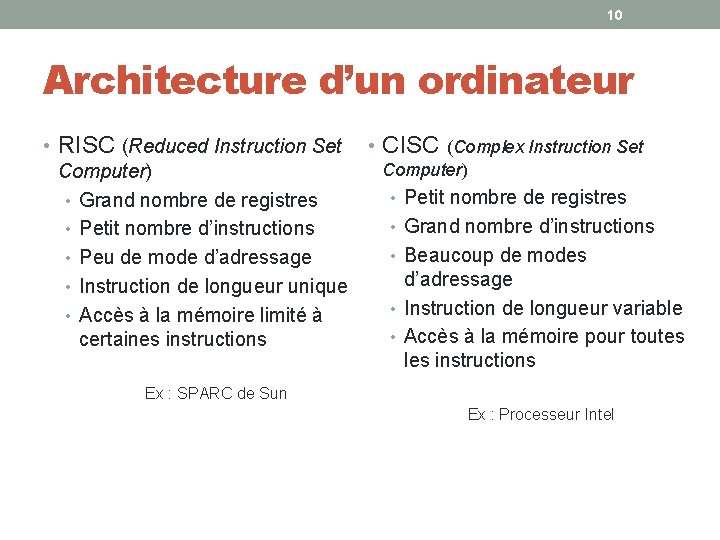

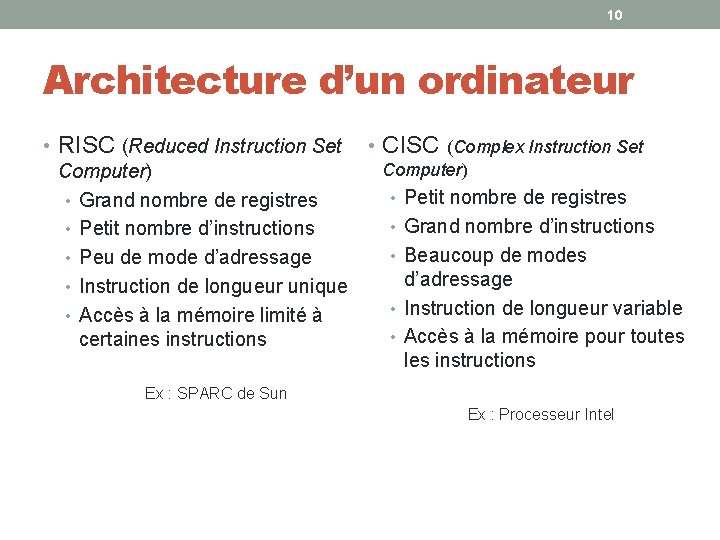

10 Architecture d’un ordinateur • RISC (Reduced Instruction Set • CISC (Complex Instruction Set Computer) • Petit nombre de registres • Grand nombre d’instructions • Petit nombre d’instructions • Beaucoup de modes • Peu de mode d’adressage • Instruction de longueur unique • Instruction de longueur variable • Accès à la mémoire limité à • Accès à la mémoire pour toutes certaines instructions les instructions Ex : SPARC de Sun Ex : Processeur Intel

11 Mémoire centrale • Vecteur de cellules adressables • Contient des bits (valeur de 0 ou 1) • La plus petite cellule contient habituellement 8 bits (1 octet) • La taille d’un mot est liée à la largeur du bus de données • Habituellement 32 bits (4 octets) sur les architectures courantes

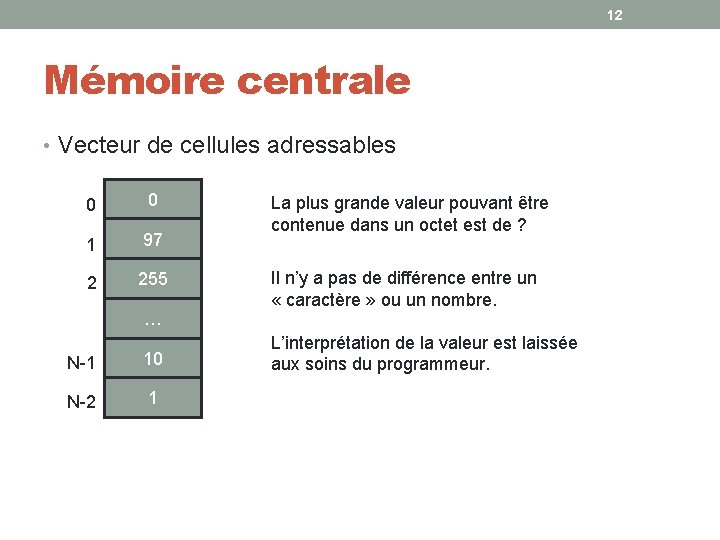

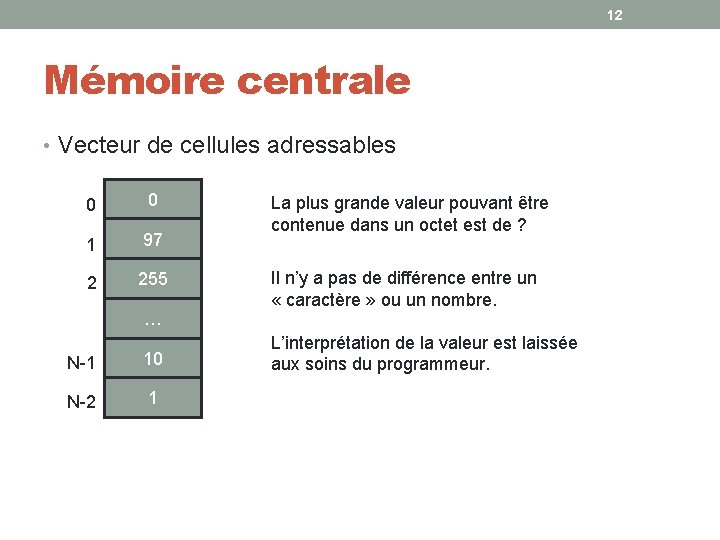

12 Mémoire centrale • Vecteur de cellules adressables 0 0 1 97 2 255 … N-1 10 N-2 1 La plus grande valeur pouvant être contenue dans un octet est de ? Il n’y a pas de différence entre un « caractère » ou un nombre. L’interprétation de la valeur est laissée aux soins du programmeur.

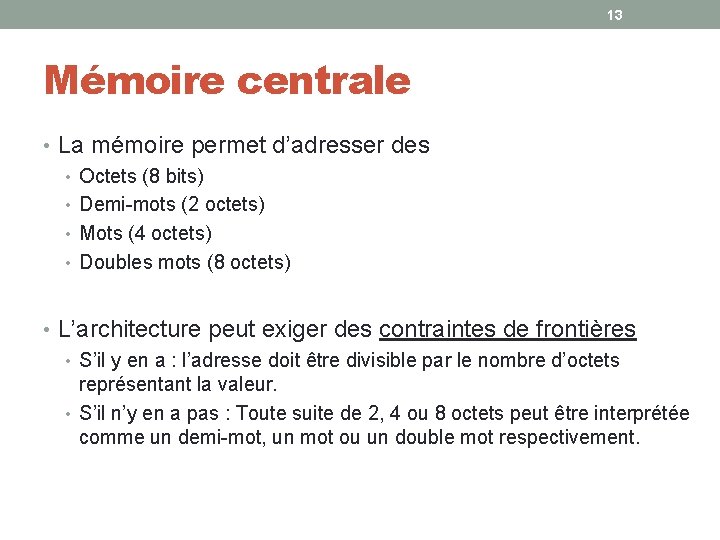

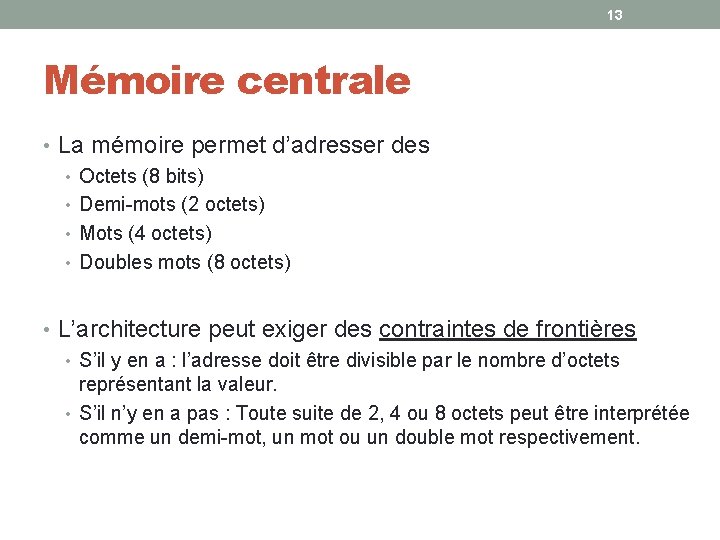

13 Mémoire centrale • La mémoire permet d’adresser des • Octets (8 bits) • Demi-mots (2 octets) • Mots (4 octets) • Doubles mots (8 octets) • L’architecture peut exiger des contraintes de frontières • S’il y en a : l’adresse doit être divisible par le nombre d’octets représentant la valeur. • S’il n’y en a pas : Toute suite de 2, 4 ou 8 octets peut être interprétée comme un demi-mot, un mot ou un double mot respectivement.

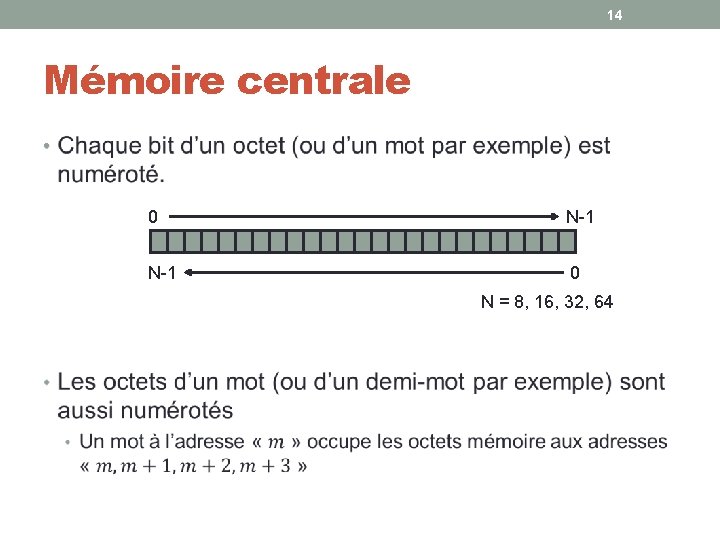

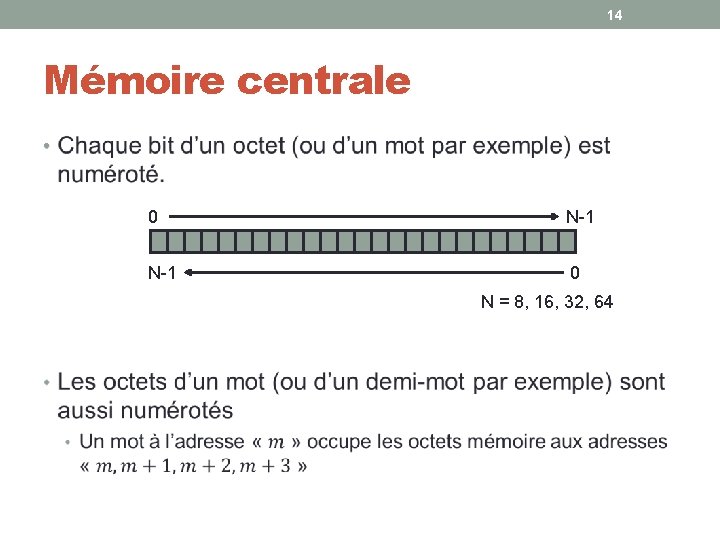

14 Mémoire centrale • 0 N-1 0 N = 8, 16, 32, 64

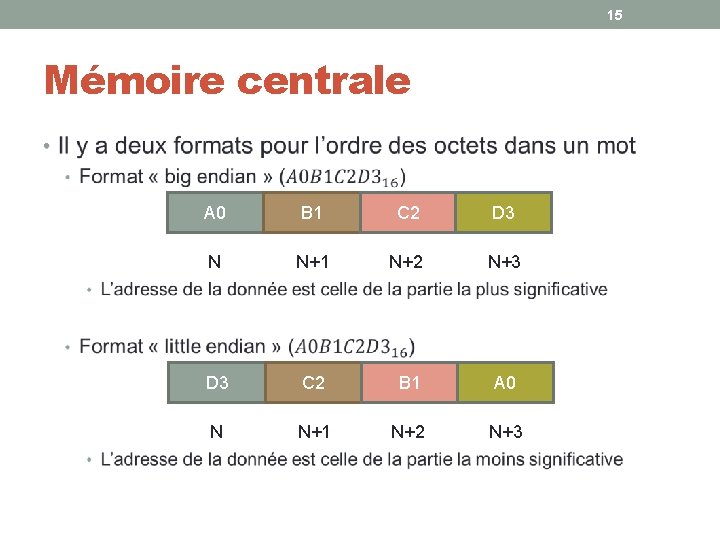

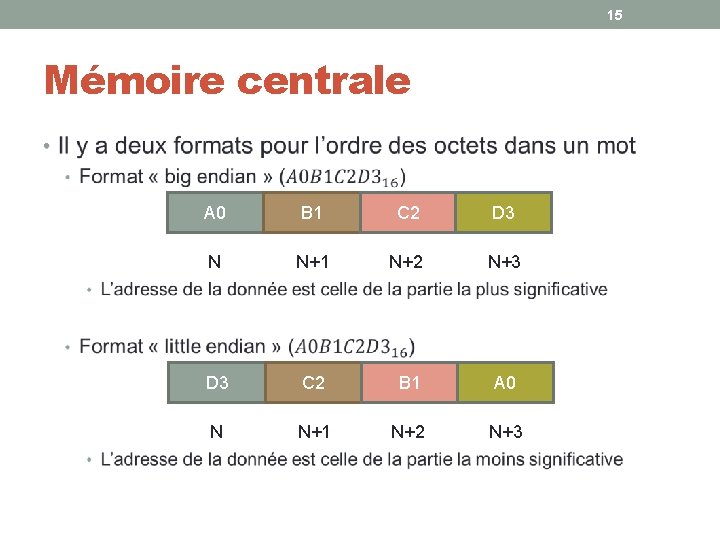

15 Mémoire centrale • A 0 B 1 C 2 D 3 N N+1 N+2 N+3 D 3 C 2 B 1 A 0 N N+1 N+2 N+3

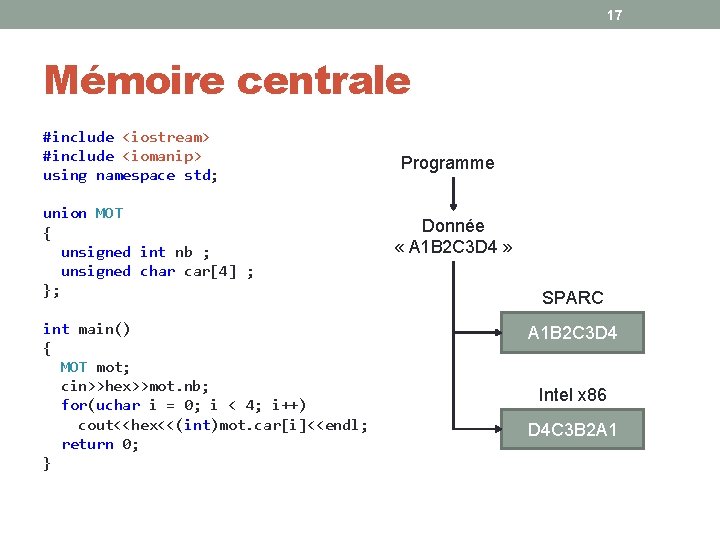

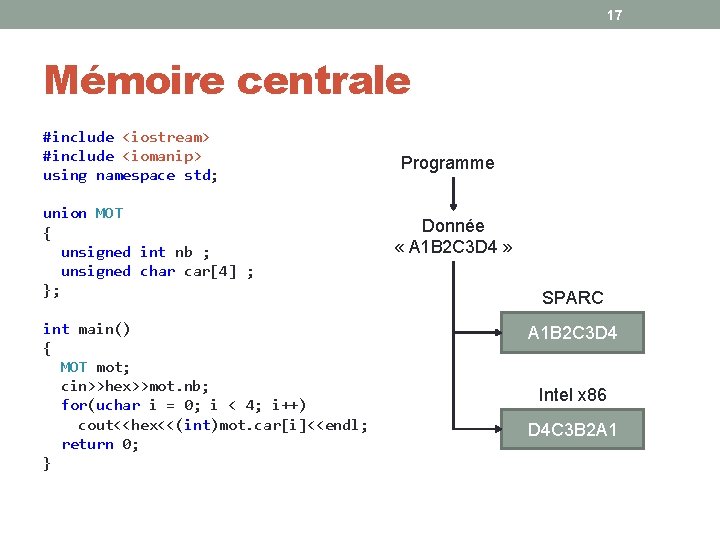

16 Mémoire centrale • La différence de format est souvent imperceptible • Il faut faire attention lorsque • Il y a transfert de données d’un ordinateur à l’autre • Une valeur est emmagasinée dans un mot, mais lue octet par octet

17 Mémoire centrale #include <iostream> #include <iomanip> using namespace std; union MOT { unsigned int nb ; unsigned char car[4] ; }; int main() { MOT mot; cin>>hex>>mot. nb; for(uchar i = 0; i < 4; i++) cout<<hex<<(int)mot. car[i]<<endl; return 0; } Programme Donnée « A 1 B 2 C 3 D 4 » SPARC A 1 B 2 C 3 D 4 Intel x 86 D 4 C 3 B 2 A 1

18 Processeur • Consiste à exécuter des instructions • La spécification du processeur comprend la description • Des registres • Des modes d’adressage • Des instructions • Les modes d’adressage sont présentés dans le chapitre suivant

19 Processeur • Possède un ensemble de cellules spécialisées (registres) • Registres généraux • Emmagasine temporairement les opérandes instructions • Très rapide (on ne dépend pas du bus de données) • Certains sont dédiés à un usage particulier ou à une valeur fixe • Un pointeur de pile (Stack pointer (SP) ), la valeur 0, etc. • Registres spécialisés • Compteur ordinal (Program Counter (PC) ) • Registre d’état (Processor Status (PS) ) • Registres d’adresse, etc. • Un registre d’instruction (RI), qui ne peut être assigné directement

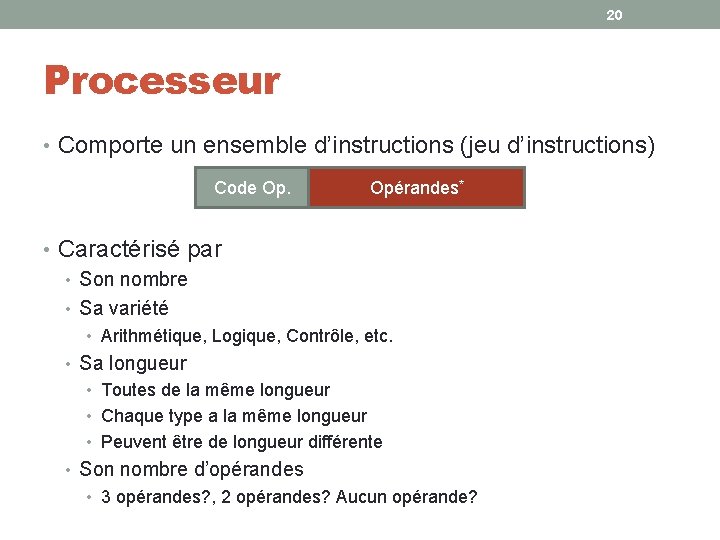

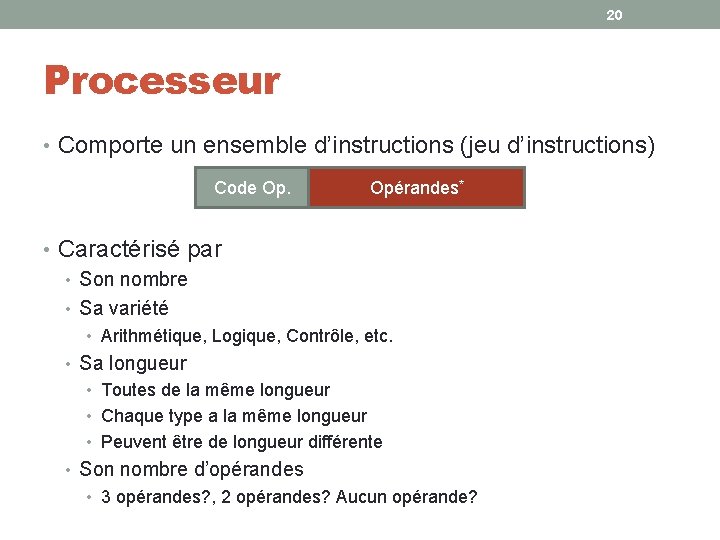

20 Processeur • Comporte un ensemble d’instructions (jeu d’instructions) Code Op. Opérandes* • Caractérisé par • Son nombre • Sa variété • Arithmétique, Logique, Contrôle, etc. • Sa longueur • Toutes de la même longueur • Chaque type a la même longueur • Peuvent être de longueur différente • Son nombre d’opérandes • 3 opérandes? , 2 opérandes? Aucun opérande?

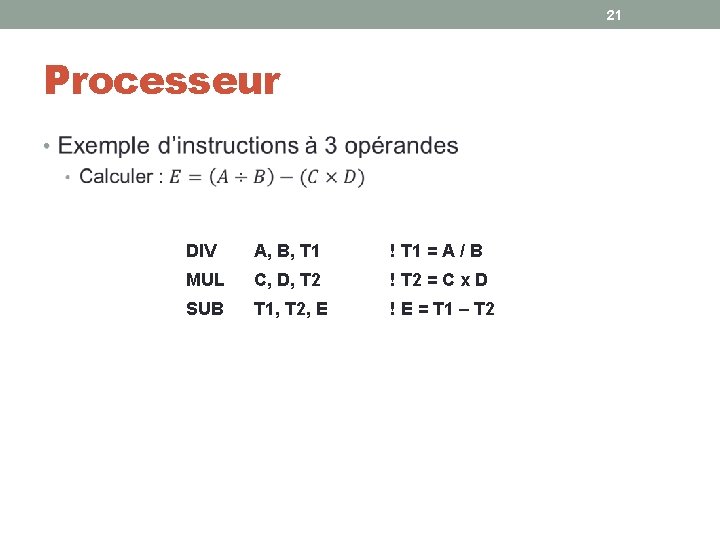

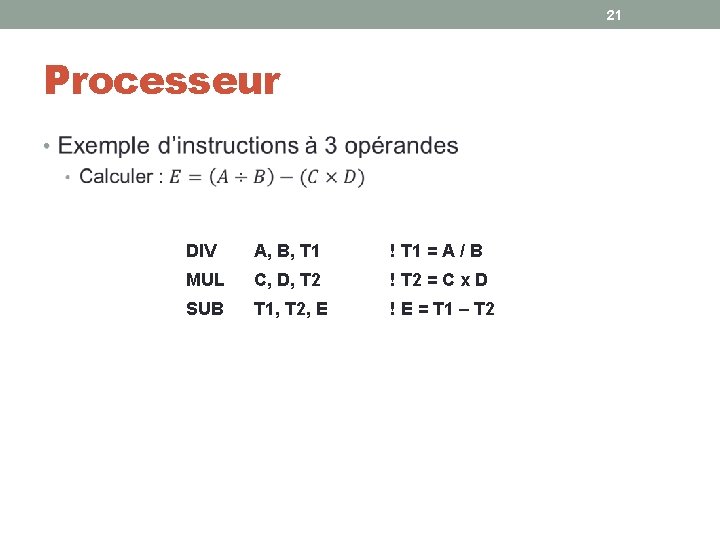

21 Processeur • DIV A, B, T 1 ! T 1 = A / B MUL C, D, T 2 ! T 2 = C x D SUB T 1, T 2, E ! E = T 1 – T 2

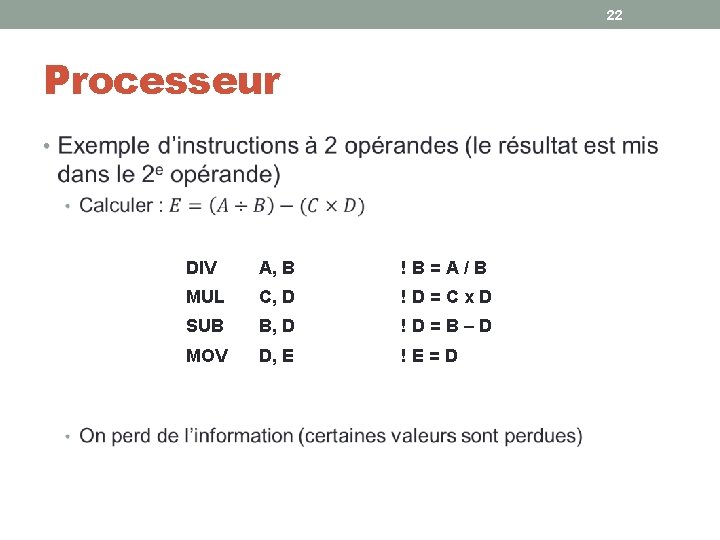

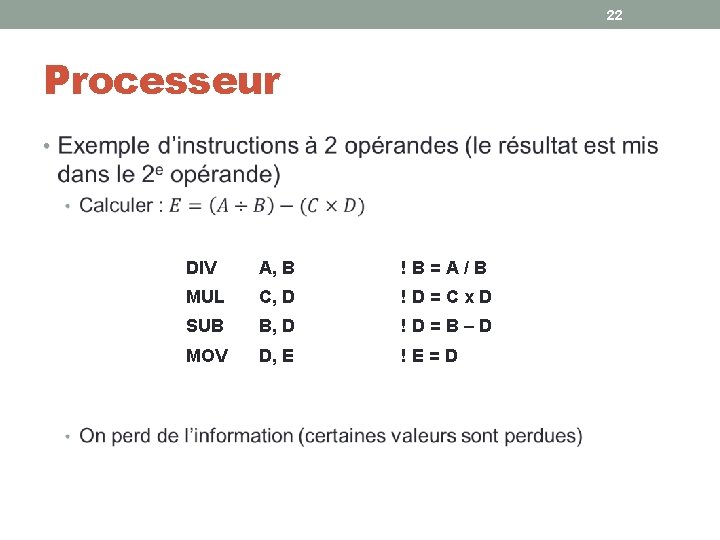

22 Processeur • DIV A, B !B=A/B MUL C, D !D=Cx. D SUB B, D !D=B–D MOV D, E !E=D

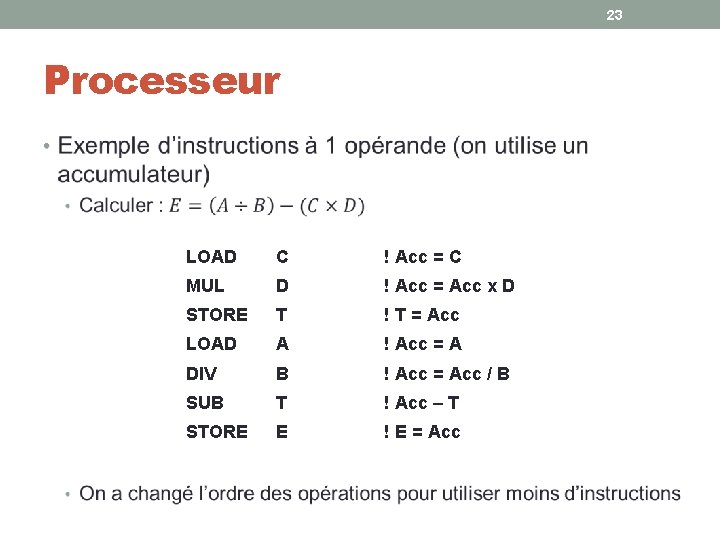

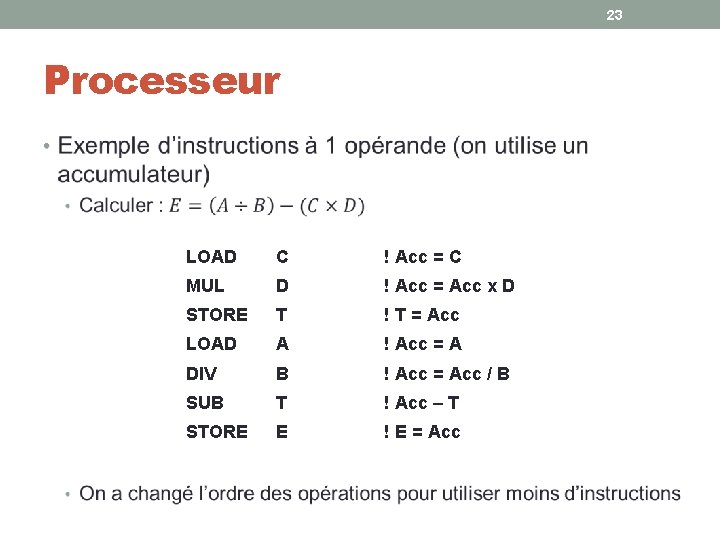

23 Processeur • LOAD C ! Acc = C MUL D ! Acc = Acc x D STORE T ! T = Acc LOAD A ! Acc = A DIV B ! Acc = Acc / B SUB T ! Acc – T STORE E ! E = Acc

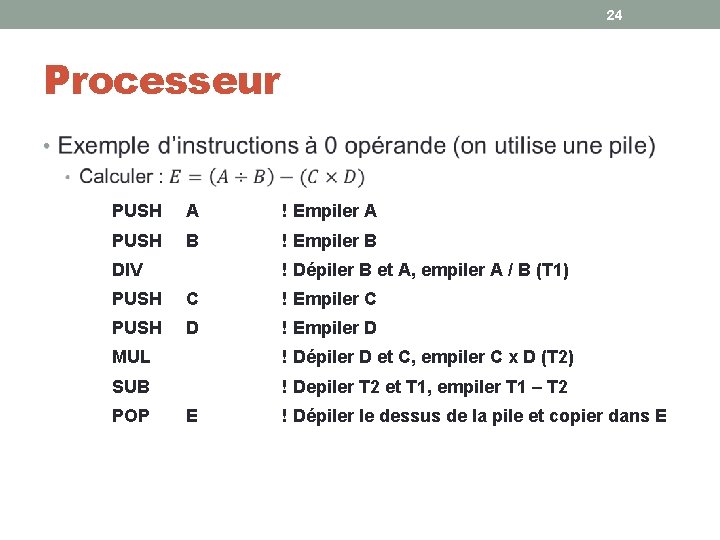

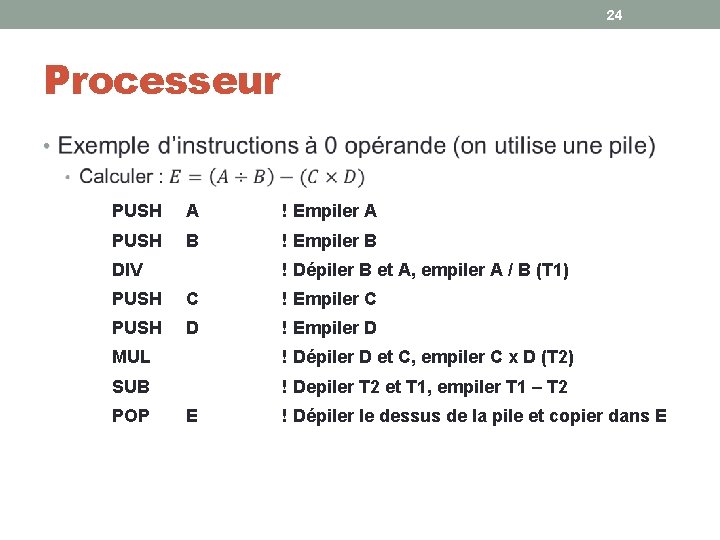

24 Processeur • PUSH A ! Empiler A PUSH B ! Empiler B DIV ! Dépiler B et A, empiler A / B (T 1) PUSH C ! Empiler C PUSH D ! Empiler D MUL ! Dépiler D et C, empiler C x D (T 2) SUB ! Depiler T 2 et T 1, empiler T 1 – T 2 POP E ! Dépiler le dessus de la pile et copier dans E

25 Organisation d’un ordinateur • Technique de pipeline • Permet d’obtenir de meilleure performance d’exécution des programmes • Un pipeline a autant d’étages que d’étape dans le traitement d’une instruction • Un cycle machine est défini comme étant le temps nécessaire au processeur pour passer une instruction d’un étage à l’autre

26 Organisation d’un ordinateur • Technique de pipeline • Supposons le cycle de traitement d’une instruction suivant : • EI Extraction de l’instruction et dépôt dans RI • DI Décodage de l’instruction et accès aux opérandes dans des registres • EX Exécution de l’instruction • MEM • Mise à jour du PC lors d’un branchement • Accès mémoire pour un chargement ou un stockage • ER Écriture du résultat dans un registre • Le cycle comporte 5 étapes indépendantes

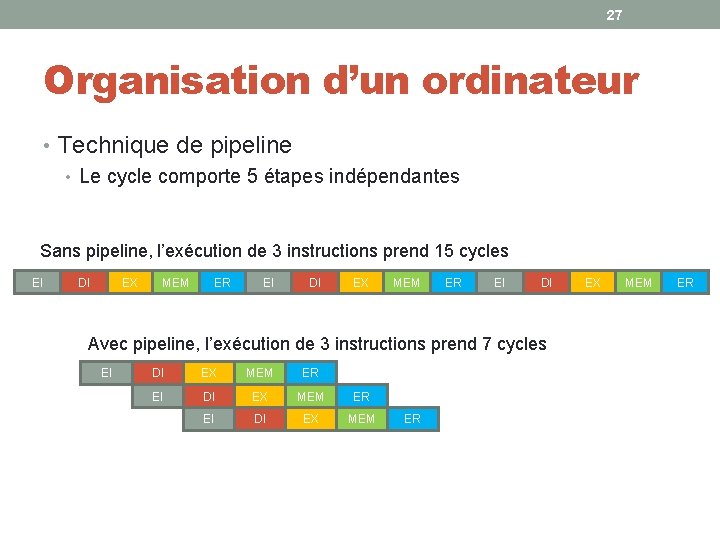

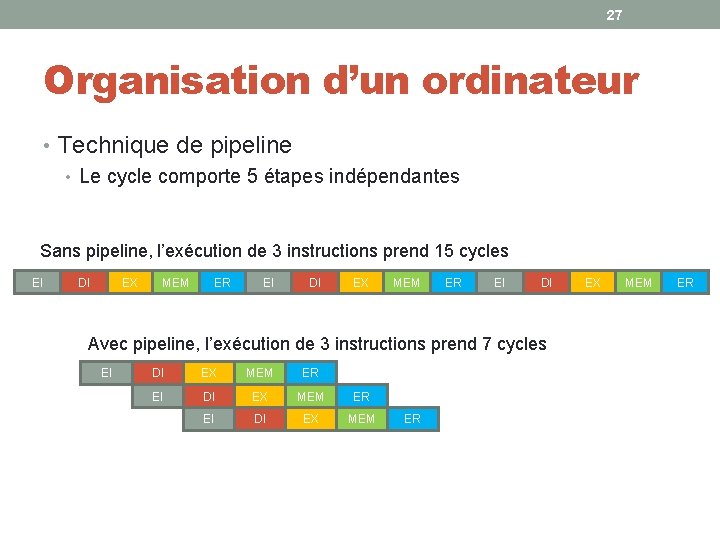

27 Organisation d’un ordinateur • Technique de pipeline • Le cycle comporte 5 étapes indépendantes Sans pipeline, l’exécution de 3 instructions prend 15 cycles EI DI EX MEM ER EI DI Avec pipeline, l’exécution de 3 instructions prend 7 cycles EI DI EX MEM ER

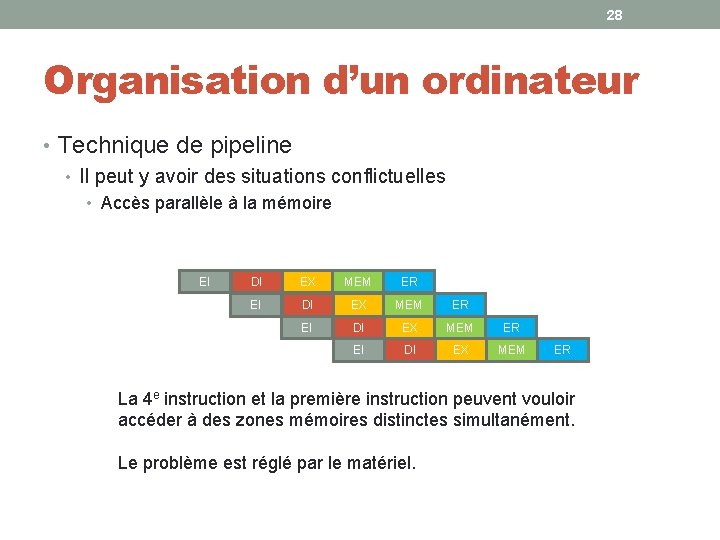

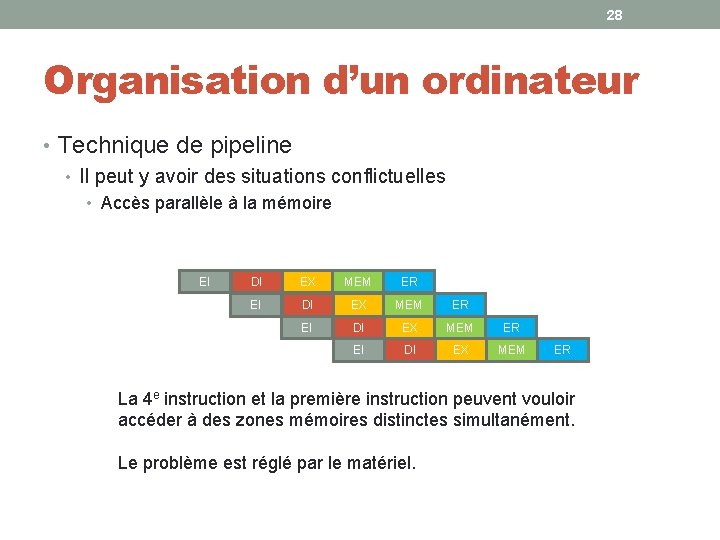

28 Organisation d’un ordinateur • Technique de pipeline • Il peut y avoir des situations conflictuelles • Accès parallèle à la mémoire EI DI EX MEM ER La 4 e instruction et la première instruction peuvent vouloir accéder à des zones mémoires distinctes simultanément. Le problème est réglé par le matériel.

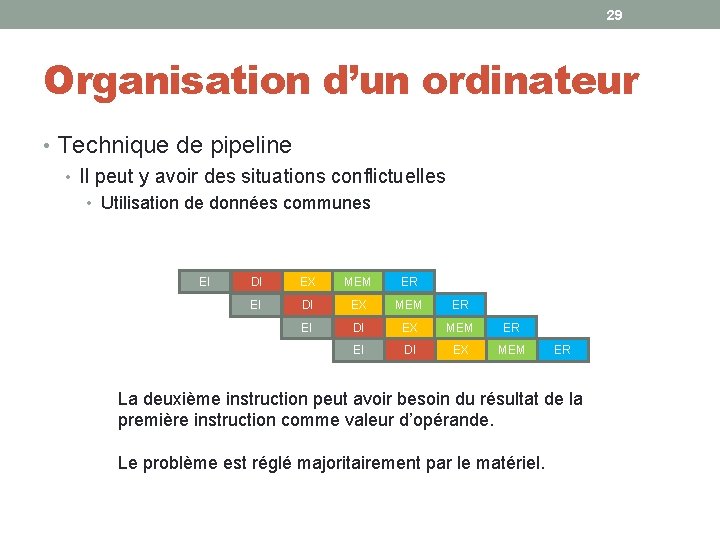

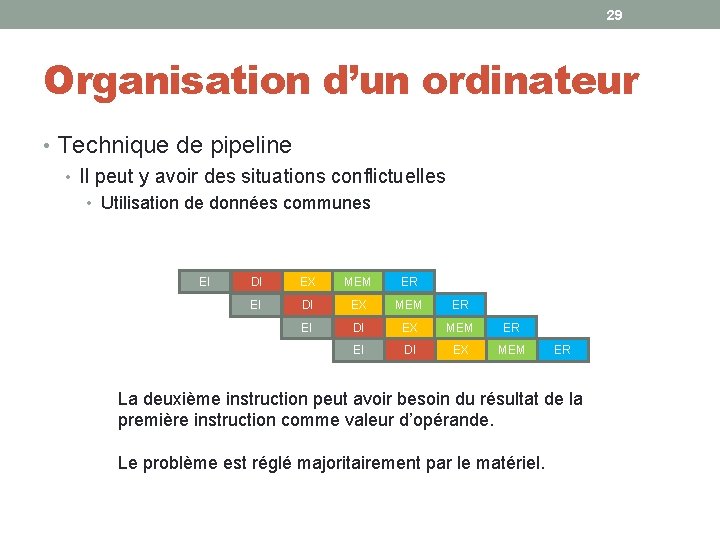

29 Organisation d’un ordinateur • Technique de pipeline • Il peut y avoir des situations conflictuelles • Utilisation de données communes EI DI EX MEM ER La deuxième instruction peut avoir besoin du résultat de la première instruction comme valeur d’opérande. Le problème est réglé majoritairement par le matériel.

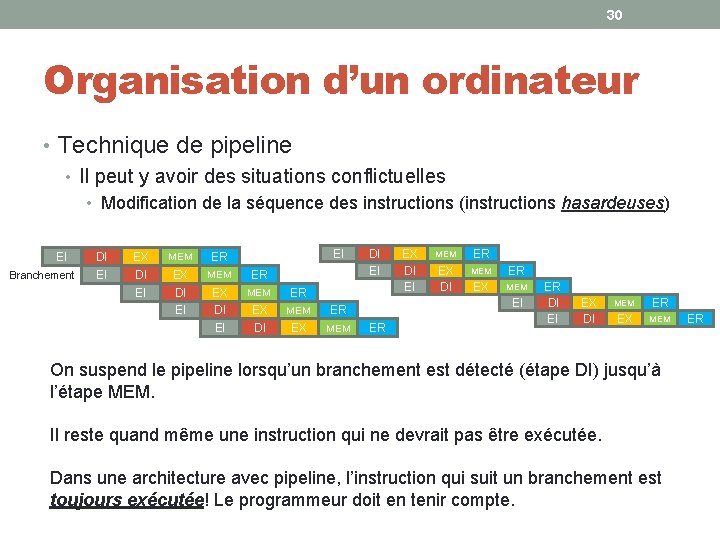

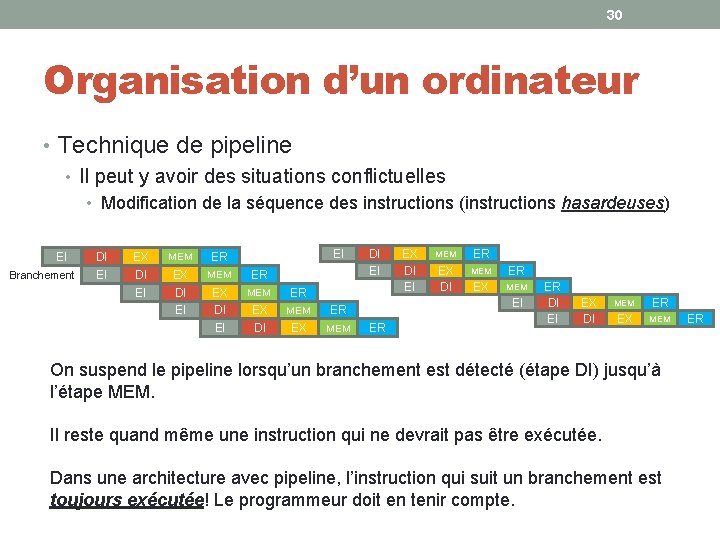

30 Organisation d’un ordinateur • Technique de pipeline • Il peut y avoir des situations conflictuelles • Modification de la séquence des instructions (instructions hasardeuses) EI Branchement EI DI EX MEM ER EI DI EI EX DI EI MEM ER EX DI MEM ER EX MEM EI ER ER DI EI EX DI MEM ER EX MEM On suspend le pipeline lorsqu’un branchement est détecté (étape DI) jusqu’à l’étape MEM. Il reste quand même une instruction qui ne devrait pas être exécutée. Dans une architecture avec pipeline, l’instruction qui suit un branchement est toujours exécutée! Le programmeur doit en tenir compte. ER

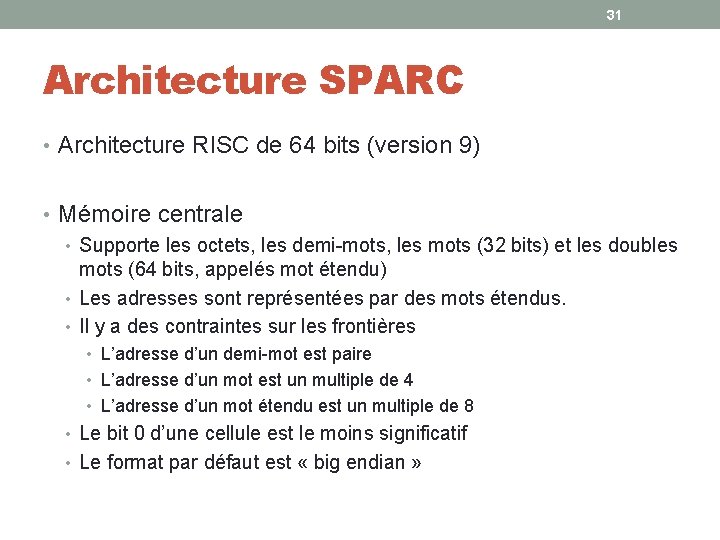

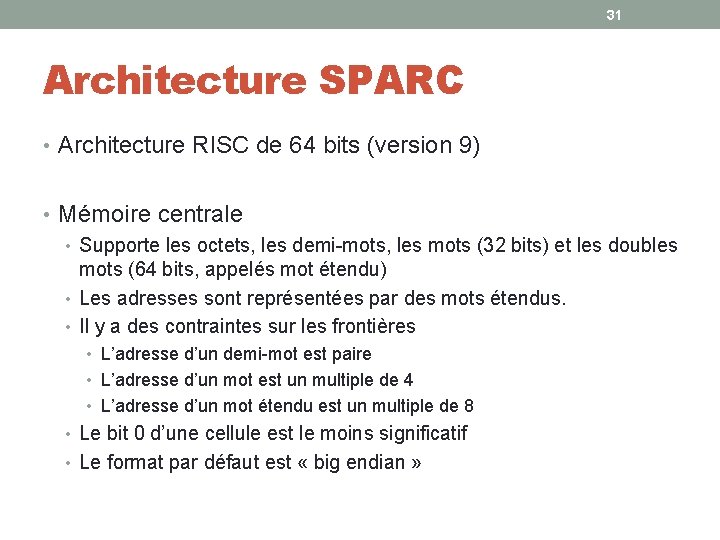

31 Architecture SPARC • Architecture RISC de 64 bits (version 9) • Mémoire centrale • Supporte les octets, les demi-mots, les mots (32 bits) et les doubles mots (64 bits, appelés mot étendu) • Les adresses sont représentées par des mots étendus. • Il y a des contraintes sur les frontières • L’adresse d’un demi-mot est paire • L’adresse d’un mot est un multiple de 4 • L’adresse d’un mot étendu est un multiple de 8 • Le bit 0 d’une cellule est le moins significatif • Le format par défaut est « big endian »

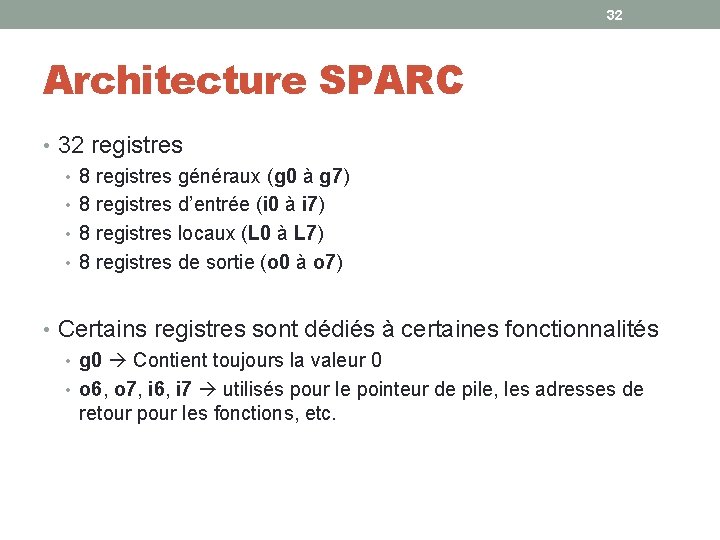

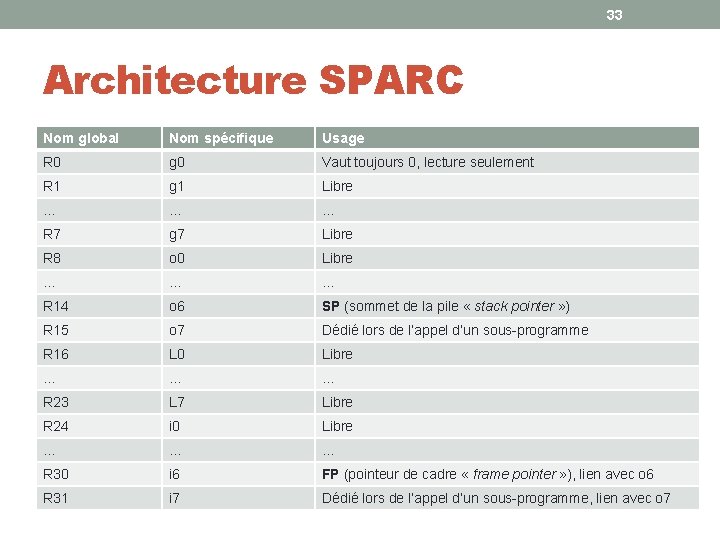

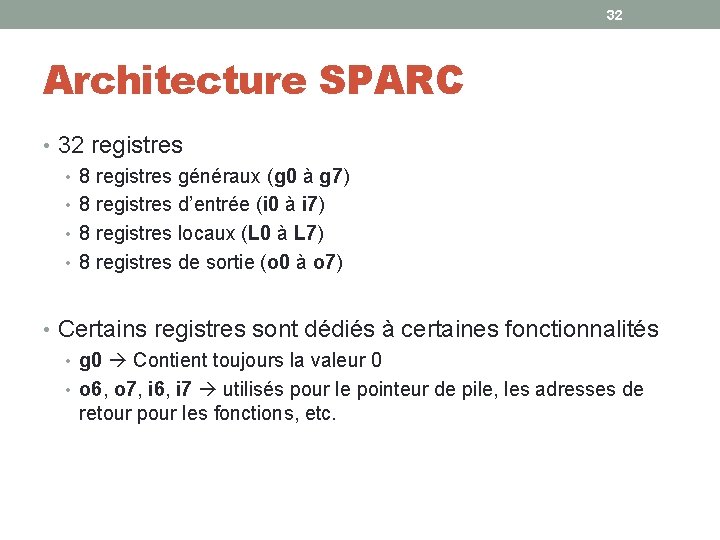

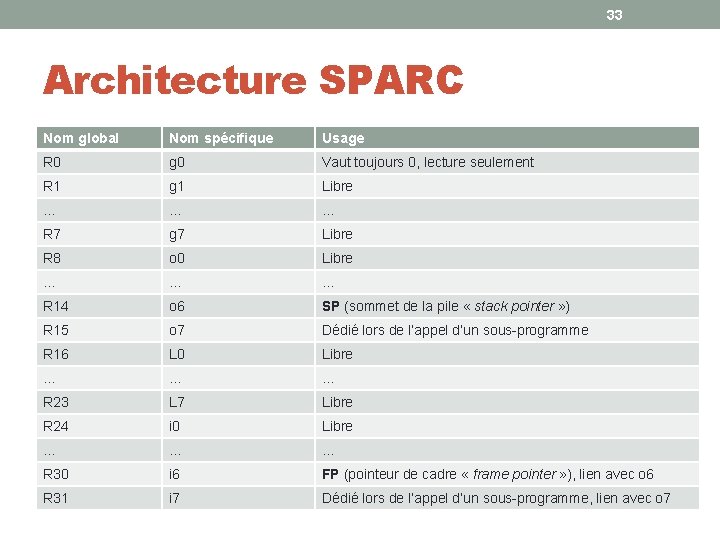

32 Architecture SPARC • 32 registres • 8 registres généraux (g 0 à g 7) • 8 registres d’entrée (i 0 à i 7) • 8 registres locaux (L 0 à L 7) • 8 registres de sortie (o 0 à o 7) • Certains registres sont dédiés à certaines fonctionnalités • g 0 Contient toujours la valeur 0 • o 6, o 7, i 6, i 7 utilisés pour le pointeur de pile, les adresses de retour pour les fonctions, etc.

33 Architecture SPARC Nom global Nom spécifique Usage R 0 g 0 Vaut toujours 0, lecture seulement R 1 g 1 Libre … … … R 7 g 7 Libre R 8 o 0 Libre … … … R 14 o 6 SP (sommet de la pile « stack pointer » ) R 15 o 7 Dédié lors de l’appel d’un sous-programme R 16 L 0 Libre … … … R 23 L 7 Libre R 24 i 0 Libre . . . … … R 30 i 6 FP (pointeur de cadre « frame pointer » ), lien avec o 6 R 31 i 7 Dédié lors de l’appel d’un sous-programme, lien avec o 7

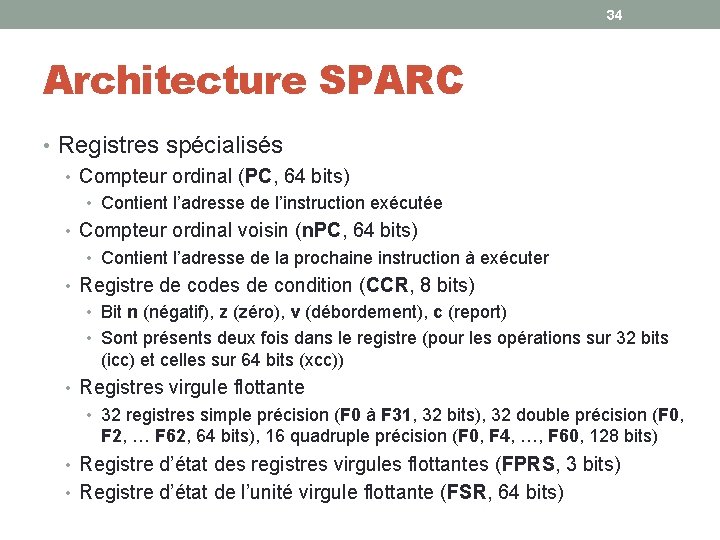

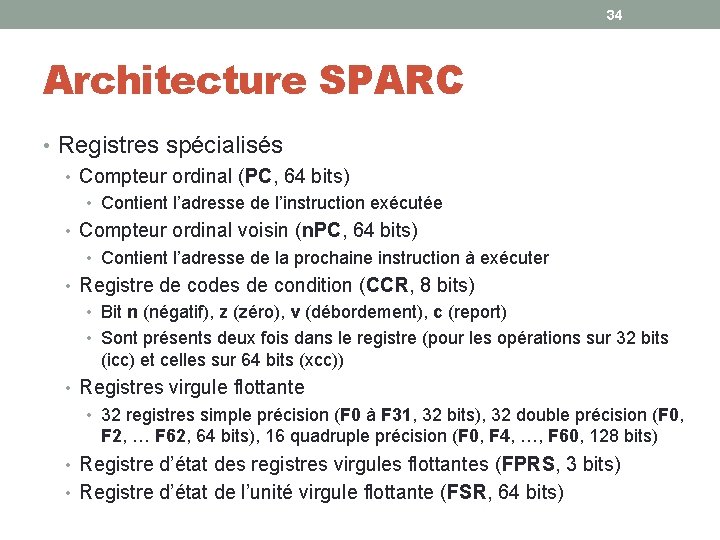

34 Architecture SPARC • Registres spécialisés • Compteur ordinal (PC, 64 bits) • Contient l’adresse de l’instruction exécutée • Compteur ordinal voisin (n. PC, 64 bits) • Contient l’adresse de la prochaine instruction à exécuter • Registre de codes de condition (CCR, 8 bits) • Bit n (négatif), z (zéro), v (débordement), c (report) • Sont présents deux fois dans le registre (pour les opérations sur 32 bits (icc) et celles sur 64 bits (xcc)) • Registres virgule flottante • 32 registres simple précision (F 0 à F 31, 32 bits), 32 double précision (F 0, F 2, … F 62, 64 bits), 16 quadruple précision (F 0, F 4, …, F 60, 128 bits) • Registre d’état des registres virgules flottantes (FPRS, 3 bits) • Registre d’état de l’unité virgule flottante (FSR, 64 bits)

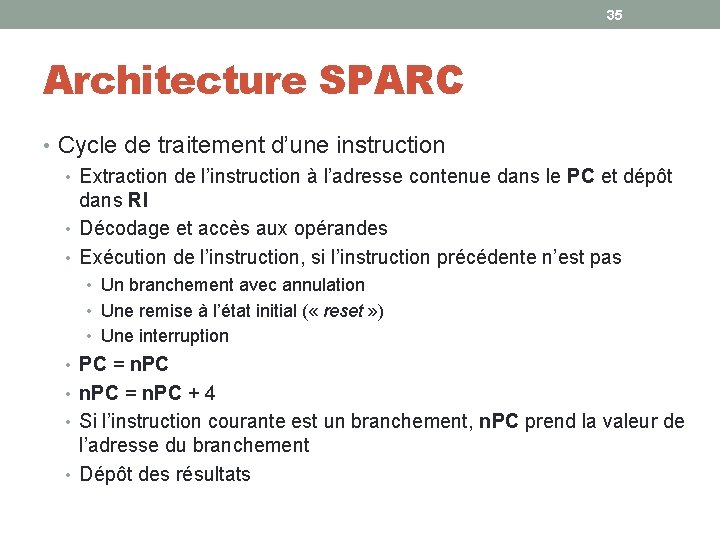

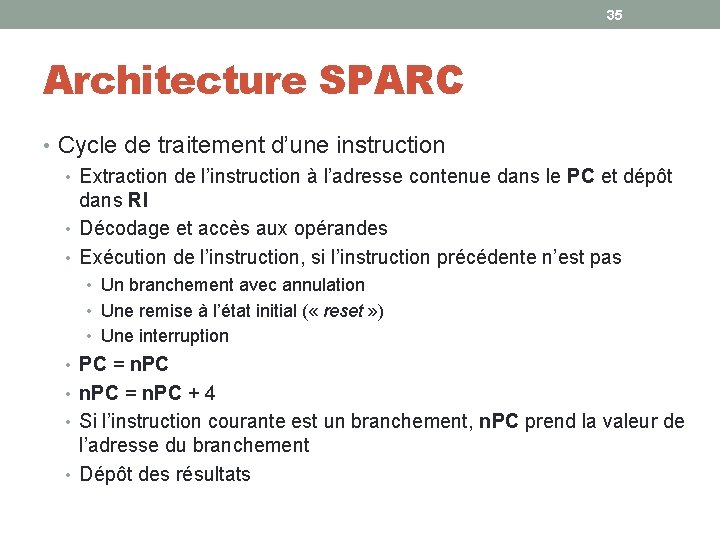

35 Architecture SPARC • Cycle de traitement d’une instruction • Extraction de l’instruction à l’adresse contenue dans le PC et dépôt dans RI • Décodage et accès aux opérandes • Exécution de l’instruction, si l’instruction précédente n’est pas • Un branchement avec annulation • Une remise à l’état initial ( « reset » ) • Une interruption • PC = n. PC • n. PC = n. PC + 4 • Si l’instruction courante est un branchement, n. PC prend la valeur de l’adresse du branchement • Dépôt des résultats

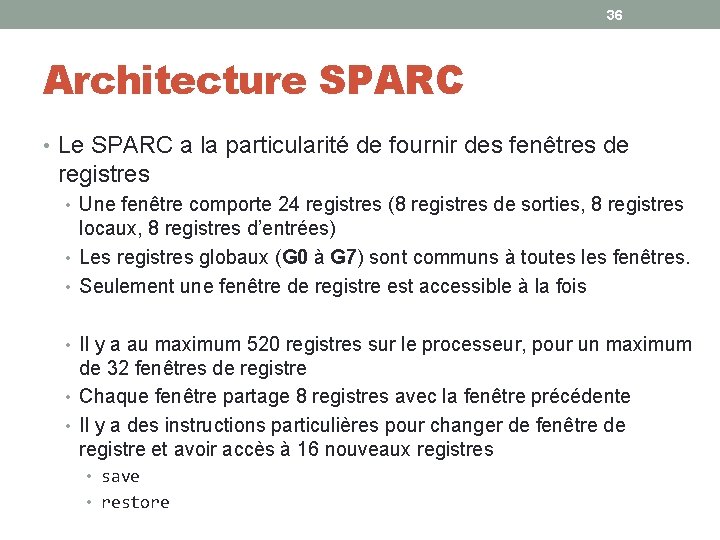

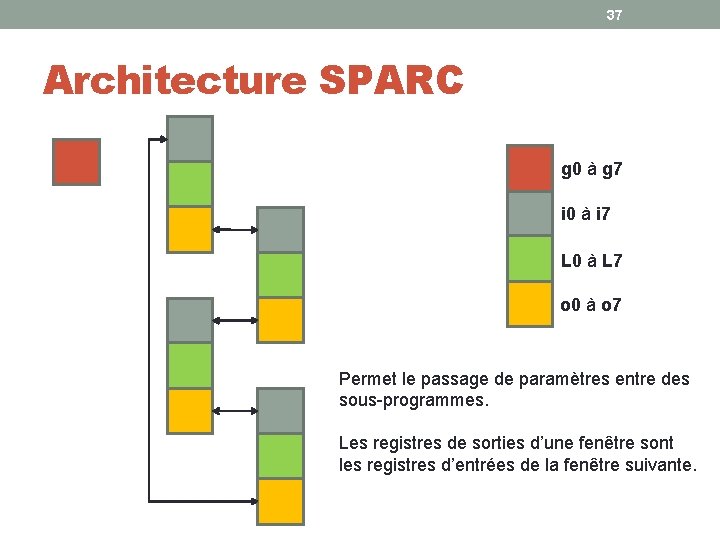

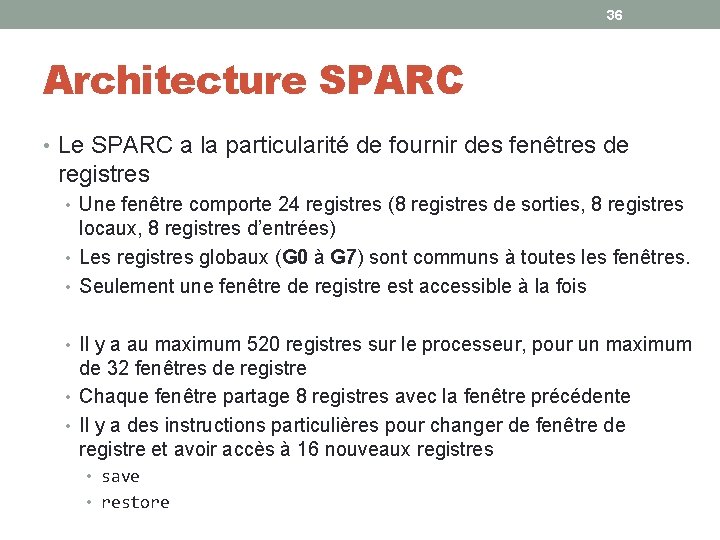

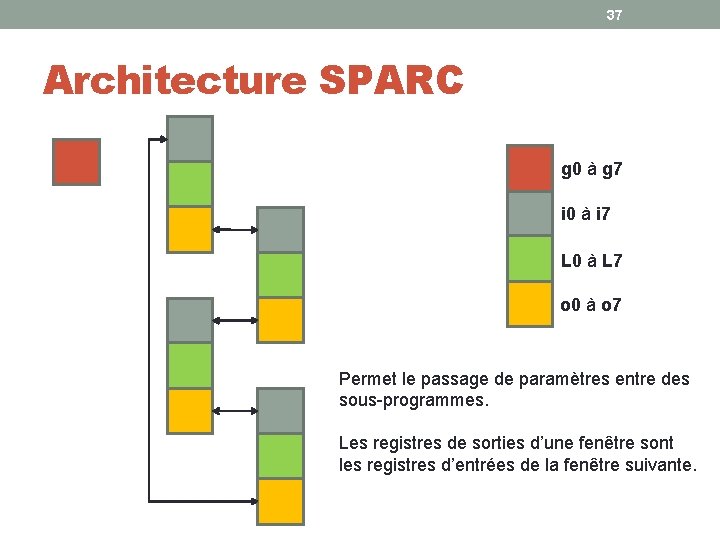

36 Architecture SPARC • Le SPARC a la particularité de fournir des fenêtres de registres • Une fenêtre comporte 24 registres (8 registres de sorties, 8 registres locaux, 8 registres d’entrées) • Les registres globaux (G 0 à G 7) sont communs à toutes les fenêtres. • Seulement une fenêtre de registre est accessible à la fois • Il y a au maximum 520 registres sur le processeur, pour un maximum de 32 fenêtres de registre • Chaque fenêtre partage 8 registres avec la fenêtre précédente • Il y a des instructions particulières pour changer de fenêtre de registre et avoir accès à 16 nouveaux registres • save • restore

37 Architecture SPARC g 0 à g 7 i 0 à i 7 L 0 à L 7 o 0 à o 7 Permet le passage de paramètres entre des sous-programmes. Les registres de sorties d’une fenêtre sont les registres d’entrées de la fenêtre suivante.

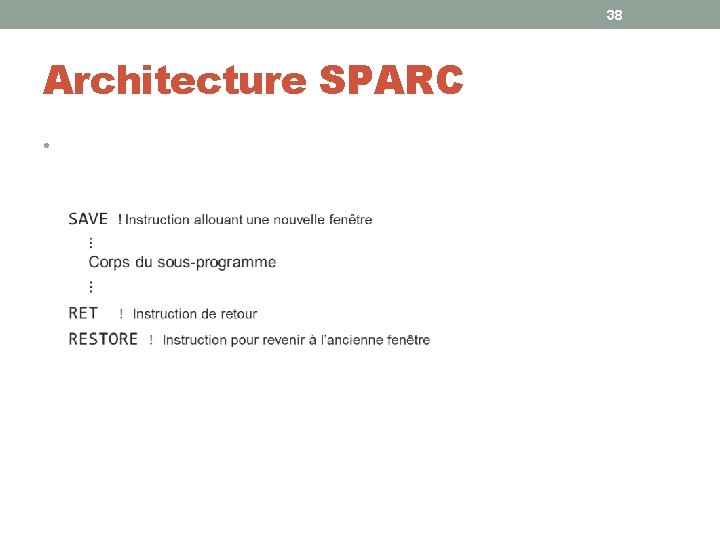

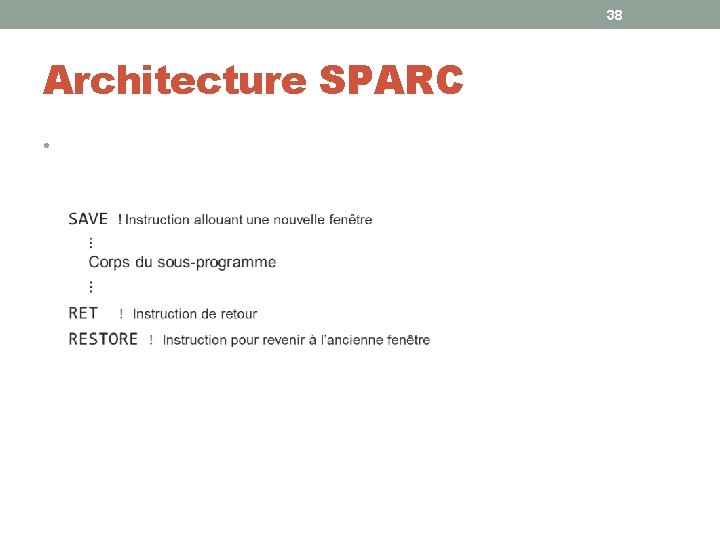

38 Architecture SPARC •

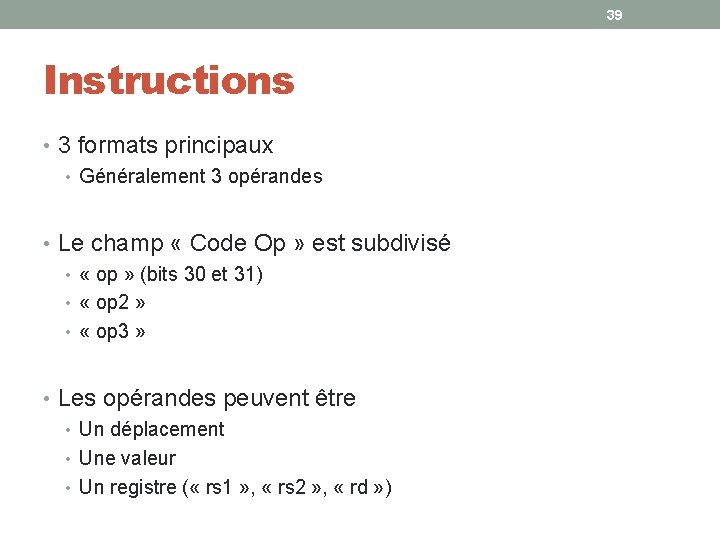

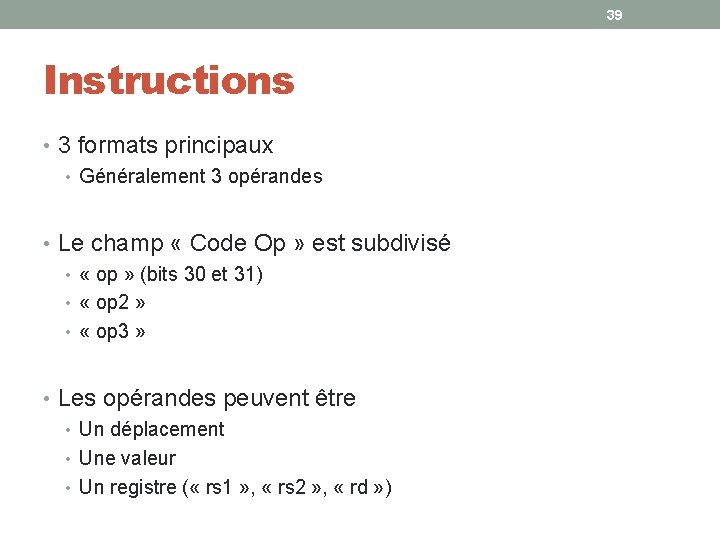

39 Instructions • 3 formats principaux • Généralement 3 opérandes • Le champ « Code Op » est subdivisé • « op » (bits 30 et 31) • « op 2 » • « op 3 » • Les opérandes peuvent être • Un déplacement • Une valeur • Un registre ( « rs 1 » , « rs 2 » , « rd » )

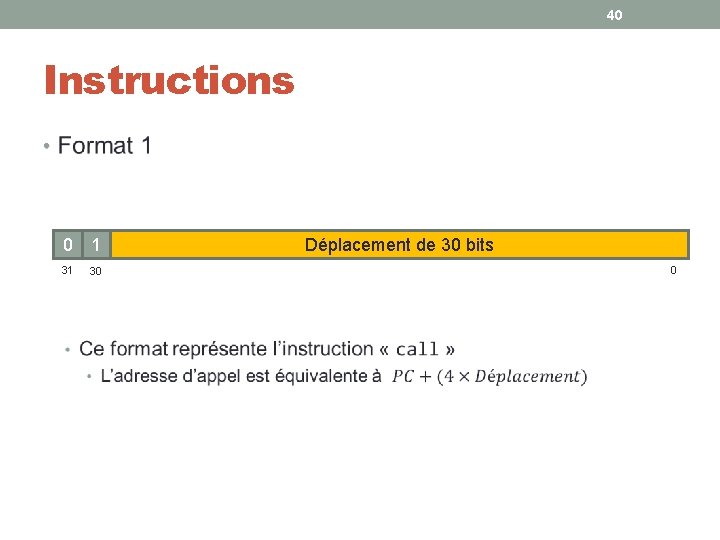

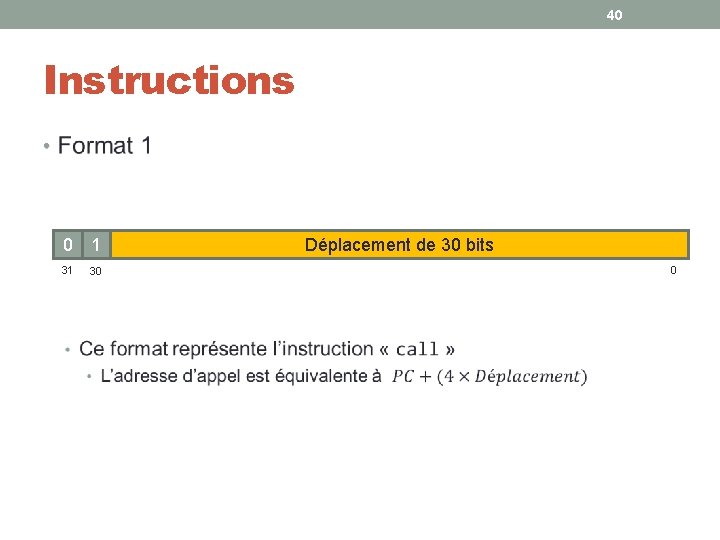

40 Instructions • 0 1 31 30 Déplacement de 30 bits 0

41 Instructions • Format 2 0 0 31 30 rd 29 Immédiat de 22 bits op 2 25 24 22 0 21 • Il s’agit de l’instruction « sethi » 0 0 a 31 30 29 cond 28 Immédiat de 22 bits op 2 25 24 22 21 • Il s’agit d’une instruction de branchement 0

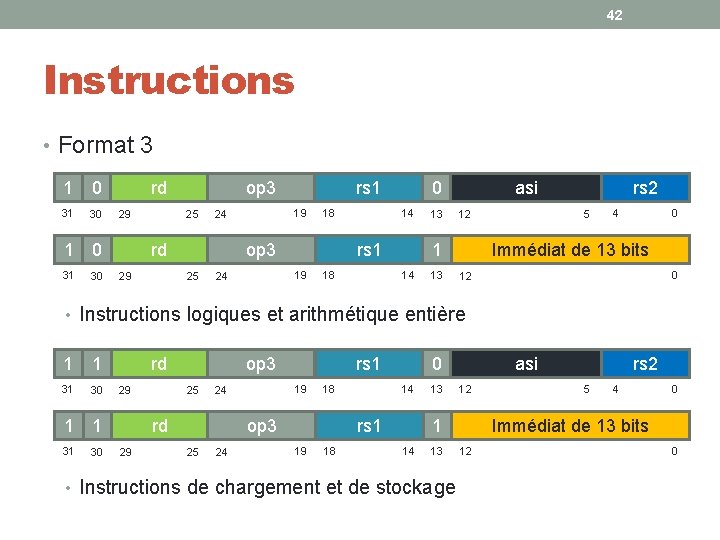

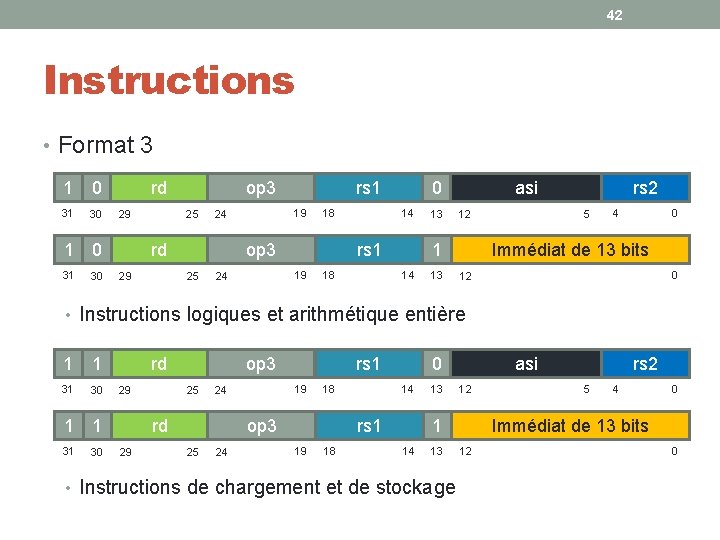

42 Instructions • Format 3 1 0 31 30 op 3 rd 29 25 19 24 18 op 3 rd 29 rs 1 25 14 rs 1 19 24 18 asi 0 13 14 13 5 12 1 rs 2 4 0 Immédiat de 13 bits 0 12 • Instructions logiques et arithmétique entière 1 1 31 30 op 3 rd 29 25 19 24 18 op 3 rd 29 rs 1 25 24 14 rs 1 19 18 asi 0 13 12 1 14 13 • Instructions de chargement et de stockage rs 2 5 4 0 Immédiat de 13 bits 12 0

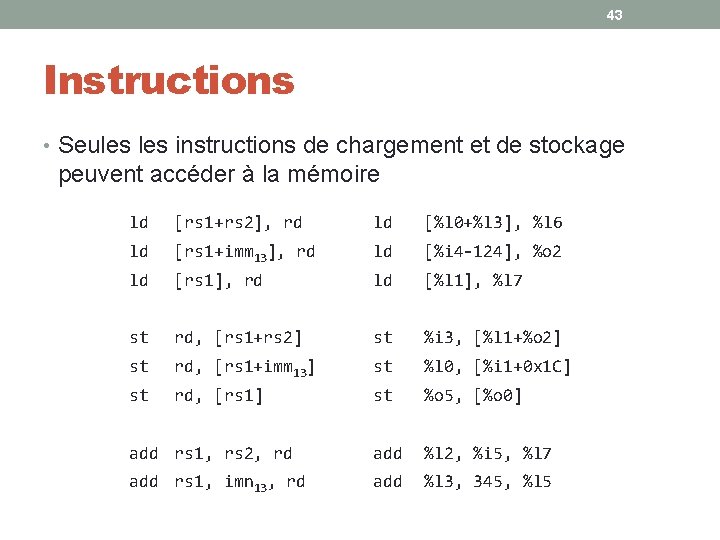

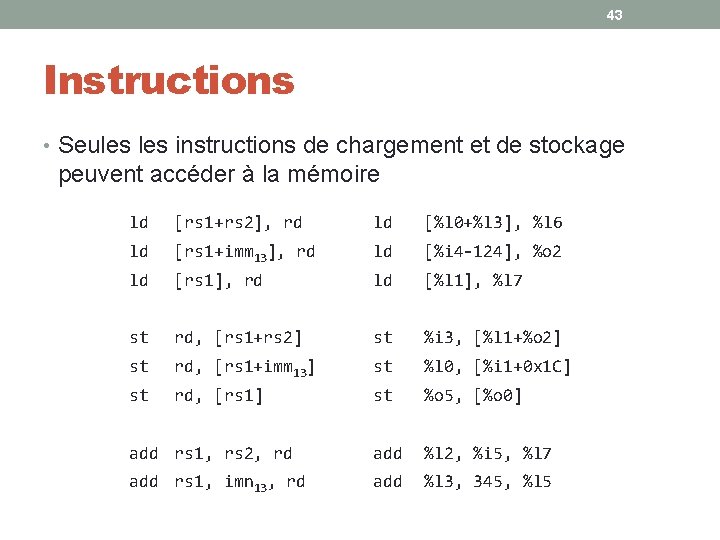

43 Instructions • Seules instructions de chargement et de stockage peuvent accéder à la mémoire ld [rs 1+rs 2], rd ld [%l 0+%l 3], %l 6 ld [rs 1+imm 13], rd ld [%i 4 -124], %o 2 ld [rs 1], rd ld [%l 1], %l 7 st rd, [rs 1+rs 2] st %i 3, [%l 1+%o 2] st rd, [rs 1+imm 13] st %l 0, [%i 1+0 x 1 C] st rd, [rs 1] st %o 5, [%o 0] add rs 1, rs 2, rd add %l 2, %i 5, %l 7 add rs 1, imn 13, rd add %l 3, 345, %l 5

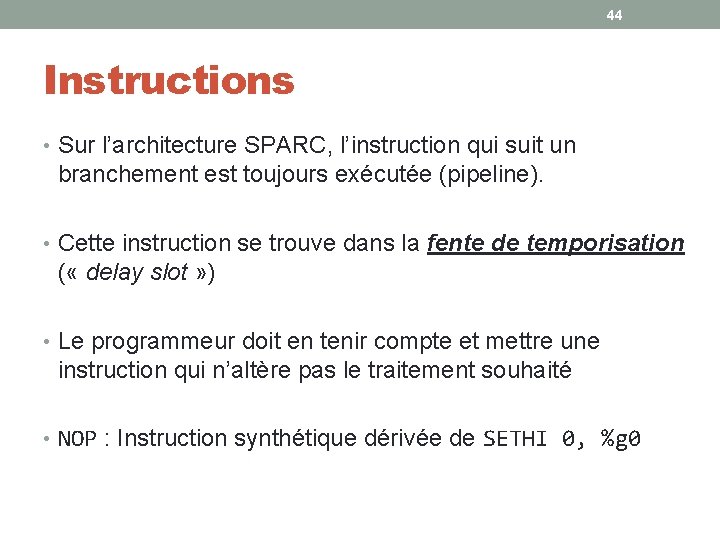

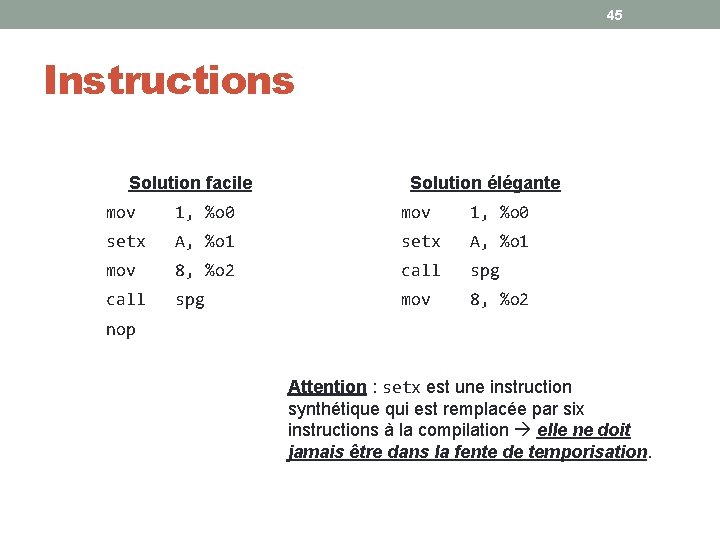

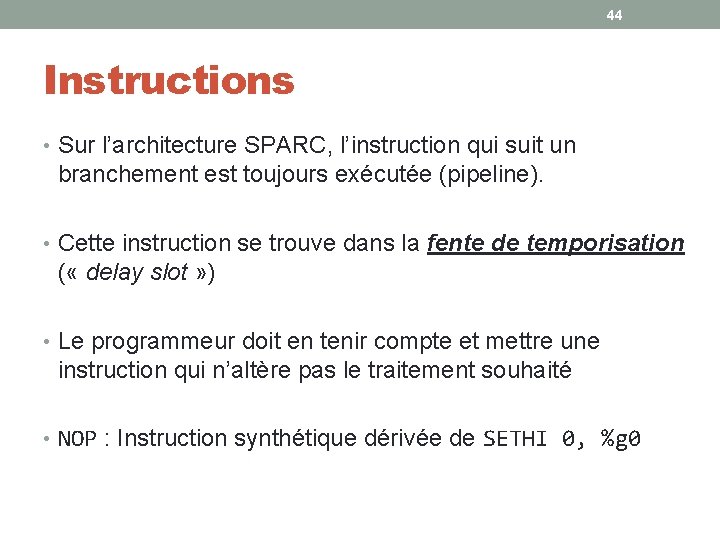

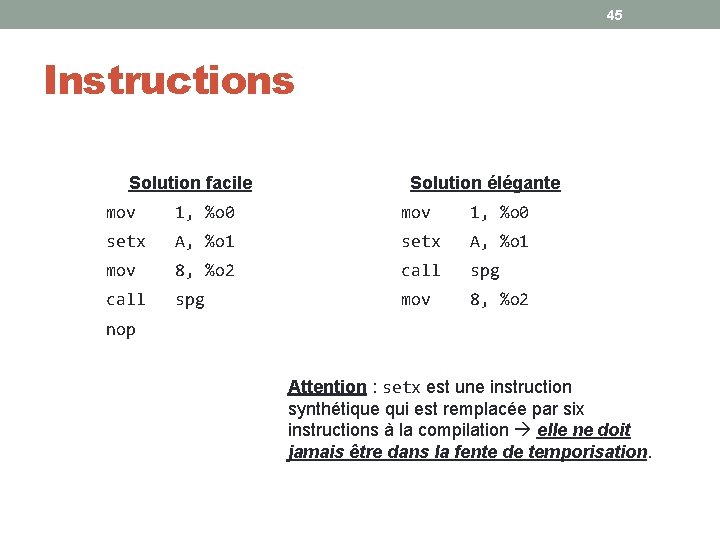

44 Instructions • Sur l’architecture SPARC, l’instruction qui suit un branchement est toujours exécutée (pipeline). • Cette instruction se trouve dans la fente de temporisation ( « delay slot » ) • Le programmeur doit en tenir compte et mettre une instruction qui n’altère pas le traitement souhaité • NOP : Instruction synthétique dérivée de SETHI 0, %g 0

45 Instructions Solution facile Solution élégante mov 1, %o 0 setx A, %o 1 mov 8, %o 2 call spg mov 8, %o 2 nop Attention : setx est une instruction synthétique qui est remplacée par six instructions à la compilation elle ne doit jamais être dans la fente de temporisation.