1 CHAPITRE 11 Les nombres virgule flottante 2

1 CHAPITRE 11 Les nombres à virgule flottante

2 Représentation •

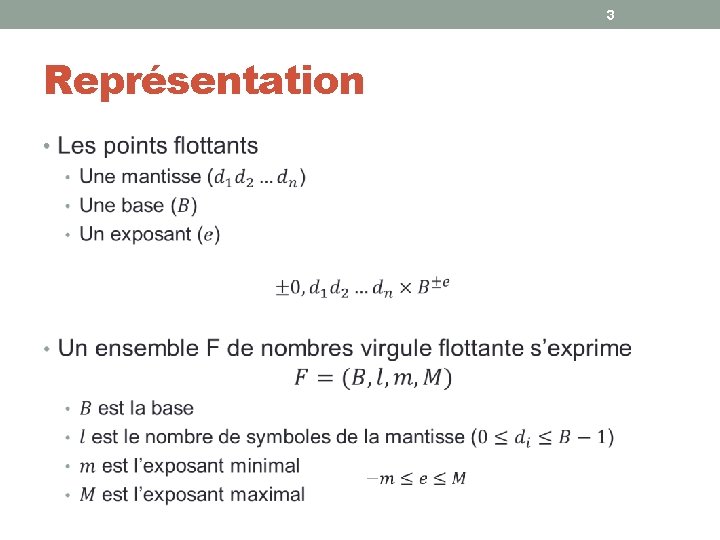

3 Représentation •

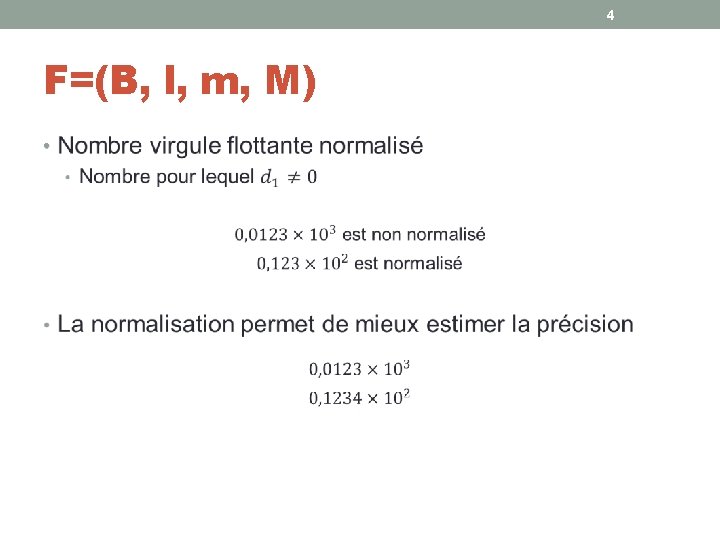

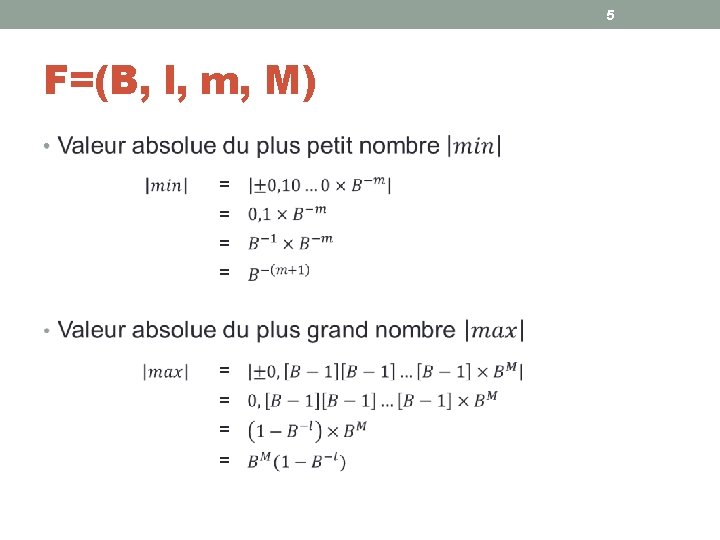

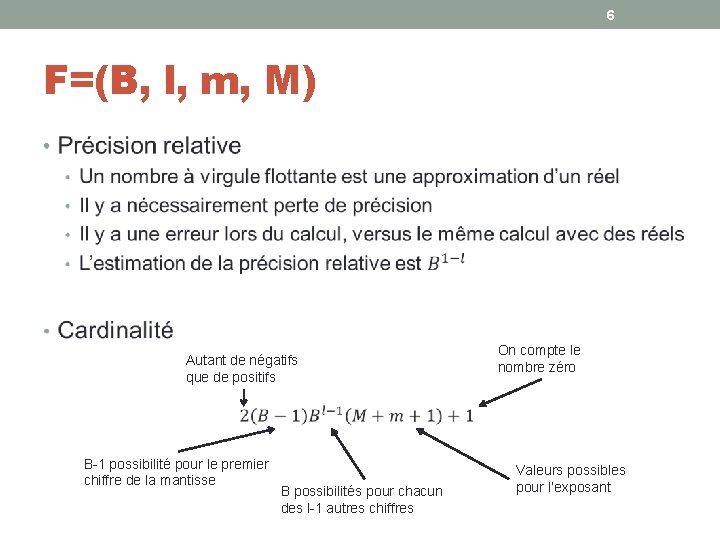

6 F=(B, l, m, M) • Autant de négatifs que de positifs On compte le nombre zéro B-1 possibilité pour le premier chiffre de la mantisse B possibilités pour chacun des l-1 autres chiffres Valeurs possibles pour l’exposant

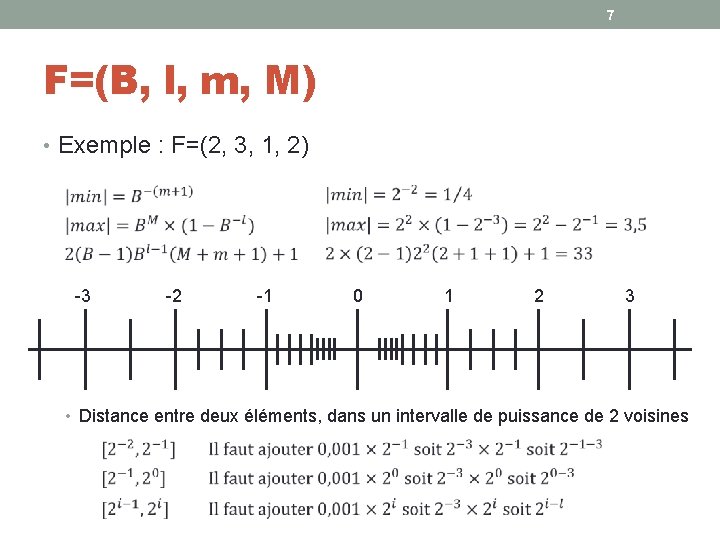

7 F=(B, l, m, M) • Exemple : F=(2, 3, 1, 2) -3 -2 -1 0 1 2 3 • Distance entre deux éléments, dans un intervalle de puissance de 2 voisines

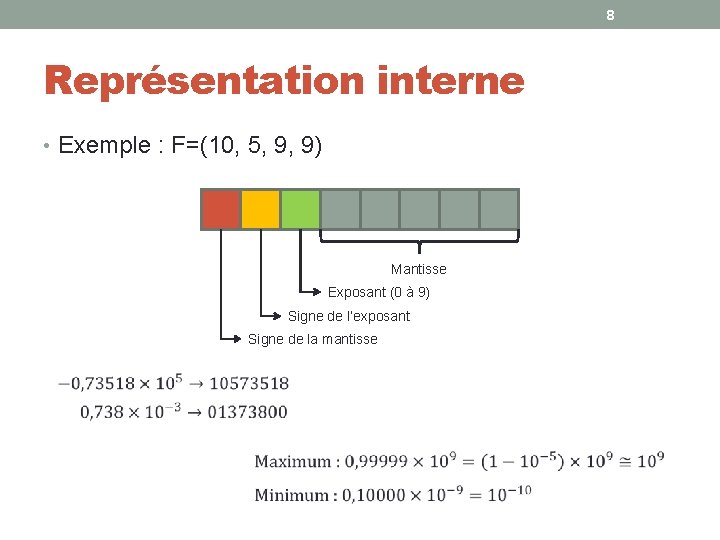

8 Représentation interne • Exemple : F=(10, 5, 9, 9) Mantisse Exposant (0 à 9) Signe de l’exposant Signe de la mantisse

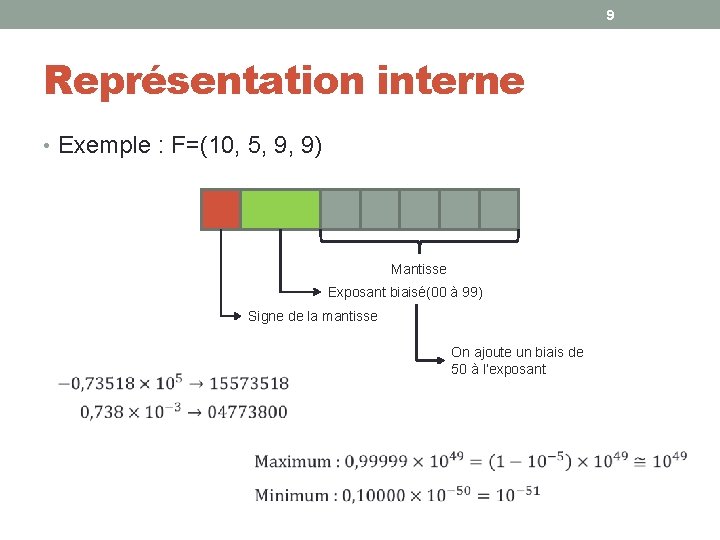

9 Représentation interne • Exemple : F=(10, 5, 9, 9) Mantisse Exposant biaisé(00 à 99) Signe de la mantisse On ajoute un biais de 50 à l’exposant

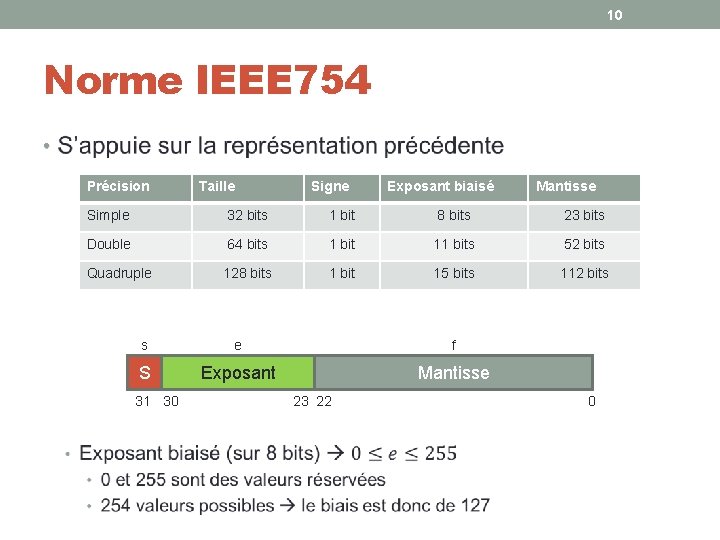

10 Norme IEEE 754 • Précision Taille Signe Exposant biaisé Mantisse Simple 32 bits 1 bit 8 bits 23 bits Double 64 bits 1 bit 11 bits 52 bits Quadruple 128 bits 1 bit 15 bits 112 bits s e f S Exposant Mantisse 31 30 23 22 0

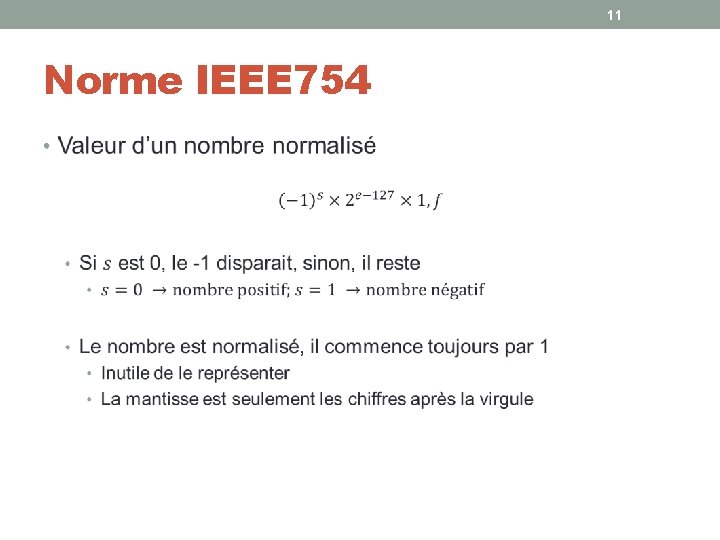

11 Norme IEEE 754 •

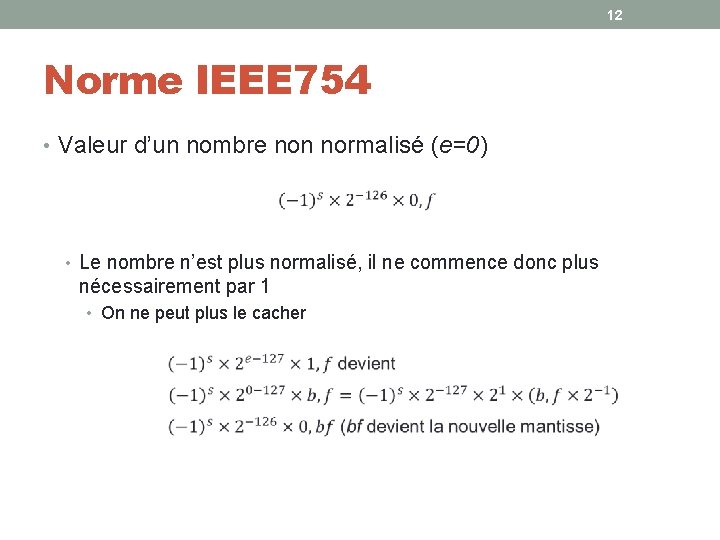

12 Norme IEEE 754 • Valeur d’un nombre non normalisé (e=0) • Le nombre n’est plus normalisé, il ne commence donc plus nécessairement par 1 • On ne peut plus le cacher

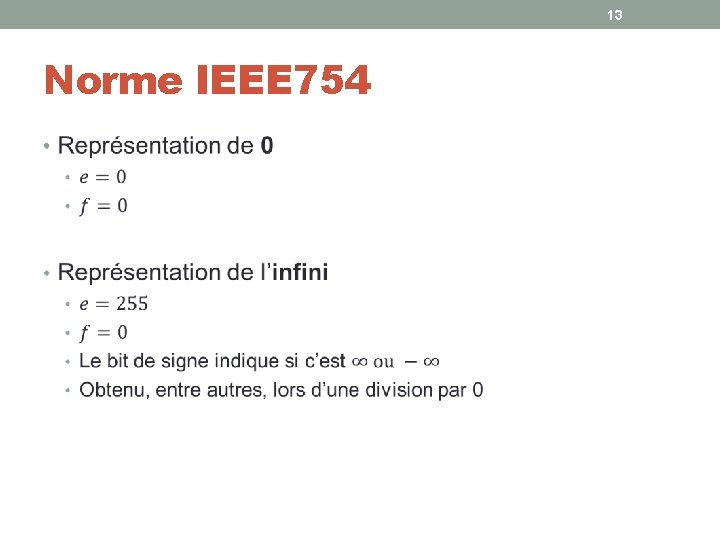

13 Norme IEEE 754 •

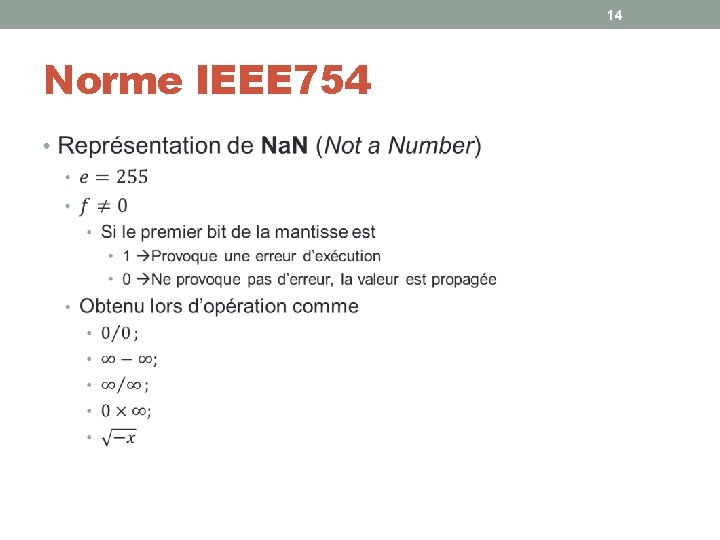

14 Norme IEEE 754 •

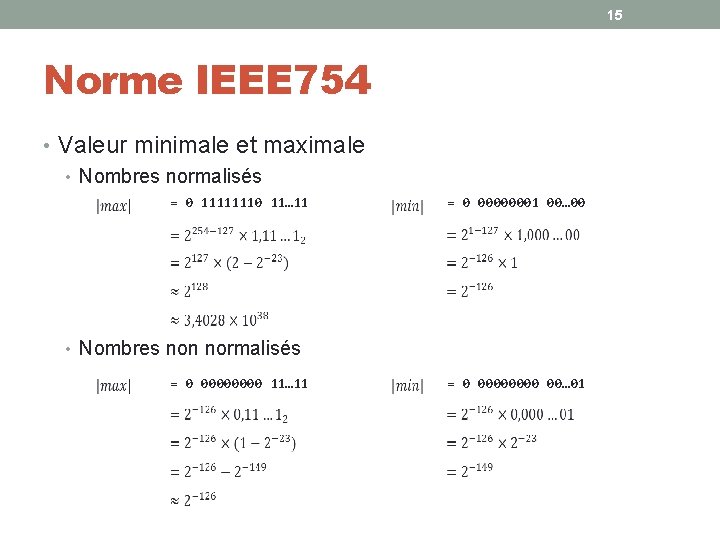

15 Norme IEEE 754 • Valeur minimale et maximale • Nombres normalisés = 0 11111110 11… 11 = 0 00000001 00… 00 • Nombres non normalisés = 0 0000 11… 11 = 0 0000 00… 01

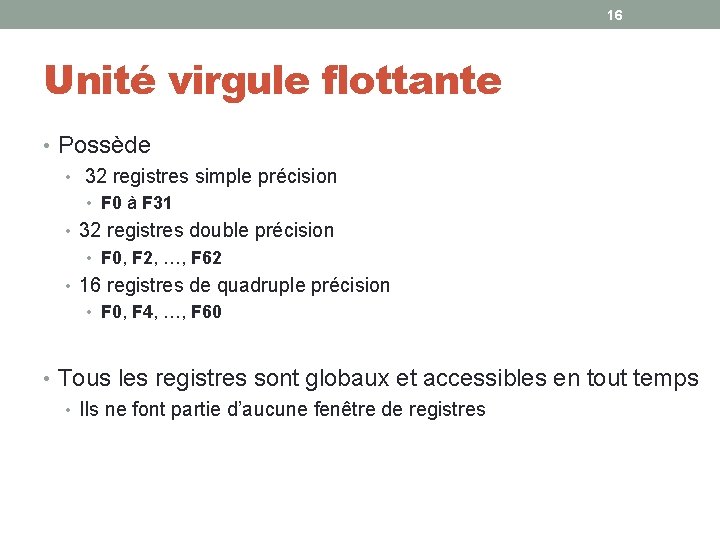

16 Unité virgule flottante • Possède • 32 registres simple précision • F 0 à F 31 • 32 registres double précision • F 0, F 2, …, F 62 • 16 registres de quadruple précision • F 0, F 4, …, F 60 • Tous les registres sont globaux et accessibles en tout temps • Ils ne font partie d’aucune fenêtre de registres

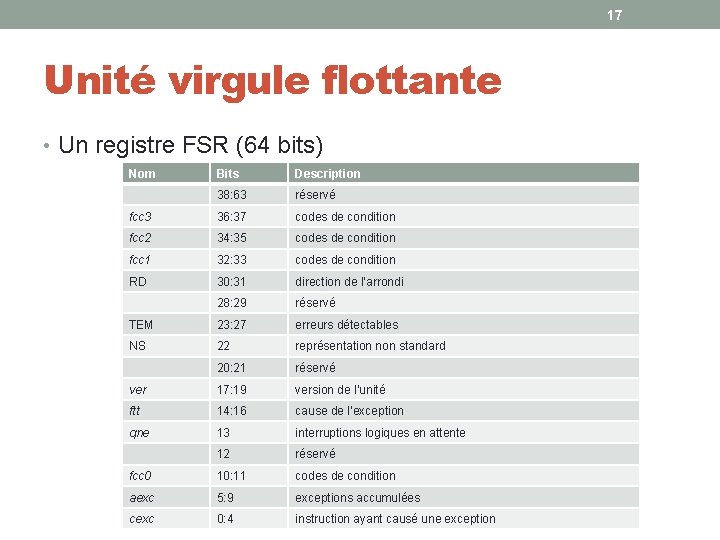

17 Unité virgule flottante • Un registre FSR (64 bits) Nom Bits Description 38: 63 réservé fcc 3 36: 37 codes de condition fcc 2 34: 35 codes de condition fcc 1 32: 33 codes de condition RD 30: 31 direction de l’arrondi 28: 29 réservé TEM 23: 27 erreurs détectables NS 22 représentation non standard 20: 21 réservé ver 17: 19 version de l’unité ftt 14: 16 cause de l’exception qne 13 interruptions logiques en attente 12 réservé fcc 0 10: 11 codes de condition aexc 5: 9 exceptions accumulées cexc 0: 4 instruction ayant causé une exception

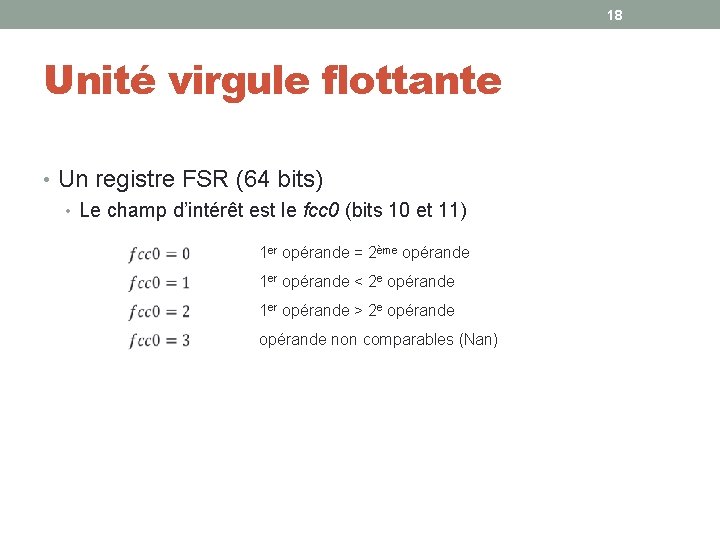

18 Unité virgule flottante • Un registre FSR (64 bits) • Le champ d’intérêt est le fcc 0 (bits 10 et 11) 1 er opérande = 2ème opérande 1 er opérande < 2 e opérande 1 er opérande > 2 e opérande non comparables (Nan)

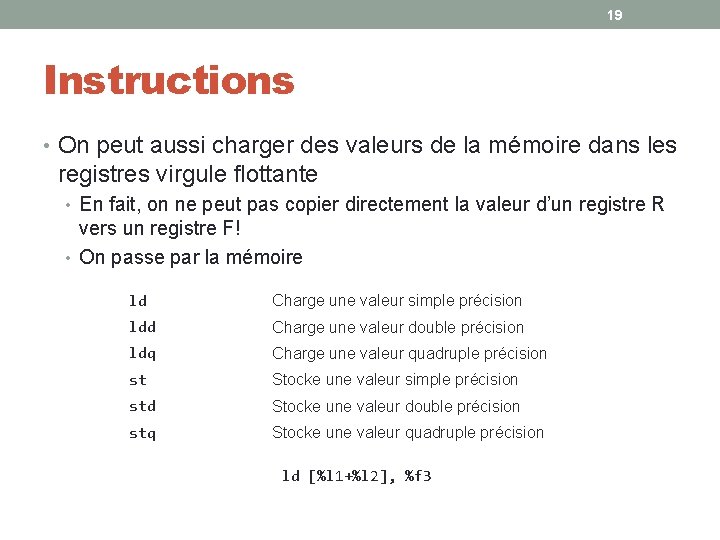

19 Instructions • On peut aussi charger des valeurs de la mémoire dans les registres virgule flottante • En fait, on ne peut pas copier directement la valeur d’un registre R vers un registre F! • On passe par la mémoire ld Charge une valeur simple précision ldd Charge une valeur double précision ldq Charge une valeur quadruple précision st Stocke une valeur simple précision std Stocke une valeur double précision stq Stocke une valeur quadruple précision ld [%l 1+%l 2], %f 3

20 Instructions • Les instructions arithmétiques sont légèrement modifiées pour prendre en charge les virgules flottantes • Voir annexe C. 14 du manuel pour la liste complète • On peut aussi faire des branchements sur les codes condition de l’unité virgule flottante • On ajoute un « f » devant les instructions normales de branchement • « bne » devient « fbne »

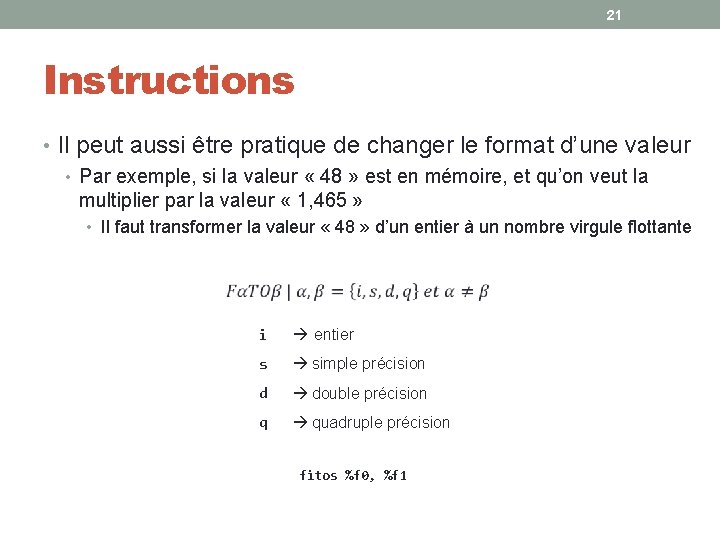

21 Instructions • Il peut aussi être pratique de changer le format d’une valeur • Par exemple, si la valeur « 48 » est en mémoire, et qu’on veut la multiplier par la valeur « 1, 465 » • Il faut transformer la valeur « 48 » d’un entier à un nombre virgule flottante i entier s simple précision d double précision q quadruple précision fitos %f 0, %f 1

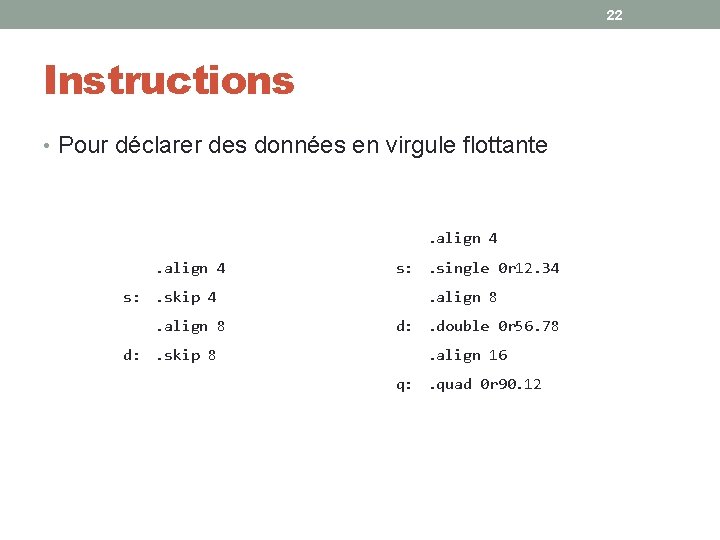

22 Instructions • Pour déclarer des données en virgule flottante . align 4 s: . skip 4. align 8 d: . skip 8 s: . single 0 r 12. 34. align 8 d: . double 0 r 56. 78. align 16 q: . quad 0 r 90. 12

- Slides: 22