1 Basics Microprocessor Microcontroller 2 What is Microcontroller

1 Basics Microprocessor & Microcontroller

2 What is Microcontroller? Micro Controller Very Small A mechanism that controls the operation of a machine

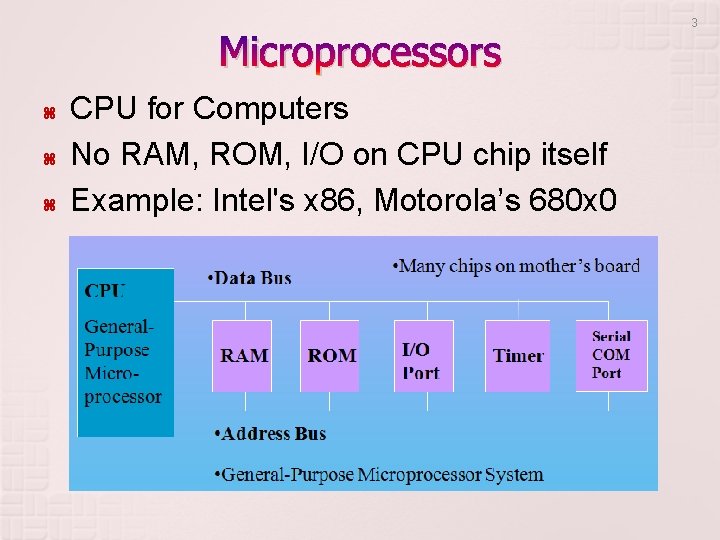

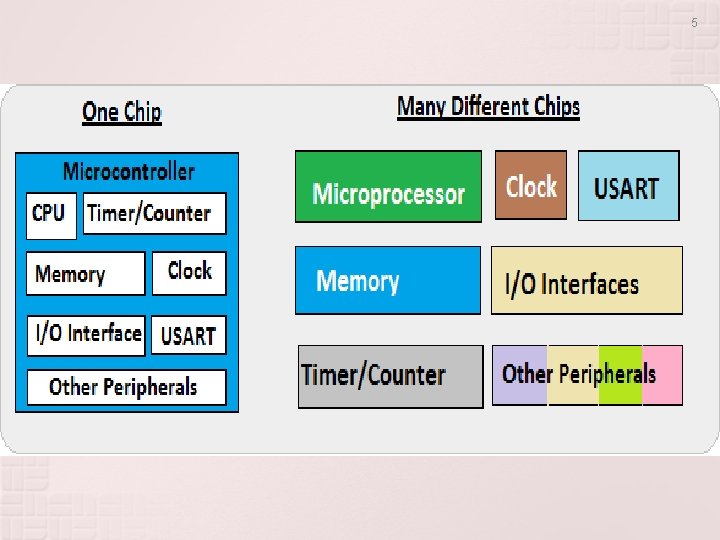

Microprocessors CPU for Computers No RAM, ROM, I/O on CPU chip itself Example: Intel's x 86, Motorola’s 680 x 0 3

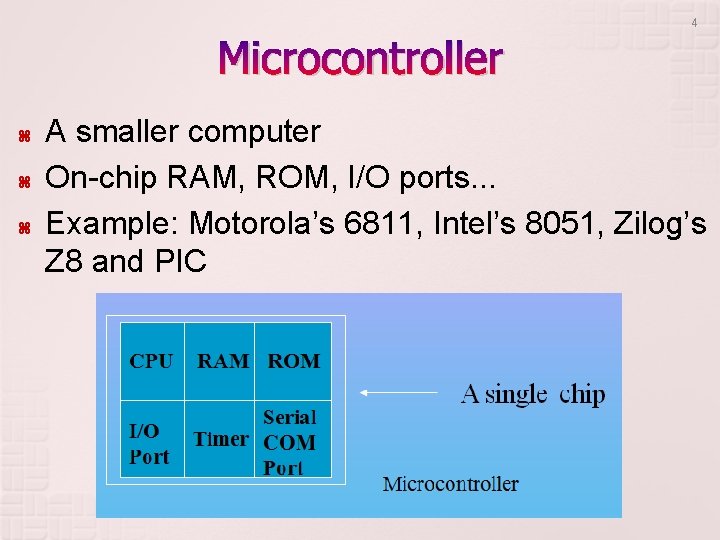

4 Microcontroller A smaller computer On-chip RAM, ROM, I/O ports. . . Example: Motorola’s 6811, Intel’s 8051, Zilog’s Z 8 and PIC

5

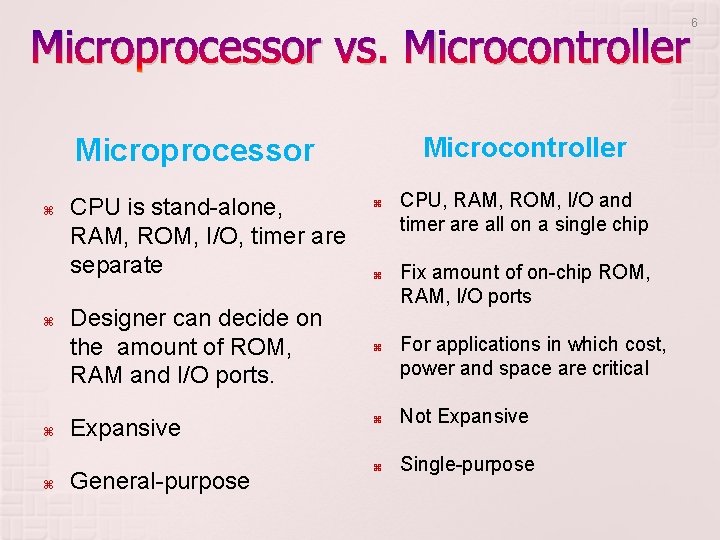

Microprocessor vs. Microcontroller Microprocessor CPU is stand-alone, RAM, ROM, I/O, timer are separate Designer can decide on the amount of ROM, RAM and I/O ports. Expansive General-purpose CPU, RAM, ROM, I/O and timer are all on a single chip Fix amount of on-chip ROM, RAM, I/O ports For applications in which cost, power and space are critical Not Expansive Single-purpose 6

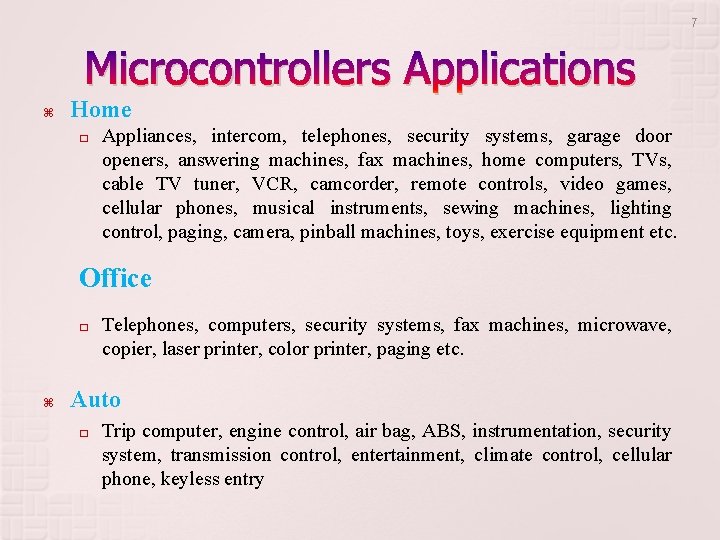

7 Microcontrollers Applications Home � Appliances, intercom, telephones, security systems, garage door openers, answering machines, fax machines, home computers, TVs, cable TV tuner, VCR, camcorder, remote controls, video games, cellular phones, musical instruments, sewing machines, lighting control, paging, camera, pinball machines, toys, exercise equipment etc. Office � Telephones, computers, security systems, fax machines, microwave, copier, laser printer, color printer, paging etc. Auto � Trip computer, engine control, air bag, ABS, instrumentation, security system, transmission control, entertainment, climate control, cellular phone, keyless entry

8

9 UNIT-4 8051 MICROCONTROLLER Presented by R. BENSCHWARTZ

UNIT 4 Syllabus • • • Architecture of 8051 Special Function Registers(SFRs) I/O Pins Ports and Circuits {Pin Diagram} Instruction set Addressing modes Assembly language programming 10

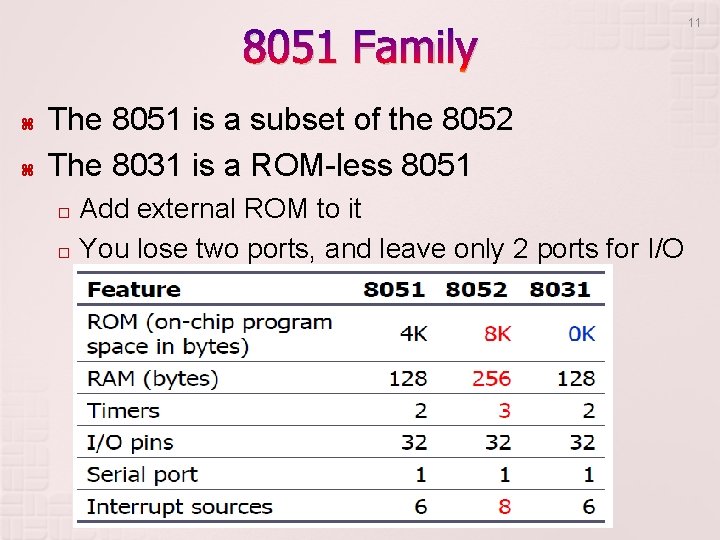

8051 Family 11 The 8051 is a subset of the 8052 The 8031 is a ROM-less 8051 Add external ROM to it � You lose two ports, and leave only 2 ports for I/O operations �

12

13 8051 Microcontroller Intel introduced 8051, developed in the year 1981. The 8051 is an 8 -bit controller. D 0 -D 7 DATA LINES � A 0 -A 15 ADDRESS LINES �

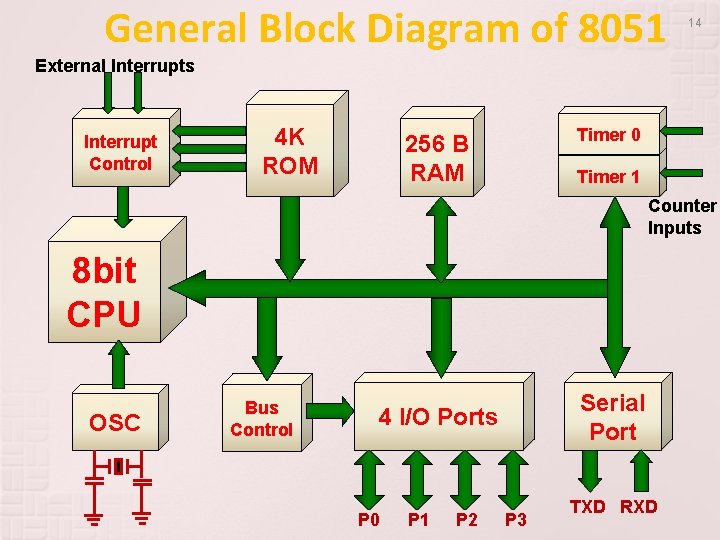

General Block Diagram of 8051 14 External Interrupts Interrupt Control 4 K ROM Timer 0 256 B RAM Timer 1 Counter Inputs 8 bit CPU OSC Bus Control Serial Port 4 I/O Ports P 0 P 1 P 2 P 3 TXD RXD

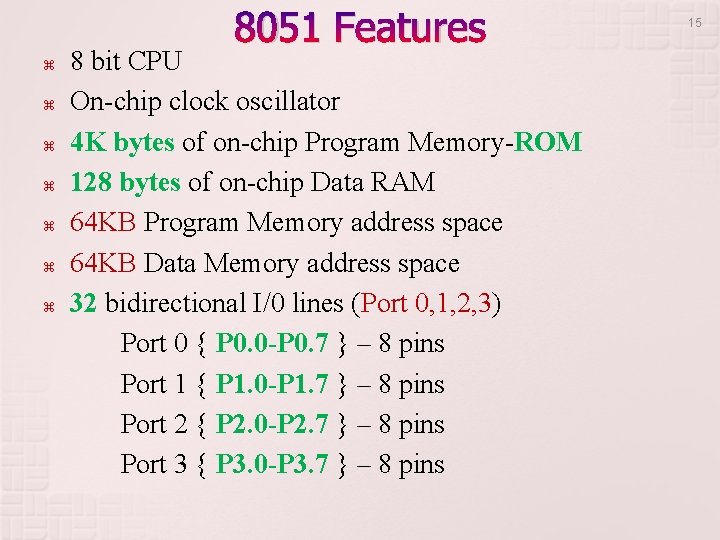

8051 Features 8 bit CPU On-chip clock oscillator 4 K bytes of on-chip Program Memory-ROM 128 bytes of on-chip Data RAM 64 KB Program Memory address space 64 KB Data Memory address space 32 bidirectional I/0 lines (Port 0, 1, 2, 3) Port 0 { P 0. 0 -P 0. 7 } – 8 pins Port 1 { P 1. 0 -P 1. 7 } – 8 pins Port 2 { P 2. 0 -P 2. 7 } – 8 pins Port 3 { P 3. 0 -P 3. 7 } – 8 pins 15

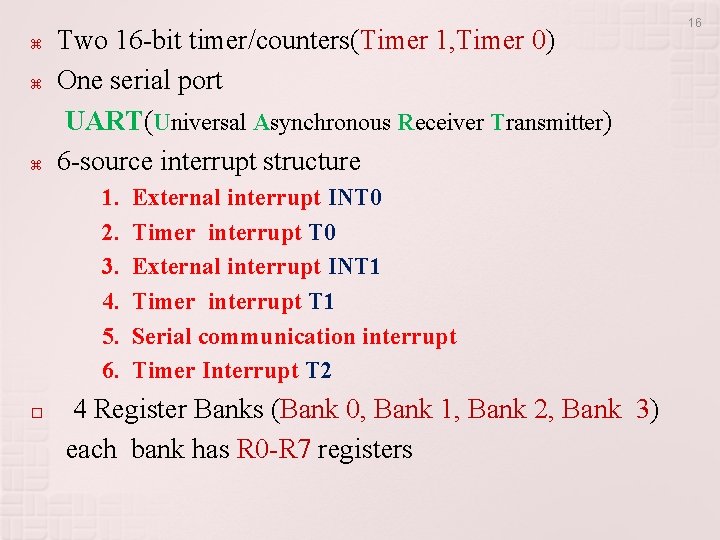

Two 16 -bit timer/counters(Timer 1, Timer 0) One serial port UART(Universal Asynchronous Receiver Transmitter) 6 -source interrupt structure 1. 2. 3. 4. 5. 6. � External interrupt INT 0 Timer interrupt T 0 External interrupt INT 1 Timer interrupt T 1 Serial communication interrupt Timer Interrupt T 2 4 Register Banks (Bank 0, Bank 1, Bank 2, Bank 3) each bank has R 0 -R 7 registers 16

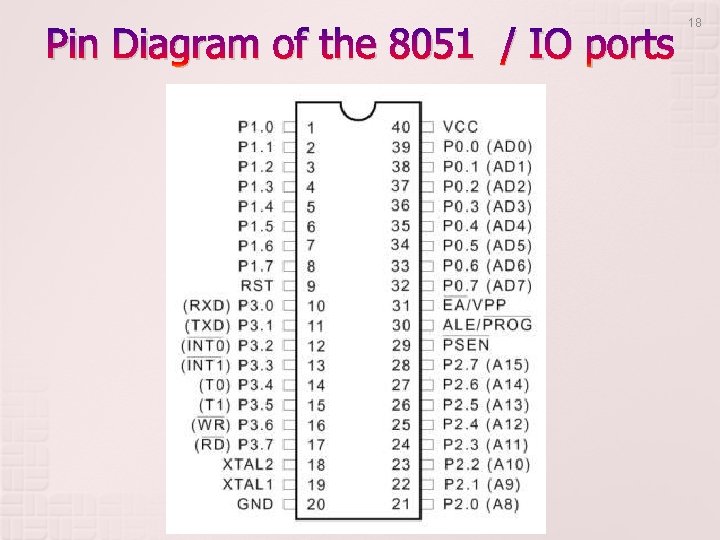

17 Pin Description of the 8051

Pin Diagram of the 8051 / IO ports 18

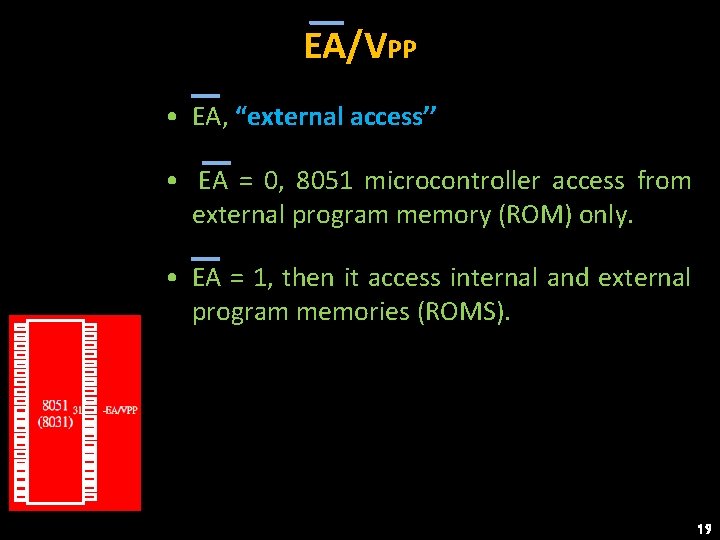

EA/VPP • EA, “external access’’ • EA = 0, 8051 microcontroller access from external program memory (ROM) only. • EA = 1, then it access internal and external program memories (ROMS). 19

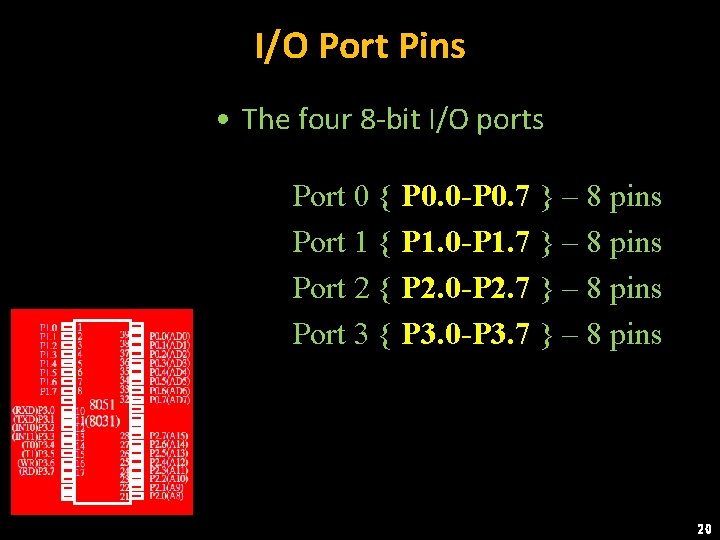

I/O Port Pins • The four 8 -bit I/O ports Port 0 { P 0. 0 -P 0. 7 } – 8 pins Port 1 { P 1. 0 -P 1. 7 } – 8 pins Port 2 { P 2. 0 -P 2. 7 } – 8 pins Port 3 { P 3. 0 -P 3. 7 } – 8 pins 20

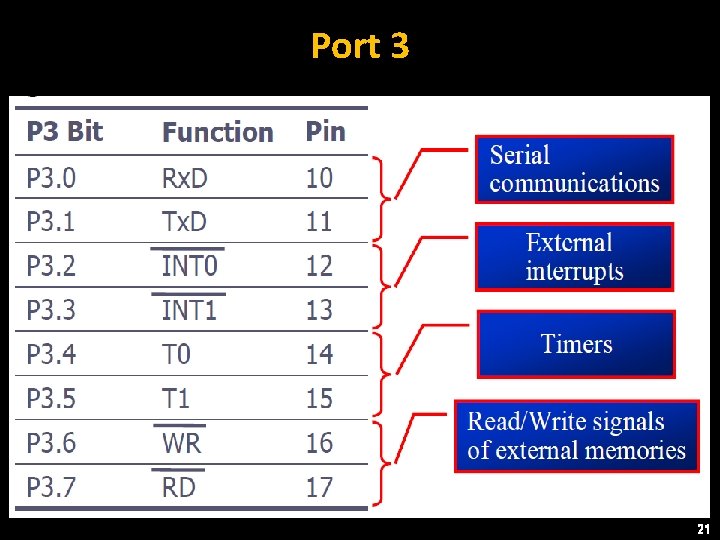

Port 3 • Port 3 can be used as input or output. • Port 3 has the additional function of providing some extremely important signals 21

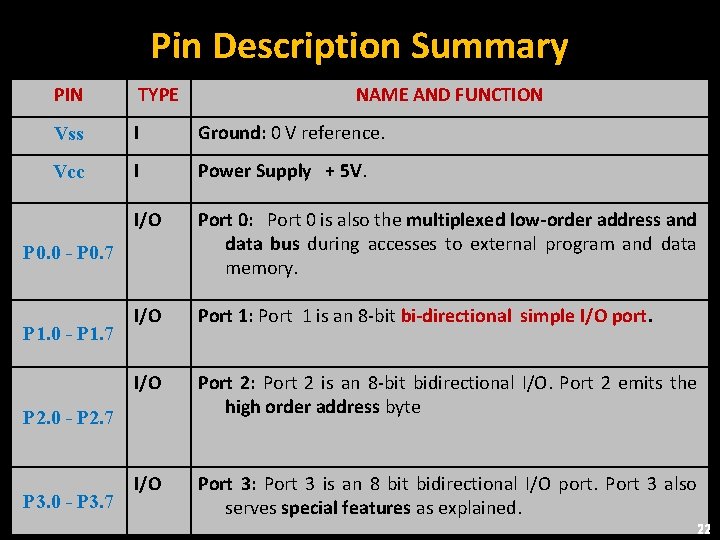

Pin Description Summary PIN TYPE Vss I Ground: 0 V reference. Vcc I Power Supply + 5 V. I/O Port 0: Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. I/O Port 1: Port 1 is an 8 -bit bi-directional simple I/O port. I/O Port 2: Port 2 is an 8 -bit bidirectional I/O. Port 2 emits the high order address byte I/O Port 3: Port 3 is an 8 bit bidirectional I/O port. Port 3 also serves special features as explained. P 0. 0 - P 0. 7 P 1. 0 - P 1. 7 P 2. 0 - P 2. 7 P 3. 0 - P 3. 7 NAME AND FUNCTION 22

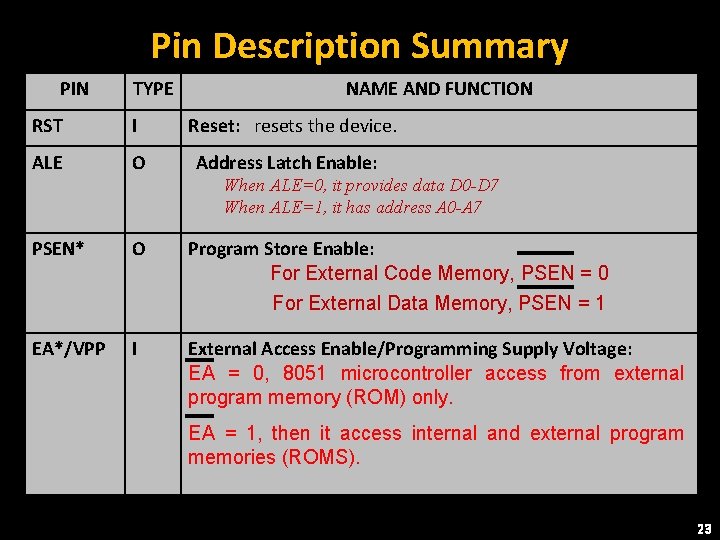

Pin Description Summary PIN TYPE RST I ALE O NAME AND FUNCTION Reset: resets the device. Address Latch Enable: When ALE=0, it provides data D 0 -D 7 When ALE=1, it has address A 0 -A 7 PSEN* O Program Store Enable: For External Code Memory, PSEN = 0 For External Data Memory, PSEN = 1 EA*/VPP I External Access Enable/Programming Supply Voltage: EA = 0, 8051 microcontroller access from external program memory (ROM) only. EA = 1, then it access internal and external program memories (ROMS). 23

Architecture of 8051 microcontroller 24

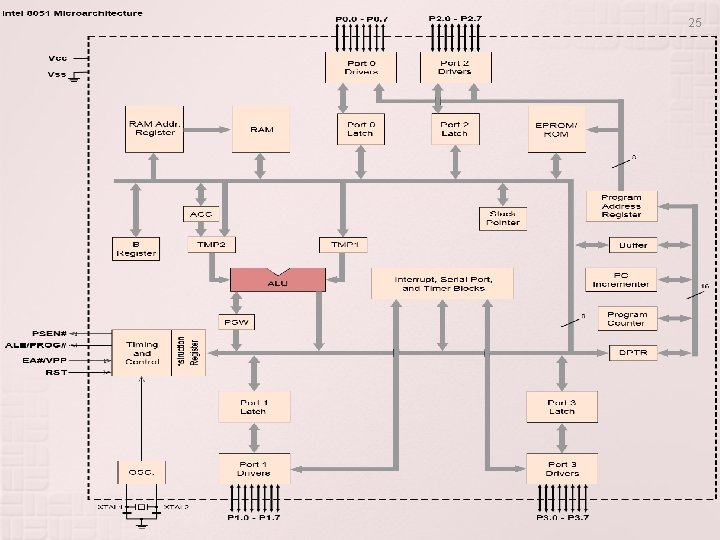

25

26

Program Counter(PC) : The program counter always points to the address of the next instruction to be executed. Stack Pointer Register (SP) : It is an 8 -bit register which stores the address of the stack top. ALU: perform arithmetic & logical operations Flags : Carry(C), Auxiliary Carry(AC), Overflow(O) & Parity(P) 27

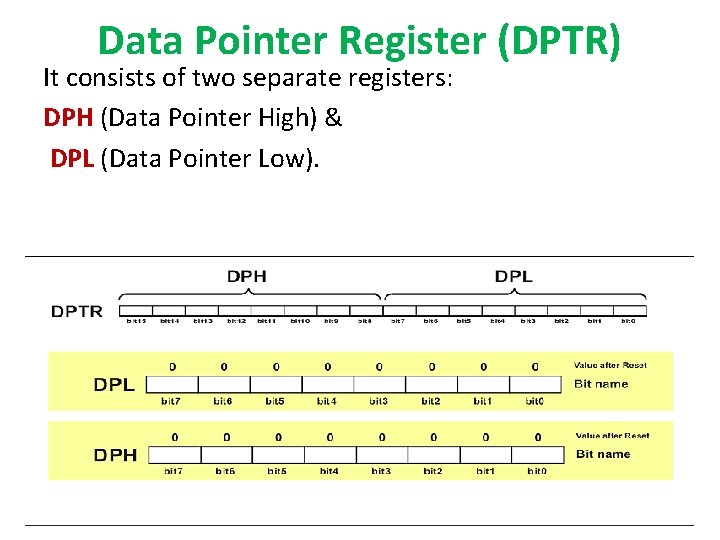

28 Timing & Control: Timing and control unit synchronises all microcontroller operations with clock & generates control signals. DPTR: (Data Pointer) - 16 bit DPH-Data Pointer High – 8 bit Y DPL-Data Pointer Low – 8 bit DPTR Register is usually used for storing data and intermediate results. Y

8051 Program Memory, Data Memory structure 29

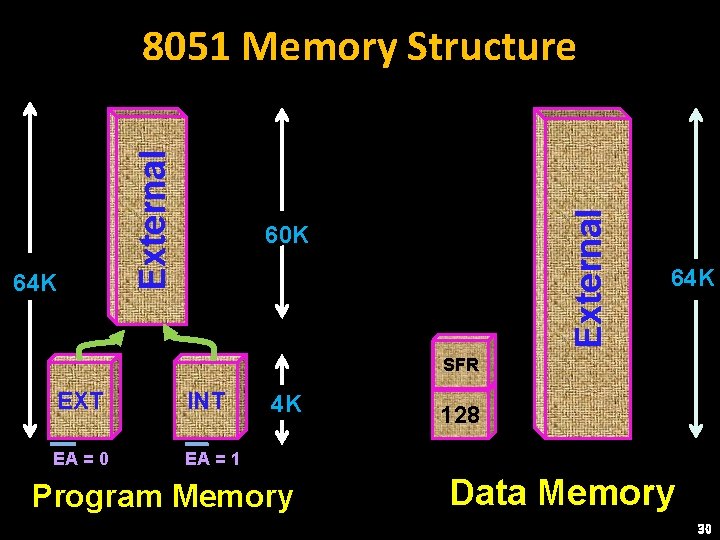

External 64 K External 8051 Memory Structure 60 K 64 K SFR EXT INT EA = 0 EA = 1 4 K Program Memory 128 Data Memory 30

![Special Function Registers [SFR] 31 Special Function Registers [SFR] 31](http://slidetodoc.com/presentation_image_h/0c42601851e22bcd5b8ad83f9a55e5c9/image-31.jpg)

Special Function Registers [SFR] 31

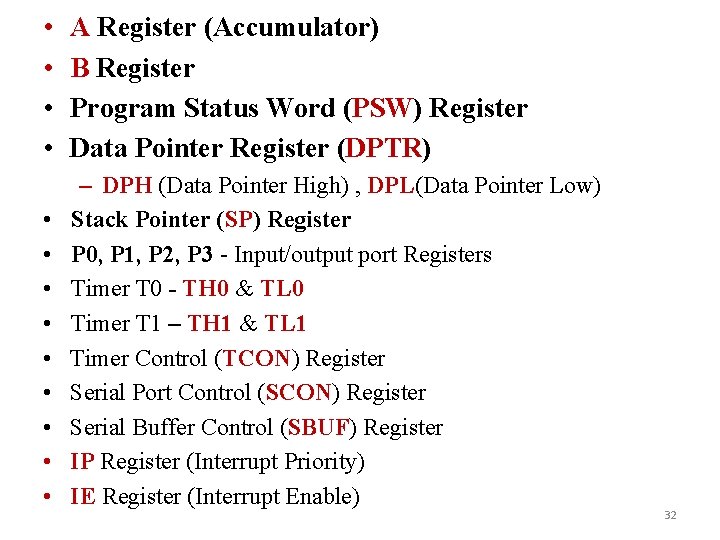

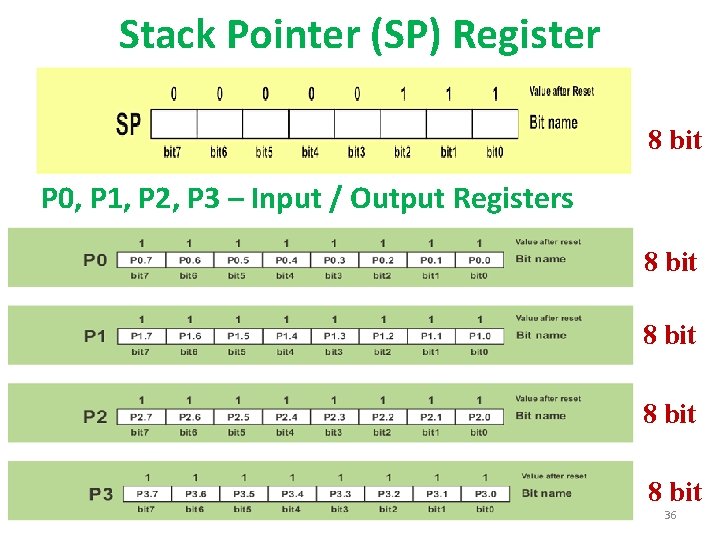

• • A Register (Accumulator) B Register Program Status Word (PSW) Register Data Pointer Register (DPTR) • • • – DPH (Data Pointer High) , DPL(Data Pointer Low) Stack Pointer (SP) Register P 0, P 1, P 2, P 3 - Input/output port Registers Timer T 0 - TH 0 & TL 0 Timer T 1 – TH 1 & TL 1 Timer Control (TCON) Register Serial Port Control (SCON) Register Serial Buffer Control (SBUF) Register IP Register (Interrupt Priority) IE Register (Interrupt Enable) 32

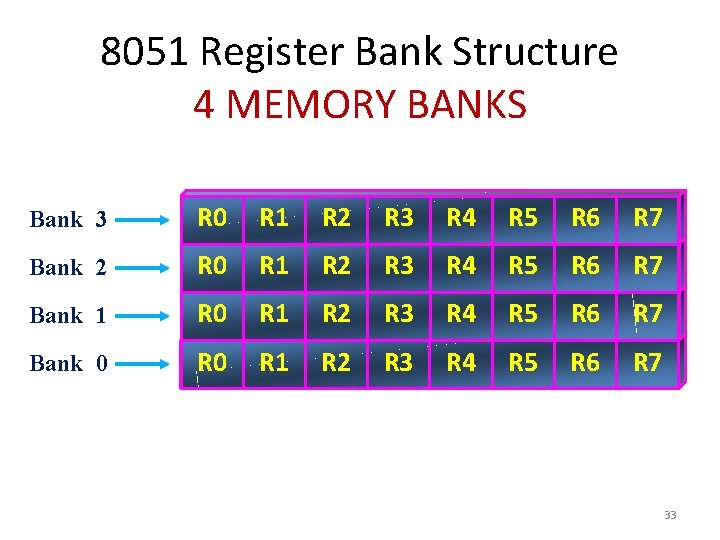

8051 Register Bank Structure 4 MEMORY BANKS Bank 3 R 0 R 1 R 2 R 3 R 4 R 5 R 6 R 7 Bank 2 R 0 R 1 R 2 R 3 R 4 R 5 R 6 R 7 Bank 1 R 0 R 1 R 2 R 3 R 4 R 5 R 6 R 7 Bank 0 R 1 R 2 R 3 R 4 R 5 R 6 R 7 33

![Program Status Word [PSW] C AC F 0 RS 1 RS 0 OV F Program Status Word [PSW] C AC F 0 RS 1 RS 0 OV F](http://slidetodoc.com/presentation_image_h/0c42601851e22bcd5b8ad83f9a55e5c9/image-34.jpg)

Program Status Word [PSW] C AC F 0 RS 1 RS 0 OV F 1 P Carry Parity Auxiliary Carry User Flag 0 User Flag 1 Register Bank Select Overflow 00 -Bank 0 01 -Bank 1 10 -Bank 2 11 -Bank 3 34

Data Pointer Register (DPTR) It consists of two separate registers: DPH (Data Pointer High) & DPL (Data Pointer Low). 35

Stack Pointer (SP) Register 8 bit P 0, P 1, P 2, P 3 – Input / Output Registers 8 bit 36

INSTRUCTION SET OF 8051 37

8051 Instruction Set • The instructions are grouped into 5 groups – Arithmetic – Logic – Data Transfer – Boolean – Branching 38

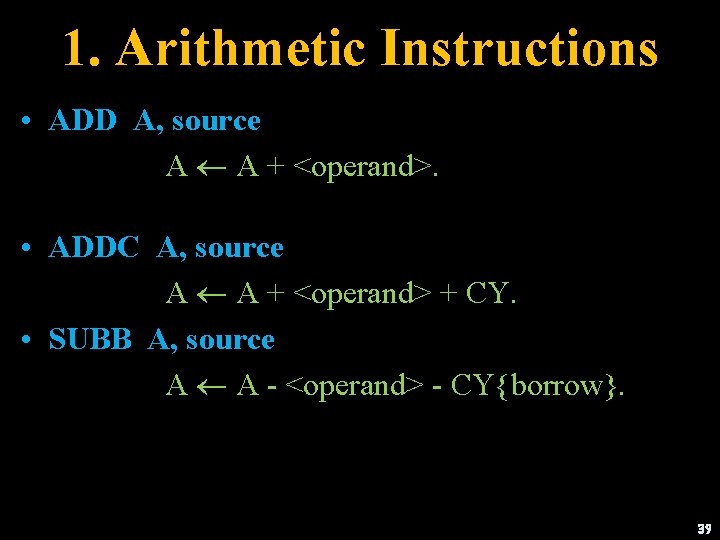

1. Arithmetic Instructions • ADD A, source A A + <operand>. • ADDC A, source A A + <operand> + CY. • SUBB A, source A A - <operand> - CY{borrow}. 39

• INC – Increment the operand by one. Ex: INC DPTR • DEC – Decrement the operand by one. Ex: DEC B • MUL AB Multiplication 8 byte * 8 byte A*B Result A=low byte, B=high byte • DIV AB Division 8 byte /8 byte A/B Quotient Remainder A B 40

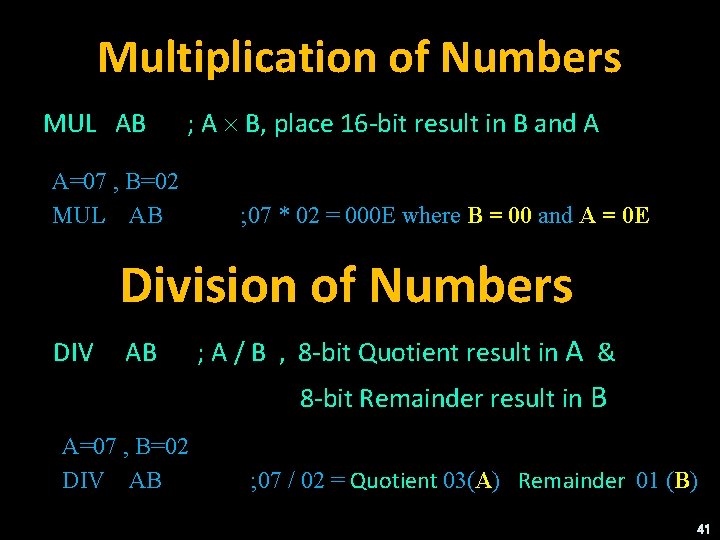

Multiplication of Numbers MUL AB ; A B, place 16 -bit result in B and A A=07 , B=02 MUL AB ; 07 * 02 = 000 E where B = 00 and A = 0 E Division of Numbers DIV AB ; A / B , 8 -bit Quotient result in A & 8 -bit Remainder result in B A=07 , B=02 DIV AB ; 07 / 02 = Quotient 03(A) Remainder 01 (B) = ) 41

2. Logical instructions 42

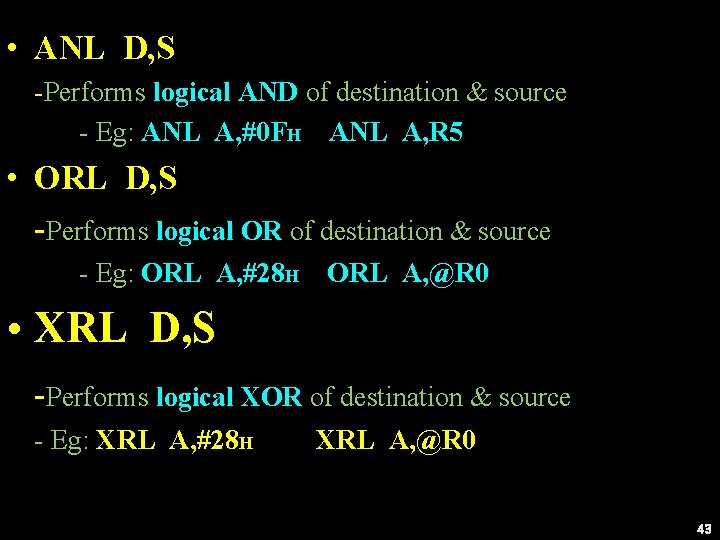

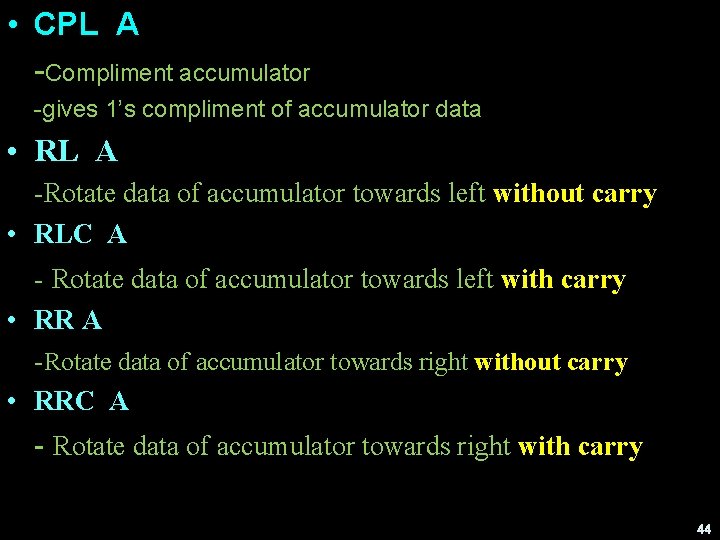

• ANL D, S -Performs logical AND of destination & source - Eg: ANL A, #0 FH ANL A, R 5 • ORL D, S -Performs logical OR of destination & source - Eg: ORL A, #28 H ORL A, @R 0 • XRL D, S -Performs logical XOR of destination & source - Eg: XRL A, #28 H XRL A, @R 0 43

• CPL A -Compliment accumulator -gives 1’s compliment of accumulator data • RL A -Rotate data of accumulator towards left without carry • RLC A - Rotate data of accumulator towards left with carry • RR A -Rotate data of accumulator towards right without carry • RRC A - Rotate data of accumulator towards right with carry 44

3. Data Transfer Instructions 45

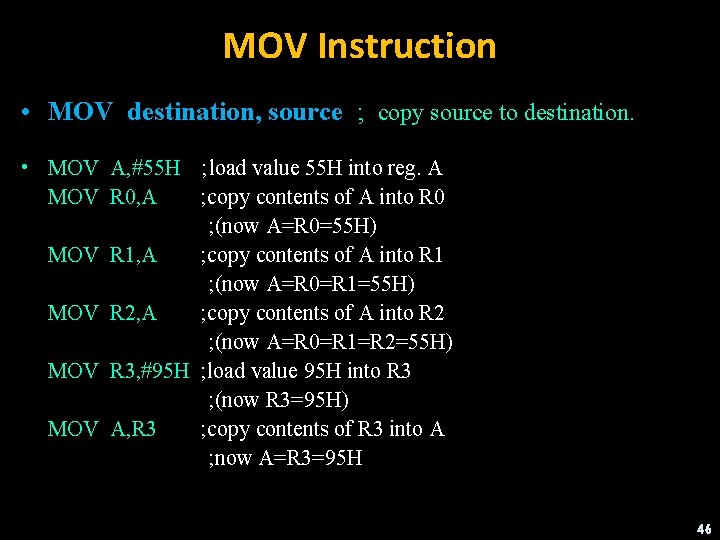

MOV Instruction • MOV destination, source ; copy source to destination. • MOV A, #55 H ; load value 55 H into reg. A MOV R 0, A ; copy contents of A into R 0 ; (now A=R 0=55 H) MOV R 1, A ; copy contents of A into R 1 ; (now A=R 0=R 1=55 H) MOV R 2, A ; copy contents of A into R 2 ; (now A=R 0=R 1=R 2=55 H) MOV R 3, #95 H ; load value 95 H into R 3 ; (now R 3=95 H) MOV A, R 3 ; copy contents of R 3 into A ; now A=R 3=95 H 46

• MOVX – Data transfer between the accumulator and a byte from external data memory. • MOVX A, @DPTR, A 47

• PUSH / POP – Push and Pop a data byte onto the stack. • PUSH • POP DPL 40 H 48

• XCH – Exchange accumulator and a byte variable • XCH A, Rn A, direct A, @Ri 49

4. Boolean variable instructions 50

CLR: • The operation clears the specified bit indicated in the instruction • Ex: CLR C clear the carry SETB: • The operation sets the specified bit to 1. CPL: • The operation complements the specified bit indicated in the instruction 51

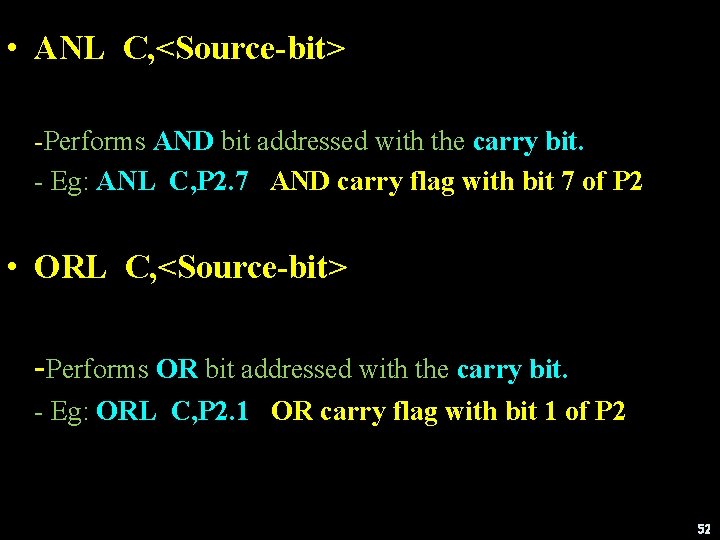

• ANL C, <Source-bit> -Performs AND bit addressed with the carry bit. - Eg: ANL C, P 2. 7 AND carry flag with bit 7 of P 2 • ORL C, <Source-bit> -Performs OR bit addressed with the carry bit. - Eg: ORL C, P 2. 1 OR carry flag with bit 1 of P 2 52

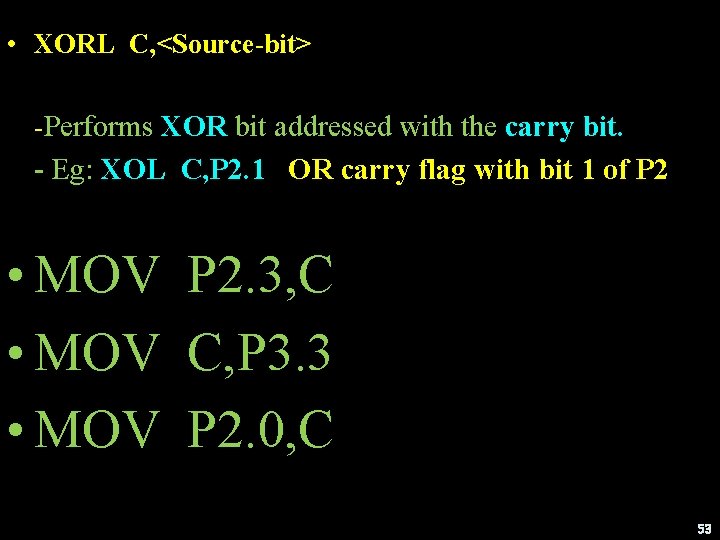

• XORL C, <Source-bit> -Performs XOR bit addressed with the carry bit. - Eg: XOL C, P 2. 1 OR carry flag with bit 1 of P 2 • MOV P 2. 3, C • MOV C, P 3. 3 • MOV P 2. 0, C 53

5. Branching instructions 54

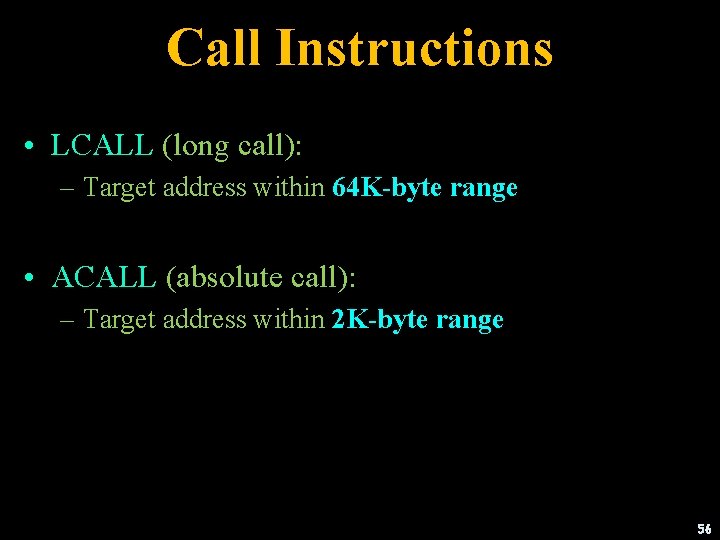

Jump Instructions • LJMP (long jump): – Original 8051 has only 4 KB on-chip ROM • SJMP (short jump): – 1 -byte relative address: -128 to +127 55

Call Instructions • LCALL (long call): – Target address within 64 K-byte range • ACALL (absolute call): – Target address within 2 K-byte range 56

• 2 forms for the return instruction: – Return from subroutine – RET – Return from ISR – RETI 57

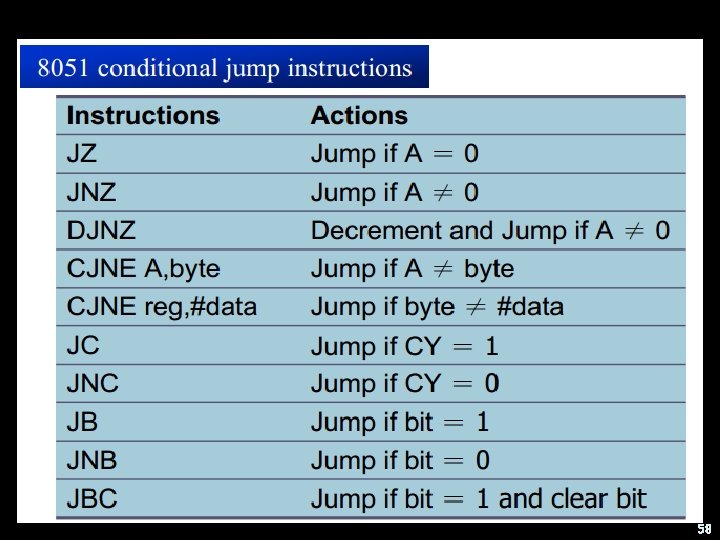

58

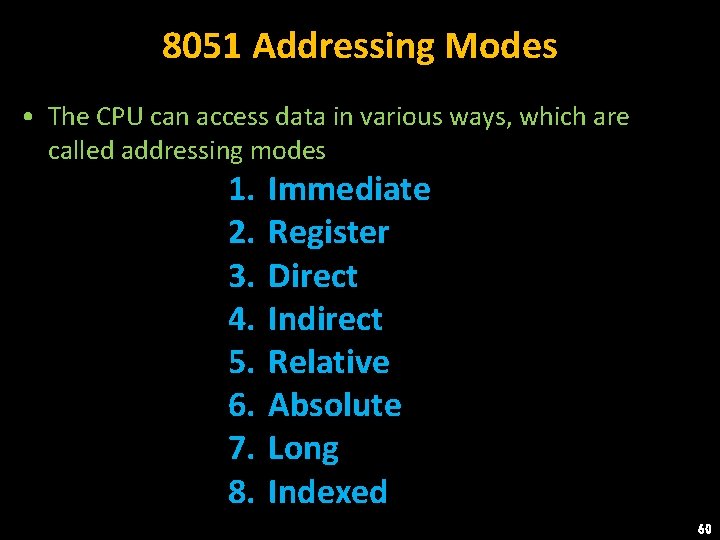

8051 Addressing Modes

8051 Addressing Modes • The CPU can access data in various ways, which are called addressing modes 1. 2. 3. 4. 5. 6. 7. 8. Immediate Register Direct Indirect Relative Absolute Long Indexed 60

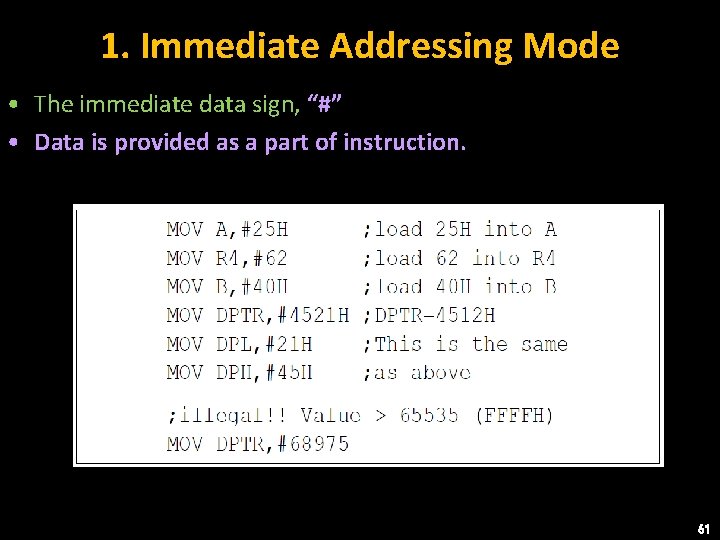

1. Immediate Addressing Mode • The immediate data sign, “#” • Data is provided as a part of instruction. 61

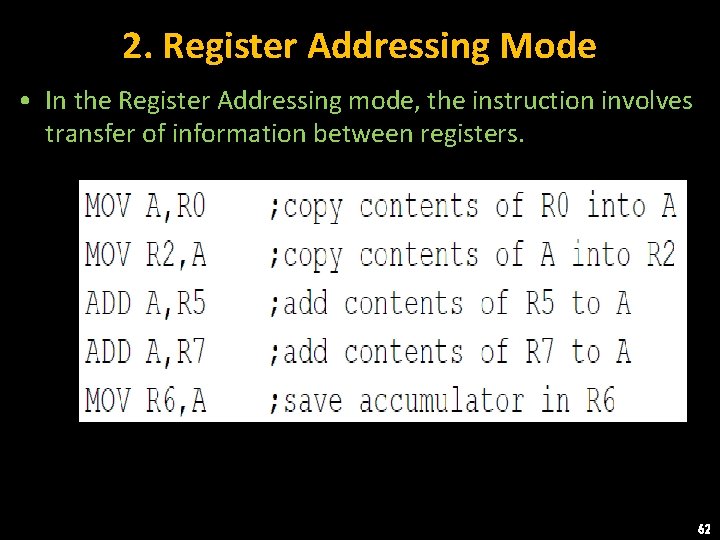

2. Register Addressing Mode • In the Register Addressing mode, the instruction involves transfer of information between registers. 62

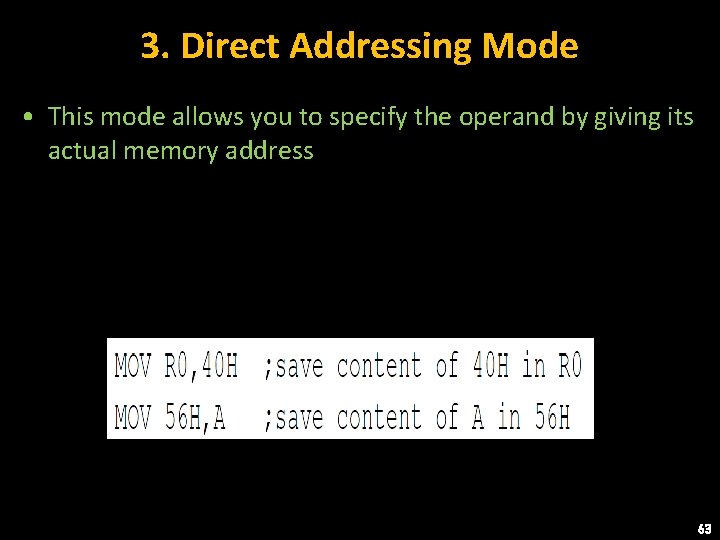

3. Direct Addressing Mode • This mode allows you to specify the operand by giving its actual memory address 63

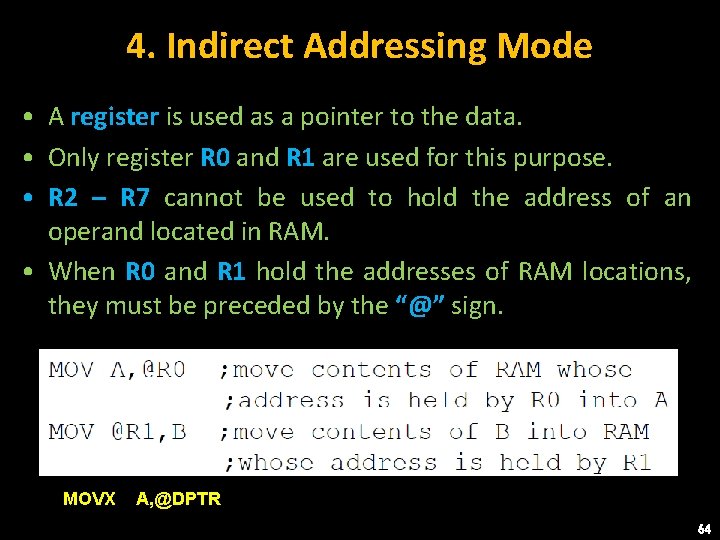

4. Indirect Addressing Mode • A register is used as a pointer to the data. • Only register R 0 and R 1 are used for this purpose. • R 2 – R 7 cannot be used to hold the address of an operand located in RAM. • When R 0 and R 1 hold the addresses of RAM locations, they must be preceded by the “@” sign. MOVX A, @DPTR 64

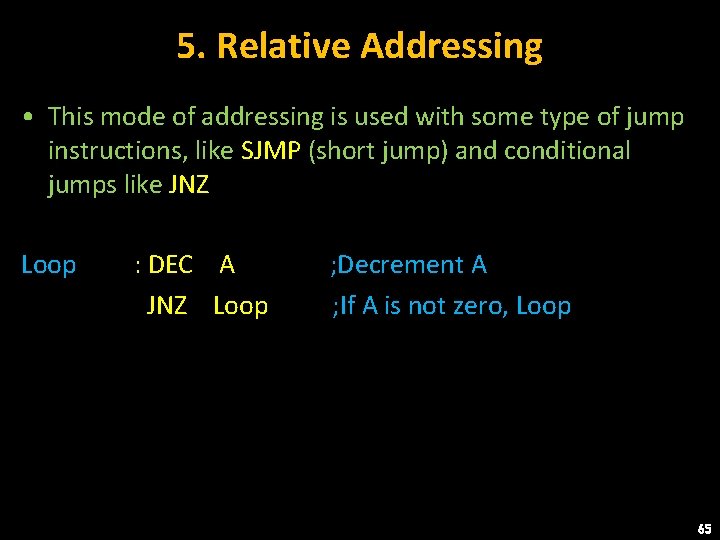

5. Relative Addressing • This mode of addressing is used with some type of jump instructions, like SJMP (short jump) and conditional jumps like JNZ Loop : DEC A ; Decrement A JNZ Loop ; If A is not zero, Loop 65

6. Absolute Addressing • In Absolute Addressing mode, the absolute address, to which the control is transferred, is specified by a label. • Two instructions associated with this mode of addressing are ACALL and AJMP instructions. • These are 2 -byte instructions 66

7. Long Addressing • This mode of addressing is used with the LCALL and LJMP instructions. • It is a 3 -byte instruction • It allows use of the full 64 K code space. 67

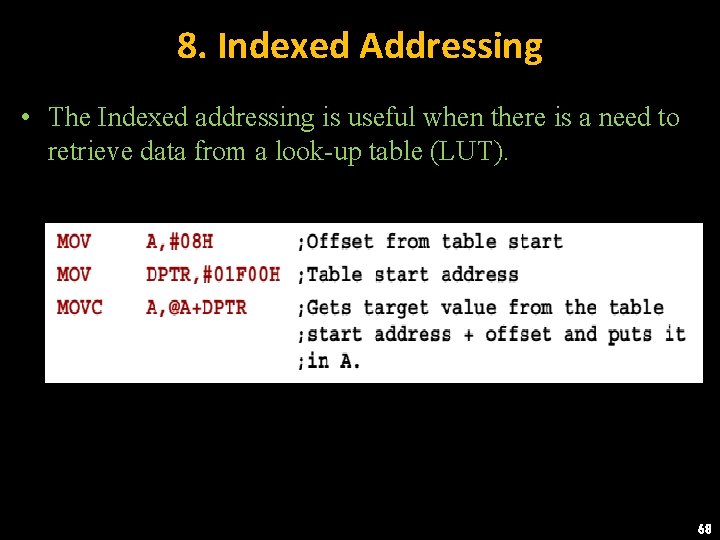

8. Indexed Addressing • The Indexed addressing is useful when there is a need to retrieve data from a look-up table (LUT). 68

8051 Assembly Language Programming(ALP) 69

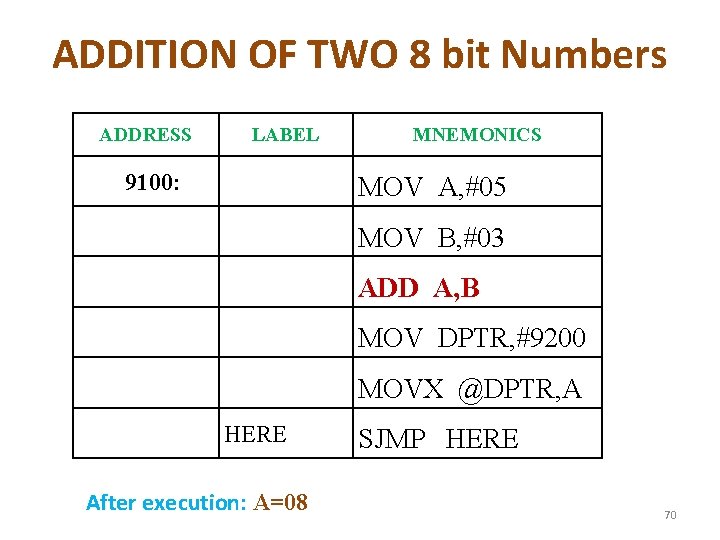

ADDITION OF TWO 8 bit Numbers ADDRESS LABEL 9100: MNEMONICS MOV A, #05 MOV B, #03 ADD A, B MOV DPTR, #9200 MOVX @DPTR, A HERE After execution: A=08 SJMP HERE 70

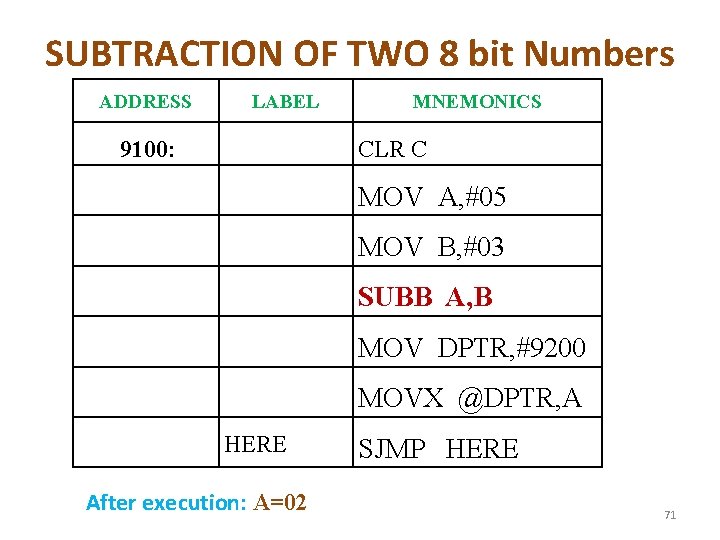

SUBTRACTION OF TWO 8 bit Numbers ADDRESS LABEL 9100: MNEMONICS CLR C MOV A, #05 MOV B, #03 SUBB A, B MOV DPTR, #9200 MOVX @DPTR, A HERE After execution: A=02 SJMP HERE 71

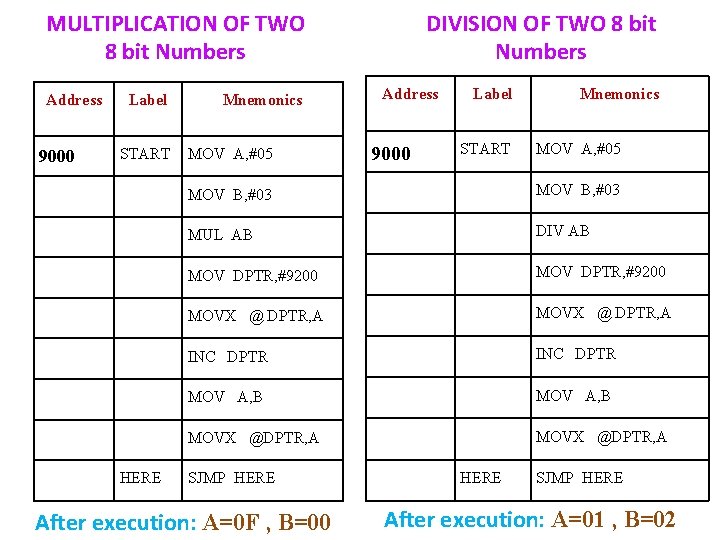

MULTIPLICATION OF TWO 8 bit Numbers Address 9000 Label START HERE Mnemonics MOV A, #05 DIVISION OF TWO 8 bit Numbers Address 9000 Label START Mnemonics MOV A, #05 MOV B, #03 MUL AB DIV AB MOV DPTR, #9200 MOVX @ DPTR, A INC DPTR MOV A, B MOVX @DPTR, A SJMP HERE After execution: A=0 F , B=00 HERE SJMP HERE After execution: A=01 , B=02

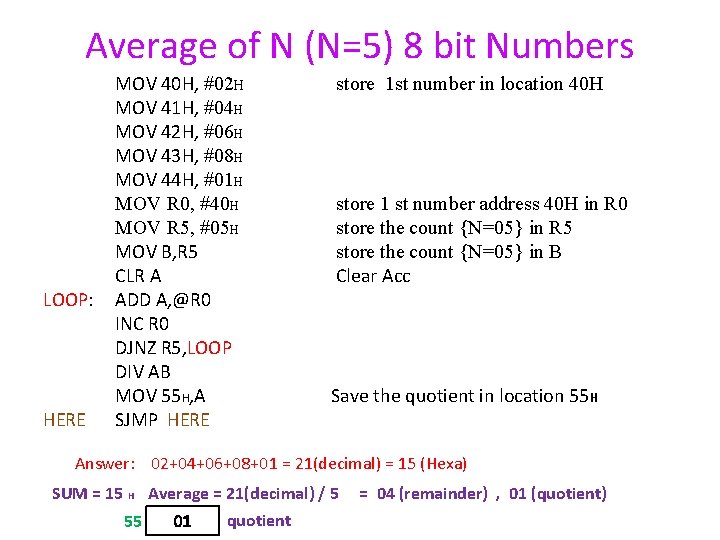

Average of N (N=5) 8 bit Numbers MOV 40 H, #02 H MOV 41 H, #04 H MOV 42 H, #06 H MOV 43 H, #08 H MOV 44 H, #01 H MOV R 0, #40 H MOV R 5, #05 H MOV B, R 5 CLR A LOOP: ADD A, @R 0 INC R 0 DJNZ R 5, LOOP DIV AB MOV 55 H, A HERE SJMP HERE store 1 st number in location 40 H store 1 st number address 40 H in R 0 store the count {N=05} in R 5 store the count {N=05} in B Clear Acc Save the quotient in location 55 H Answer: 02+04+06+08+01 = 21(decimal) = 15 (Hexa) SUM = 15 H Average = 21(decimal) / 5 55 01 quotient = 04 (remainder) , 01 (quotient)

- Slides: 73