1 8051 Microcontroller Architecture Prepared by Atul Marutirao

1. 8051 Microcontroller Architecture Prepared by: Atul Marutirao Kulkarni Lecturer, Electronics and Teleco. Engineering Dr. Babasaheb Ambedkar Tech. Uni. Institute of Petrochemical Engineering Lonere, Maharashtra Email: amkulkarni@dbatu. ac. in Website: atulkulkarnisite. wordpress. com This work is licensed under the Creative Commons Attribution-Non commercial-Share Alike 4. 0 International License. You are free to use, distribute and modify it, but not for commercial purposes, provided you acknowledge the source and share-alike. To view a copy of this license, visit https: //creativecommons. org/licenses/by-nc-sa/4. 0/ Atul M Kulkarni, Dr. Babasaheb Ambedkar Technological University, Lonere 1

2 Examples of Embedded Systems • Keyboard • Printer • video game player • MP 3 music players • Embedded memories to keep configuration information • Mobile phone units • Domestic (home) appliances • Data switches • Automotive controls Atul M Kulkarni, Dr. Babasaheb Ambedkar Technological University, Lonere 2

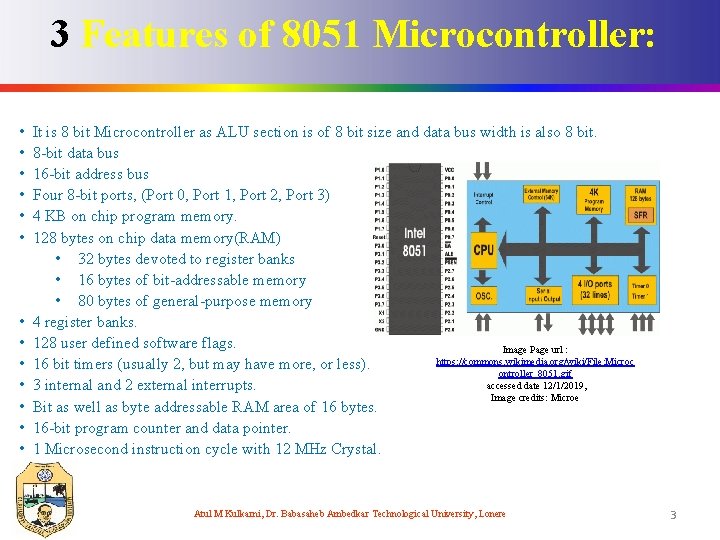

3 Features of 8051 Microcontroller: • • • • It is 8 bit Microcontroller as ALU section is of 8 bit size and data bus width is also 8 bit. 8 -bit data bus 16 -bit address bus Four 8 -bit ports, (Port 0, Port 1, Port 2, Port 3) 4 KB on chip program memory. 128 bytes on chip data memory(RAM) • 32 bytes devoted to register banks • 16 bytes of bit-addressable memory • 80 bytes of general-purpose memory 4 register banks. 128 user defined software flags. Image Page url : https: //commons. wikimedia. org/wiki/File: Microc 16 bit timers (usually 2, but may have more, or less). ontroller_8051. gif accessed date 12/1/2019, 3 internal and 2 external interrupts. Image credits: Microe Bit as well as byte addressable RAM area of 16 bytes. 16 -bit program counter and data pointer. 1 Microsecond instruction cycle with 12 MHz Crystal. Atul M Kulkarni, Dr. Babasaheb Ambedkar Technological University, Lonere 3

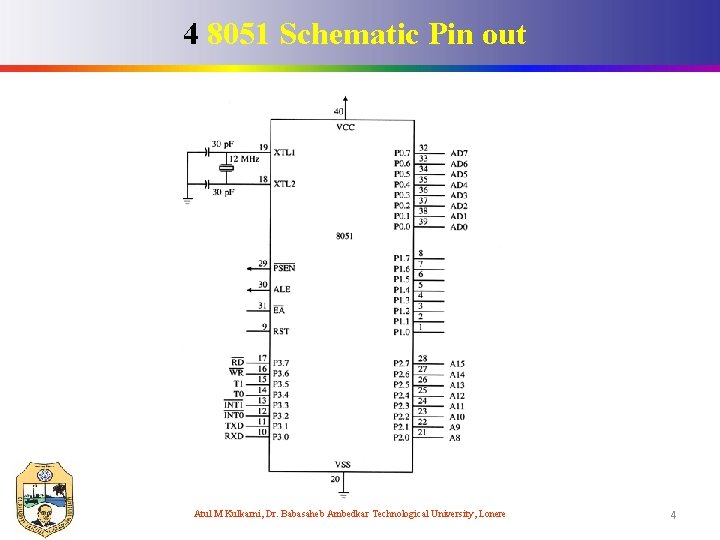

4 8051 Schematic Pin out Atul M Kulkarni, Dr. Babasaheb Ambedkar Technological University, Lonere 4

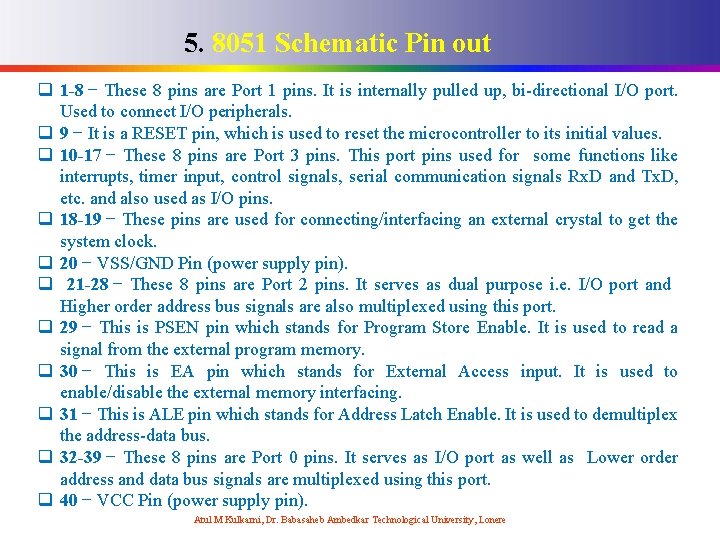

5. 8051 Schematic Pin out q 1 -8 − These 8 pins are Port 1 pins. It is internally pulled up, bi-directional I/O port. Used to connect I/O peripherals. q 9 − It is a RESET pin, which is used to reset the microcontroller to its initial values. q 10 -17 − These 8 pins are Port 3 pins. This port pins used for some functions like interrupts, timer input, control signals, serial communication signals Rx. D and Tx. D, etc. and also used as I/O pins. q 18 -19 − These pins are used for connecting/interfacing an external crystal to get the system clock. q 20 − VSS/GND Pin (power supply pin). q 21 -28 − These 8 pins are Port 2 pins. It serves as dual purpose i. e. I/O port and Higher order address bus signals are also multiplexed using this port. q 29 − This is PSEN pin which stands for Program Store Enable. It is used to read a signal from the external program memory. q 30 − This is EA pin which stands for External Access input. It is used to enable/disable the external memory interfacing. q 31 − This is ALE pin which stands for Address Latch Enable. It is used to demultiplex the address-data bus. q 32 -39 − These 8 pins are Port 0 pins. It serves as I/O port as well as Lower order address and data bus signals are multiplexed using this port. q 40 − VCC Pin (power supply pin). Atul M Kulkarni, Dr. Babasaheb Ambedkar Technological University, Lonere

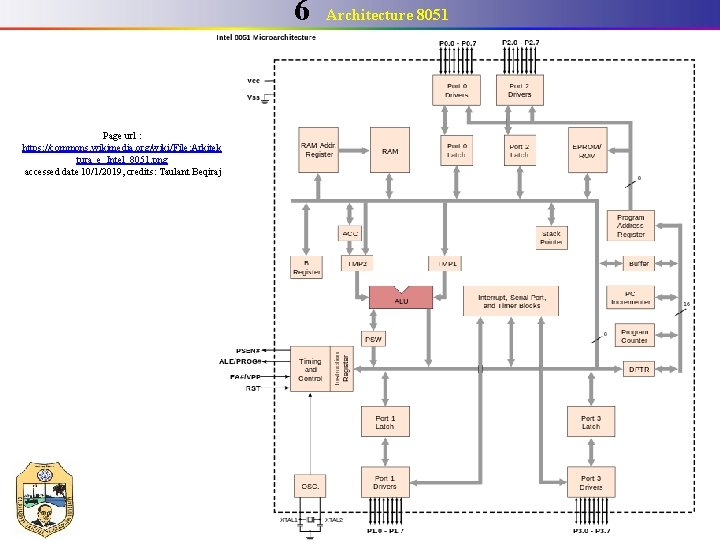

6 Page url : https: //commons. wikimedia. org/wiki/File: Arkitek tura_e_Intel_8051. png accessed date 10/1/2019, credits: Taulant Beqiraj Architecture 8051

7 Registers in 8051 1. Accumulator: The accumulator, register A, is used for all arithmetic and logic operations. 2. R 0 -R 7 register: These present in internal RAM of microcontroller. 3. B Register: The B register is an 8 -bit register. The B register is used only by two 8051 instructions: MUL AB and DIV AB. i. e. for multiply or divide operations. 4. The program counter, is also called as instruction pointer. This is a register which stores address of the instruction to be executed next. The Program Counter (PC) holds the address which tells the 8051 microcontroller where the next instruction to execute can be found in the memory. or A program counter is a register that contains the address (location) of the instruction being executed at the current time. As each instruction gets fetched, the program counter contents gets incremented by 1. i. e. because of program counter automatic execution of program happens. Atul M Kulkarni, Dr. Babasaheb Ambedkar Technological University, Lonere

8 Registers in 8051 contin. . 5. Stack is a temporary area present in RAM, which is used to store temporary data. The Stack pointer is a register that holds the address of stack area. 6. The Data Pointer: The Data Pointer (DPTR) is the 8051’s only user-accessible 16 -bit (2 -byte) register. DPTR is used for pointing to data. It is used by the 8051 to access external memory using the address indicated by DPTR is the only 16 -bit register available and is often used to store 2 -byte values. Atul M Kulkarni, Dr. Babasaheb Ambedkar Technological University, Lonere

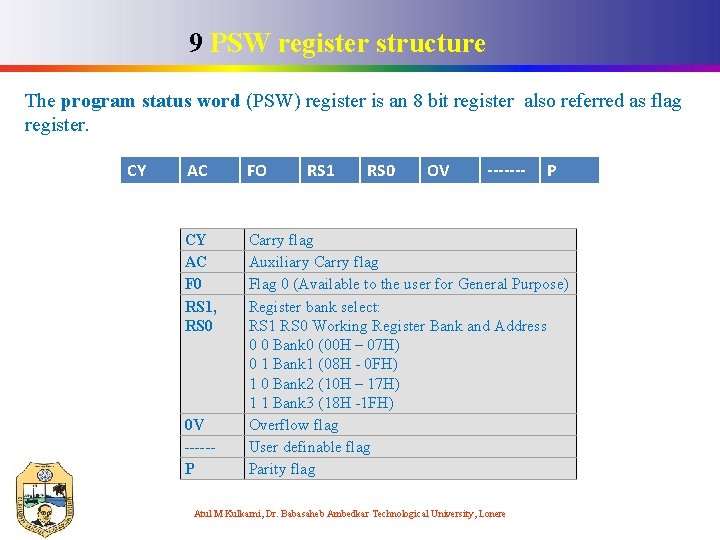

9 PSW register structure The program status word (PSW) register is an 8 bit register also referred as flag register. CY AC FO CY AC F 0 RS 1, RS 0 Carry flag Auxiliary Carry flag Flag 0 (Available to the user for General Purpose) Register bank select: RS 1 RS 0 Working Register Bank and Address 0 0 Bank 0 (00 H – 07 H) 0 1 Bank 1 (08 H - 0 FH) 1 0 Bank 2 (10 H – 17 H) 1 1 Bank 3 (18 H -1 FH) Overflow flag User definable flag Parity flag 0 V -----P RS 1 RS 0 OV ------- Atul M Kulkarni, Dr. Babasaheb Ambedkar Technological University, Lonere P

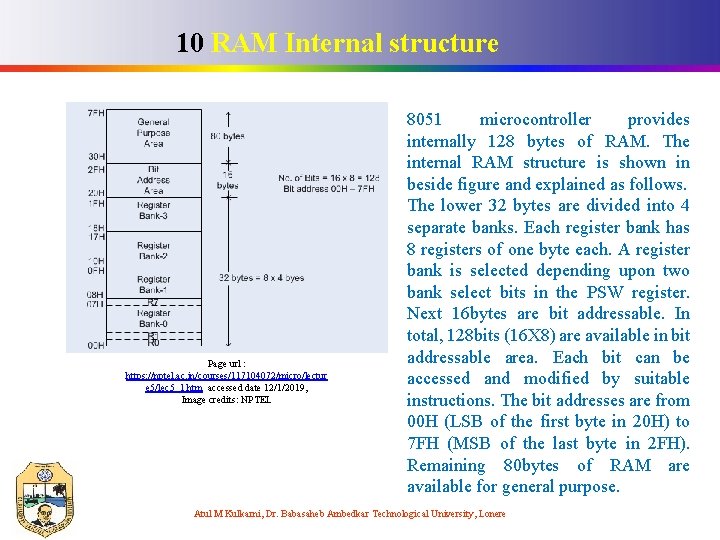

10 RAM Internal structure Page url : https: //nptel. ac. in/courses/117104072/micro/lectur e 5/lec 5_1. htm accessed date 12/1/2019, Image credits: NPTEL 8051 microcontroller provides internally 128 bytes of RAM. The internal RAM structure is shown in beside figure and explained as follows. The lower 32 bytes are divided into 4 separate banks. Each register bank has 8 registers of one byte each. A register bank is selected depending upon two bank select bits in the PSW register. Next 16 bytes are bit addressable. In total, 128 bits (16 X 8) are available in bit addressable area. Each bit can be accessed and modified by suitable instructions. The bit addresses are from 00 H (LSB of the first byte in 20 H) to 7 FH (MSB of the last byte in 2 FH). Remaining 80 bytes of RAM are available for general purpose. Atul M Kulkarni, Dr. Babasaheb Ambedkar Technological University, Lonere

- Slides: 10