1 2 3 4 ATM Asynchronous Transfer Mode

- Slides: 51

1. 2. 3. 4. ATM( Asynchronous Transfer Mode) SWITCHING CHEN SHAN Group WAN 1 WET 020022 GRACE CHANG POOI KUAN WET 020042 LIM SEOW FONG WET 020072 NG SIAO SHAN WET 020104

Content of Presentation n n Introduction To ATM Switching And Functions of ATM Switching Grace Chang Pooi Kuan WET 020042 ATM Switching Architecture Tan Phaik See WET 020174 ATM Switching Techniques Chen Shan WET 020022 Switching Element Requirements Ng Siao Shan WET 020104 Queuing Methods Lim Seow Fong WET 020072

Introduction To ATM Switching And Functions of ATM Switching Grace Chang Pooi Kuan WET 020042

Introduction to ATM switching n What is Asynchronous Transfer Mode (ATM) switching ?

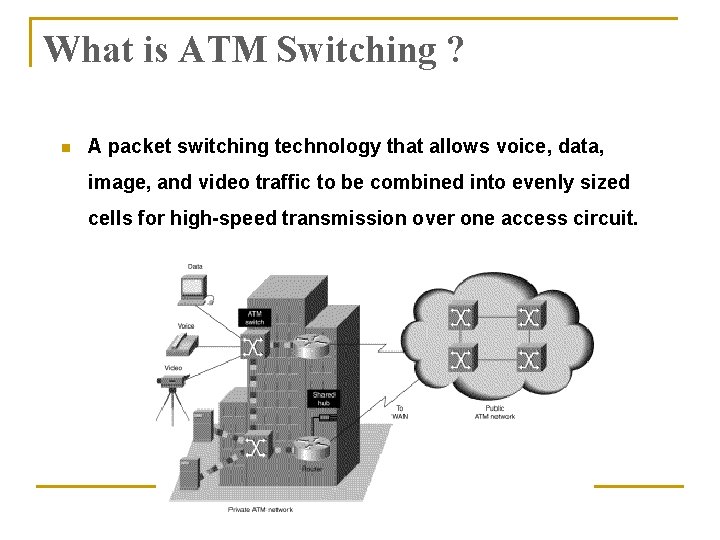

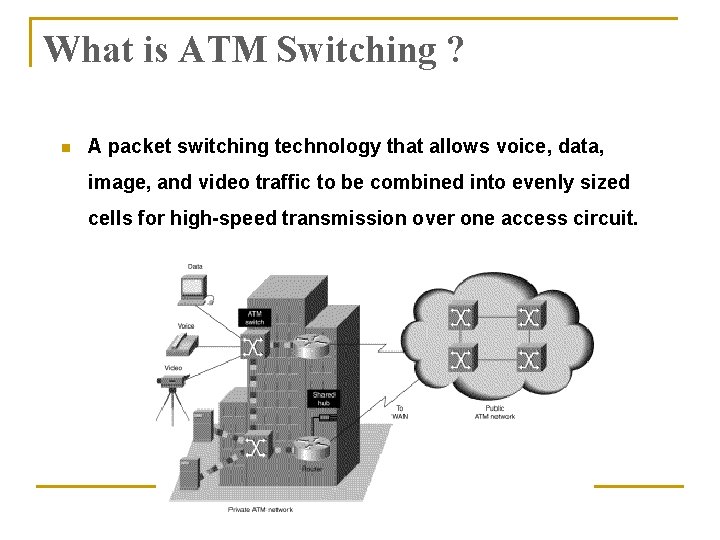

What is ATM Switching ? n A packet switching technology that allows voice, data, image, and video traffic to be combined into evenly sized cells for high-speed transmission over one access circuit.

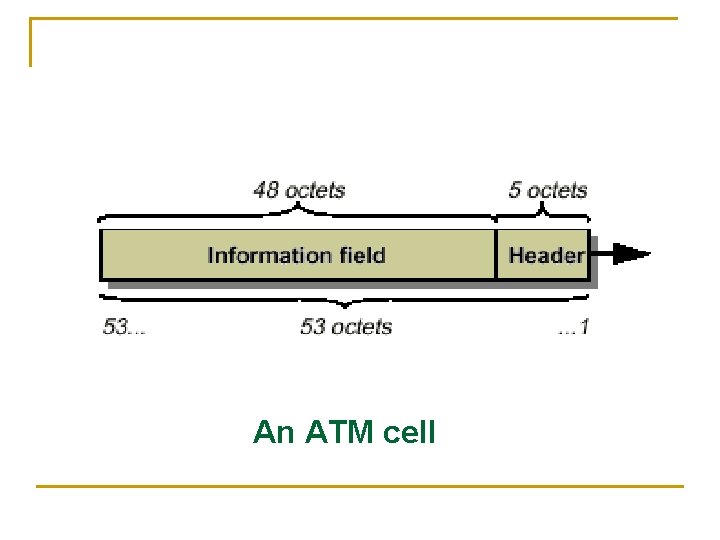

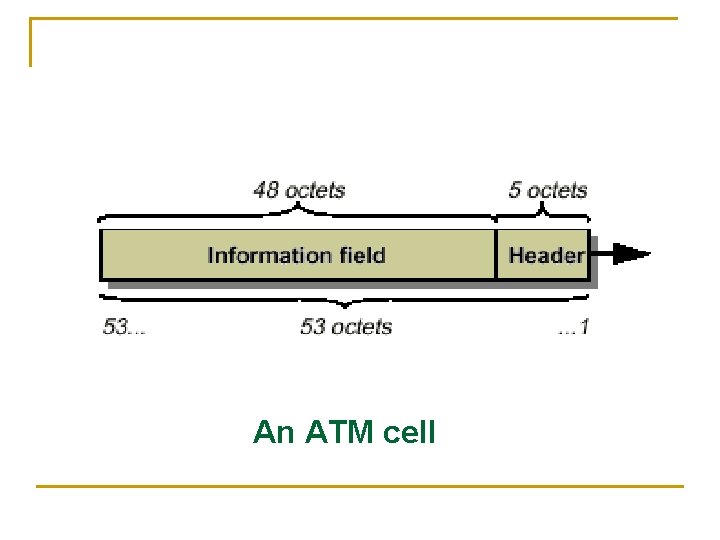

n This means that all the information sent over an ATM network is broken down into discrete packets. n Each 53 byte cell contains 48 bytes of payload and 5 bytes of control information. n Because the cells are all the same size, cell delay at ATM switches is more predictable and manageable.

An ATM cell

n The aim of ATM switch design is to increase speed, capacity and overall performance. n ATM switching differs from conventional switching because of the high-speed interfaces (50 Mbps to 2. 4 Gbps) to the switch, with switching rates up to 80 Gbps in the backplane. n ATM was designed specifically to handle broadband applications efficiently and at the same time let users give certain types of traffic priority treatment on the network.

n For example, voice traffic, which cannot tolerate much delay, can be marked "high priority" with a guaranteed bandwidth and minimal delay. Less sensitive traffic, such as electronic mail, can be marked for lower priority. n ATM networks are linked together by a series of ATM switches that take in cells from various sources and switch them out again.

ATM Switch Functions n ATM switch functions : ü User Plane ü Control Plane ü Management Plane

ATM Switch Functions n An ATM switch contains a set of input ports and output ports, through which it is interconnected to users, other switches, and other network elements.

n There are 3 planes of the switching functions in the context of the Broadband Integrated Services Digital Network (B-ISDN) model : ü User Plane ü Control Plane ü Management Plane

User Plane n The main function of an ATM switch is to relay user data cells from input ports to the appropriate output ports. n The switch processes only the cell headers and the payload is carried transparently. n As soon as the cell comes in through the input port, the Virtual Path Identifier/Virtual Channel Identifier (VPI/VCI) information is derived and used to route the cells to the appropriate output ports.

Control Plane n This plane represents functions related to the establishment and control of the Virtual Path/Virtual Channel (VP/VC) connections. n Unlike the user data cells, information in the control cells payload is not transparent to the network. The switch identifies signaling cells, and even generates some itself.

Management Plane n The management plane is concerned with monitoring the controlling the network to ensure its correct and efficient operation. n These operations can be subdivided as ü fault management functions, ü performance management functions, ü configuration management functions, ü security management functions, ü accounting management ü traffic management.

ATM Switching Architecture Tan Phaik See WET 020174

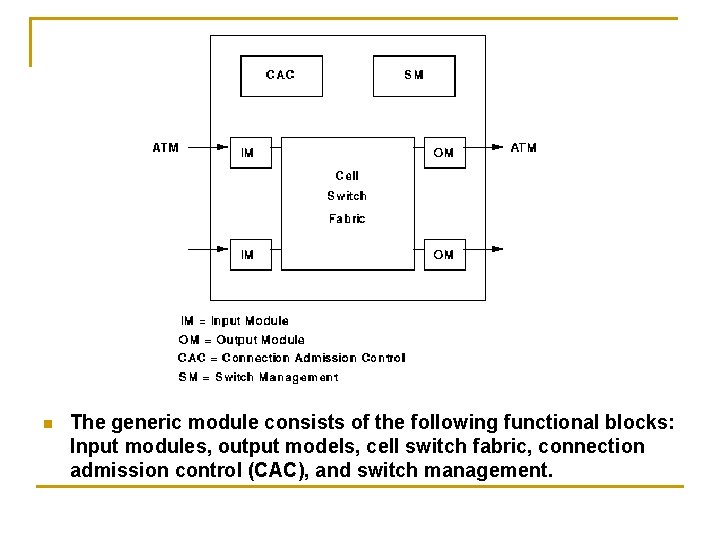

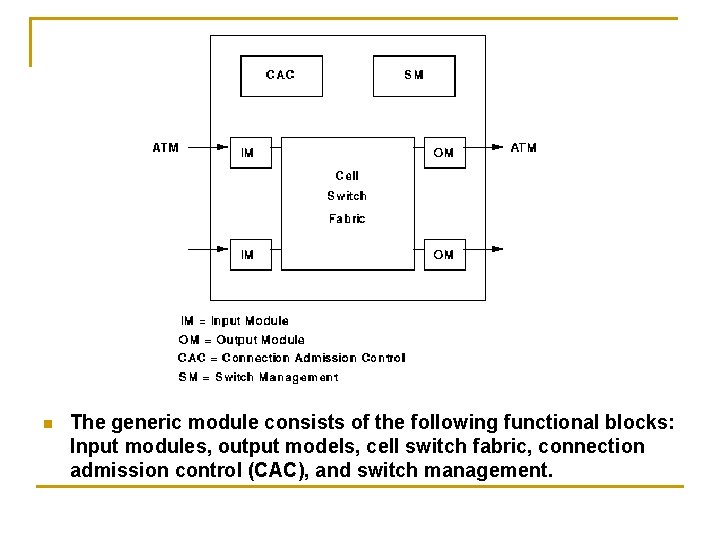

ATM n The generic module consists of the following functional blocks: Input modules, output models, cell switch fabric, connection admission control (CAC), and switch management.

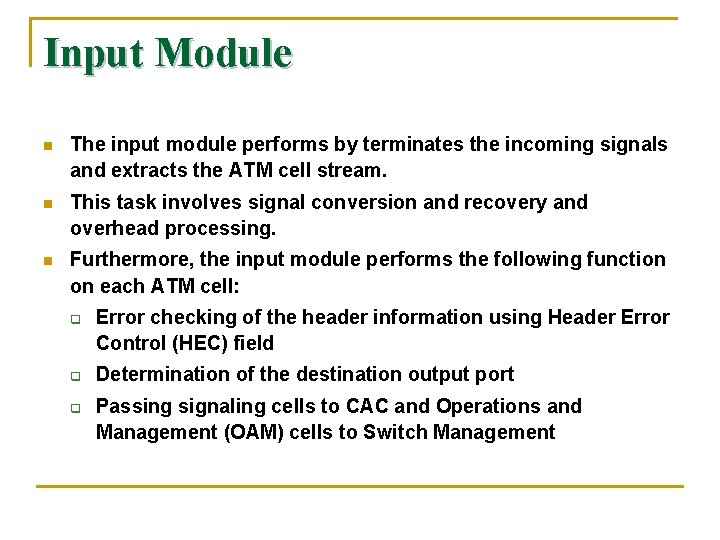

Input Module n The input module performs by terminates the incoming signals and extracts the ATM cell stream. n This task involves signal conversion and recovery and overhead processing. n Furthermore, the input module performs the following function on each ATM cell: q q q Error checking of the header information using Header Error Control (HEC) field Determination of the destination output port Passing signaling cells to CAC and Operations and Management (OAM) cells to Switch Management

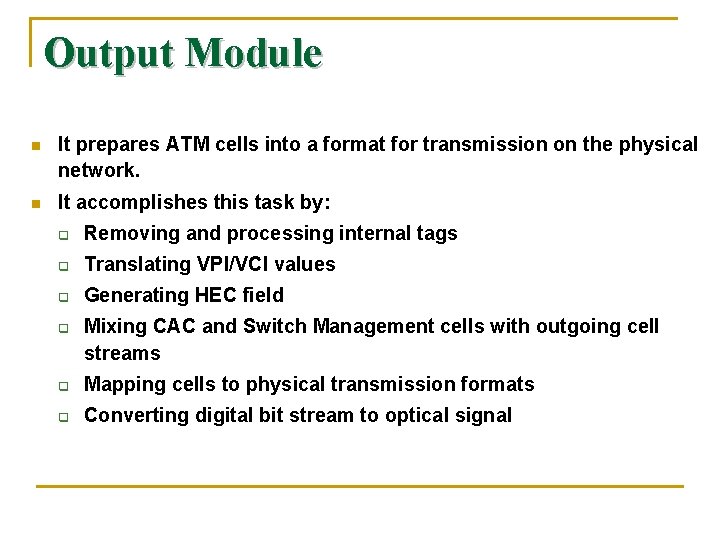

Output Module n It prepares ATM cells into a format for transmission on the physical network. n It accomplishes this task by: q Removing and processing internal tags q Translating VPI/VCI values q Generating HEC field q Mixing CAC and Switch Management cells with outgoing cell streams q Mapping cells to physical transmission formats q Converting digital bit stream to optical signal

Cell Switch Fabric n The main task is to perform the routing of data cells, signaling and management cell. n It receives cells on an incoming port, reads the VPI/VCI value, and identifies an appropriate outgoing port for the next node that is to receive the traffic.

Connection Admission Control (CAC) n A set of procedures that include actions taken by the network to grant or deny a virtual connection. n It establishes, modifies, and terminates virtual path/virtual channel connections. n It is responsible for: q high-layer signaling protocols q interface with a signaling network

Switch Management n It has the overall responsibility of providing key information for managing the switch and the network. n It performs tasks that include the following: q Traffic management q Network Management q Security control for switch database q Customer-network management

ATM Switching Techniques Chen Shan WET 020022

ATM Switching Techniques Cell Switch Fabric - to relay ATM cells as quickly as n possible and accomplishes this by performing 2 major functions: v Concentration, expansion, multiplexing/demultiplexing of traffic v Routing and buffering of traffic

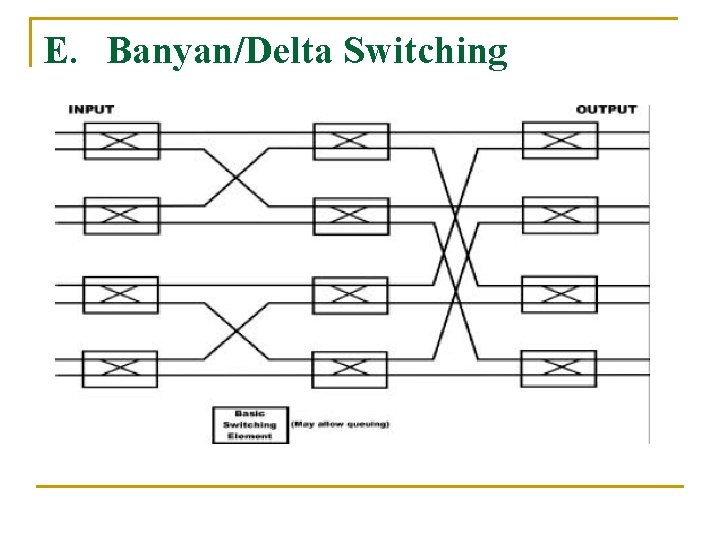

Five ATM Switching Alternatives : A. Shared Memory Switch B. Shared Bus Switch C. Crossbar Switch D. Multistage Switching E. Banyan/Delta Switching

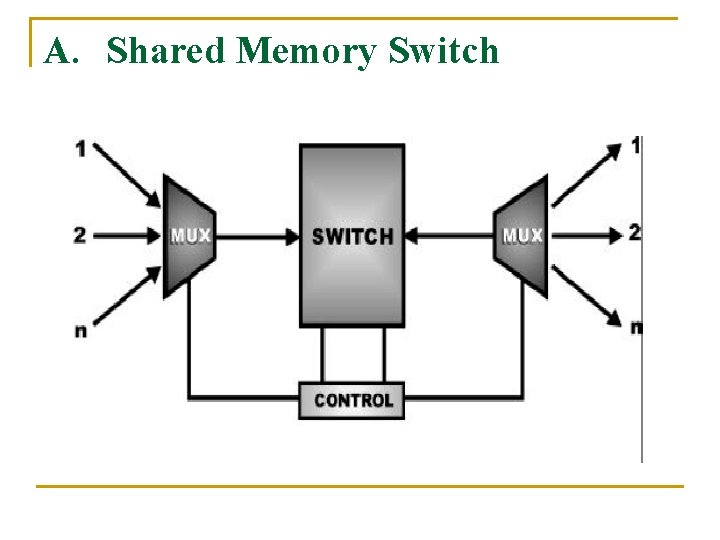

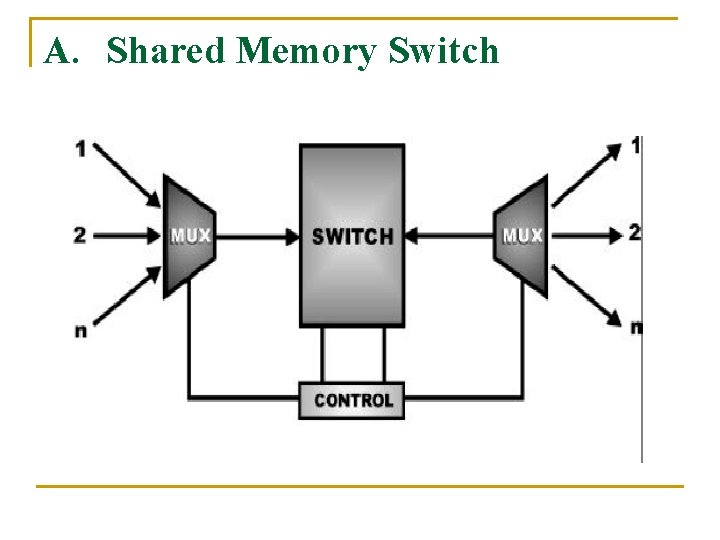

A. Shared Memory Switch

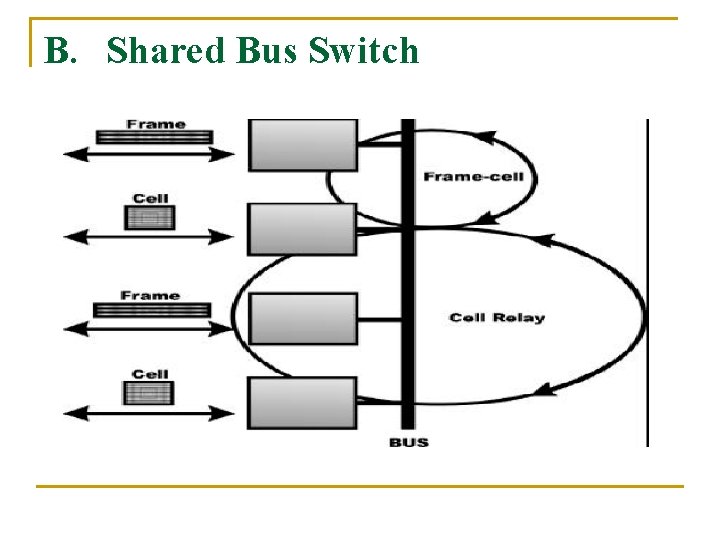

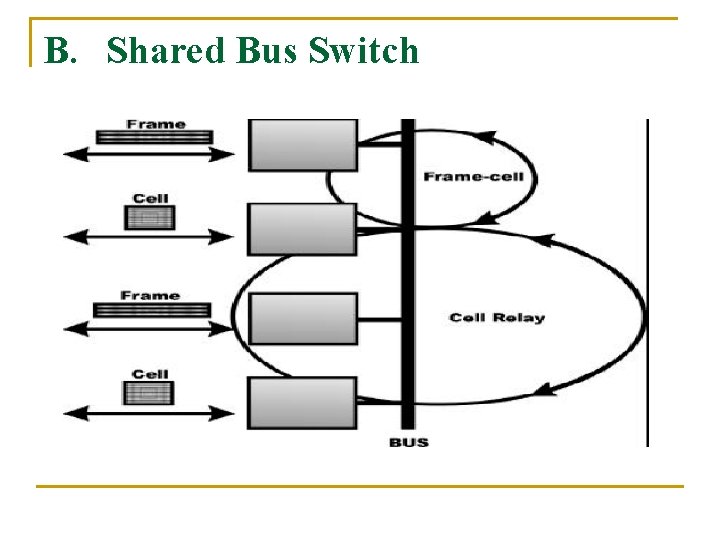

B. Shared Bus Switch

C. Crossbar Switch

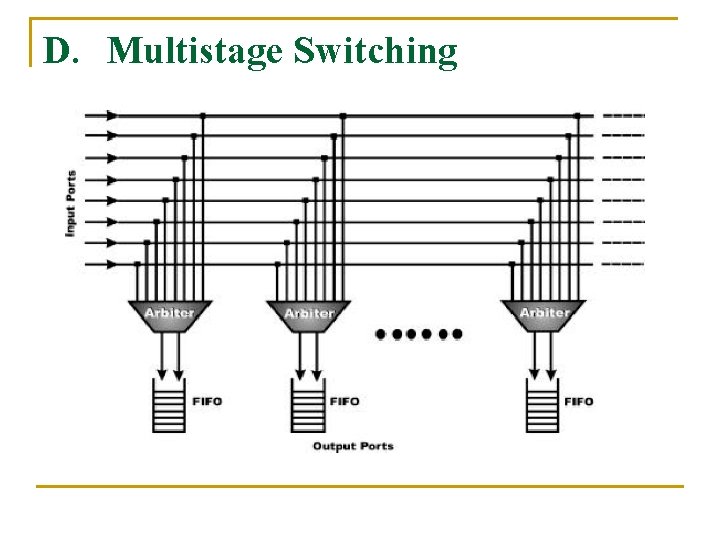

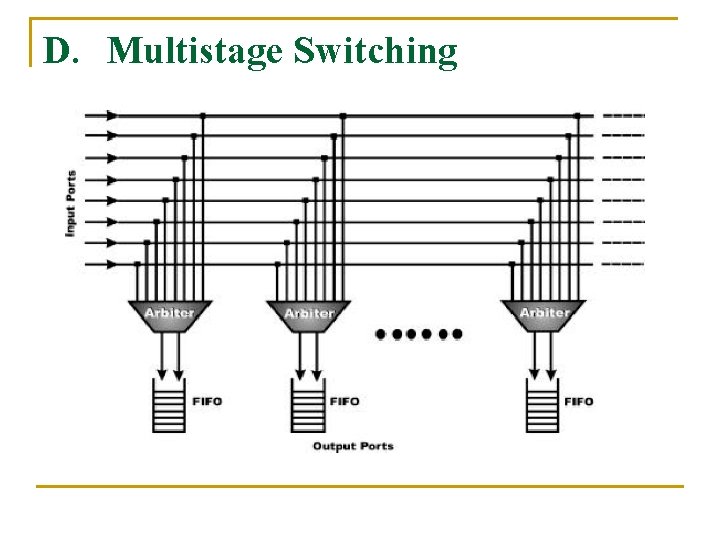

D. Multistage Switching

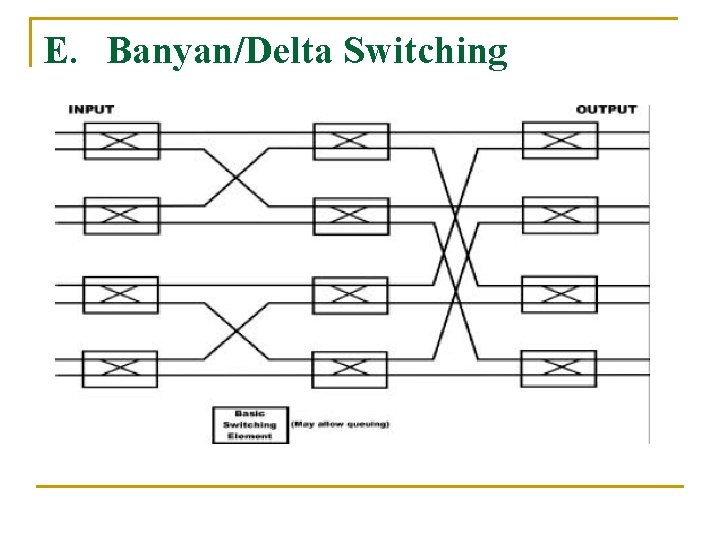

E. Banyan/Delta Switching

Switching Element Requirements Ng Siao Shan WET 020104

Switching Element Requirements n The ATM switch architectures have to consider above these requirements. 1. Performance 2. Information Rates 3. Broadcast

Performance a) b) c) Connection Blocking Cell Loss, Cell Insertion Switching Delay

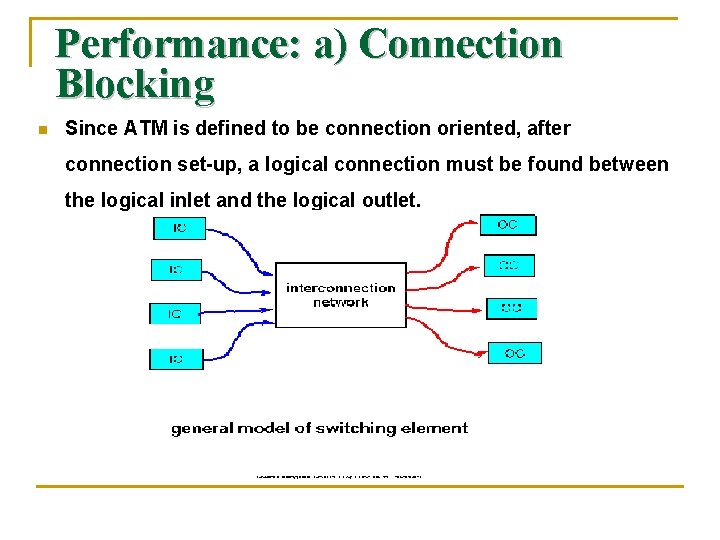

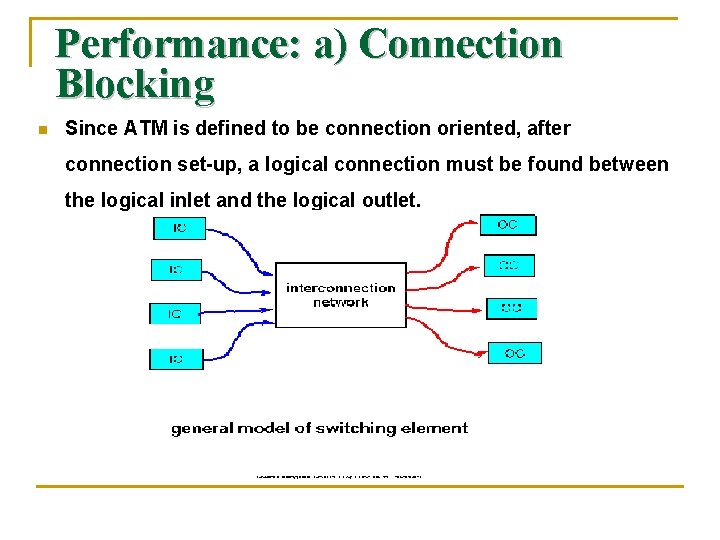

Performance: a) Connection Blocking n Since ATM is defined to be connection oriented, after connection set-up, a logical connection must be found between the logical inlet and the logical outlet.

Cont n Connection blocking is defined as the probability that not enough resources can be found to allow all the required physical connections between inlets and outlets at any time.

Performance: b) Cell Loss, Cell Insertion n In an ATM switch it is possible that temporarily too many cells in the switch have to be transmitted through the same link (switch internal or external link). n In optimal operational conditions there is an available entry in a queue to hold all the cells. n But if the queue is currently full, another cell that will require the same queue will be lost. n The probability of a cell lost must be kept in a specified limits to assure high semantic transparency. n Some switching architectures are designed such that they will not suffer from cells competing for the same resources internally, but only at their inlets and/or outlets.

Cont n n n It is also possible that from some internal routing error a cell will be sent to the wrong logical connection. If such an error occurs, error impact is doubled by the fact that one destination will miss a cell and that a second destination will accept an additional cell. The switch element has to be designed so that cell insertion error probability will be about 1000 times better than a cell loss.

Performance: c) Switching Delay n To allow support of different real time services in an ATM network, a maximal delay has to be guaranteed and a low values of jitter. n Typical delay values are between 10 and 1000 usec, with jitter of 100 nsec or less. n The delay and the jitter in the cell are strongly related to the queueing in the switching element. A small queue will assure better delays but will increase the cell loss probability.

Information Rates n A large number of information rates have to be switched in the same ATM switch. n The maximal bit rate which a future ATM switch has to be able to switch lies around 150 Mbit/sec. n For such fast services, the switching element can be implemented as several switching elements in parallel. n Or, several 150 Mbit/sec switching elements can be multiplexed on a single link. n That will require a switching rate in the order of Gbit/sec.

Broadcast n In classical connection oriented packet switching services, only point to point connections are available, because the information (cell) can be switched from one logical inlet to one logical outlet only. n In future broadband networks broadcast and multicast services are required for different applications from electronic-mail to network TV services.

Queuing Methods Lim Seow Fong WET 020072

Queuing Methods: Problems n Many queuing problems in an ATM switch because: q q q n The pre-assigned time slot concept disappears in ATM switching systems ATM switch performs statistical multiplexing in the switch inputs de-multiplexing in the switch outputs For example: q Two ATM cells arrived at two inlets at the same time and are aiming for the same outlet

Queuing Methods: Approaches n Queue of waiting cells has to be implemented in the switch: q Input Buffers q Output Buffers q Central Queuing

Queuing Methods: a) Input Buffers n Add a queue at the switch element inputs n The buffers are located at the input controller (IC) n The switch interconnection network will transfer the cell from the input buffer to the output buffer without internal conditions n Arbitration logic is needed to determine which of the cells held in different inlet buffers destined to the same output will be transferred in the interconnection network

Queuing Methods: a) Input Buffers (cont’) n Solution: q The FIFO buffer can be replaced by a random access memory (RAM) q If the first cell in the queue is blocked, the next cell which is destined for an idle output (or internal switch interconnection network link) will be selected for transmission

Queuing Methods: a) Input Buffers (cont’) n The disadvantage of this solution: q A complex buffering control is required to find a cell destined to an idle connection to guarantee a correct cell sequence of cells destined for the same output. q The input buffer approach achieves the worst performance in the sense of the queue length required to achieve a given cell-loss rate in various switch loads in comparison to the other two queuing methods.

Queuing Methods: b) Output Buffers n Add a queue at the switch output n The buffers are located at the output controller (OC) of the switch element n The assumption is that many cells from the IC can cross the internal interconnection network and arrive to the outlets n This solution requires use of a very fast internal pass

Queuing Methods: b) Output Buffers (cont’) n In order to allow a non-blocking switch, the interconnection network and the output buffer have to be capable of handling N cells at one cell time (when N in the number of ICs) n When output buffers are in use, no arbitration has to be used. The control of the output is based on a simple FIFO logic

Queuing Methods: c) Central Queuing n Add a queue between the inputs on the outputs of the switch n The queuing buffers are not dedicated to a single inlet or to a single outlet, but shared between all inlets and outlets n Each coming cell will be directly stored in the central storing element n Every outlet will identify the cells destined to it in a FIFO discipline

Queuing Methods: c) Central Queuing (cont’) n Advantage: q Most efficient and required the smallest total storage to allow minimal cell loss in heavy load conditions q Since the available memory on an integrated circuit switching element is limited, it is possible to achieve low cell -loss probabilities when using the central queuing approach

Queuing Methods: c) Central Queuing (cont’) n Disadvantage: q Very fast memory elements are required to allow all the coming cells and outgoing cells access to the memory ports at the same time q Big complexity in the queue management