1 1 a Evolution of Intels Microprocessors Product

- Slides: 41

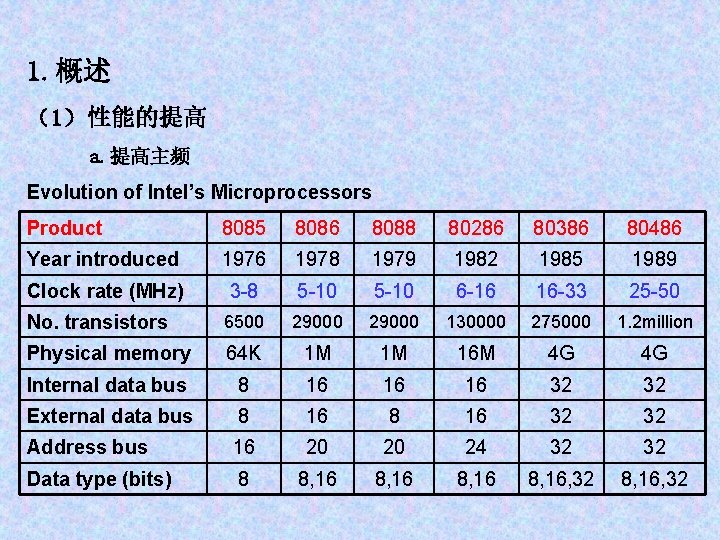

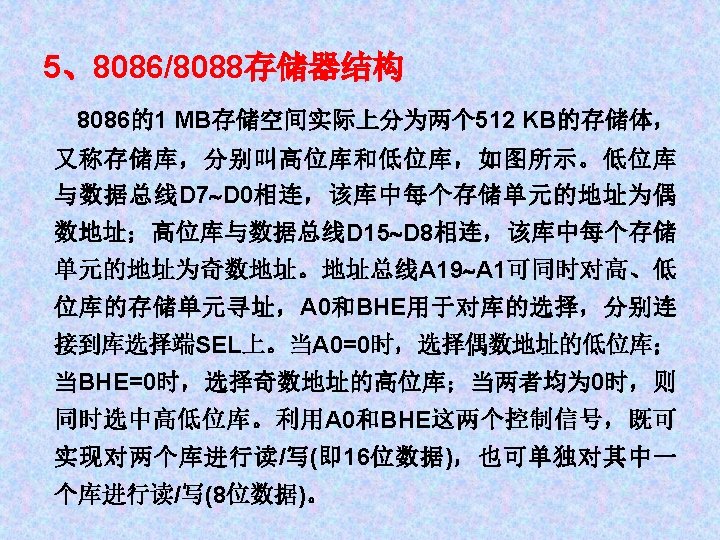

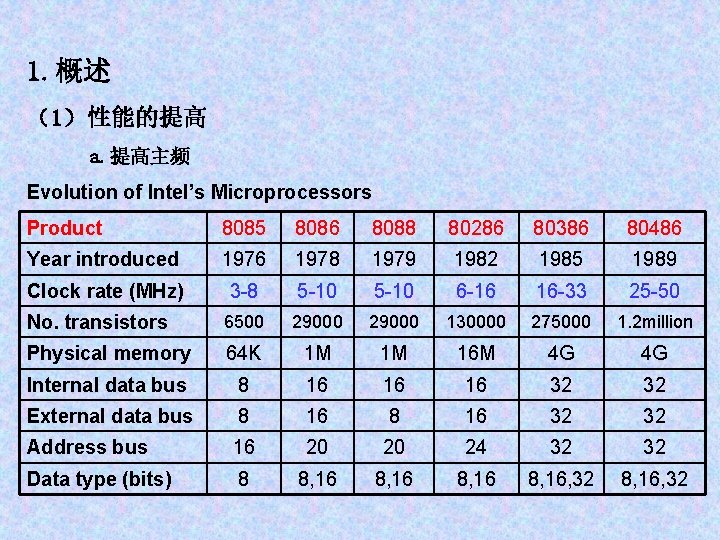

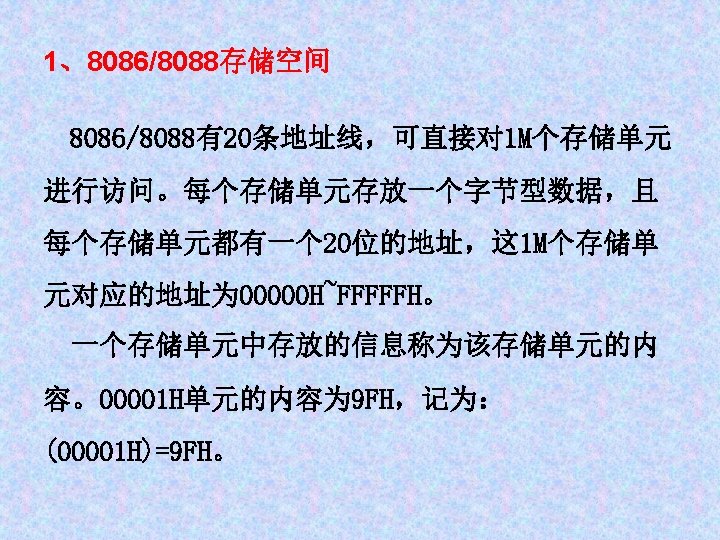

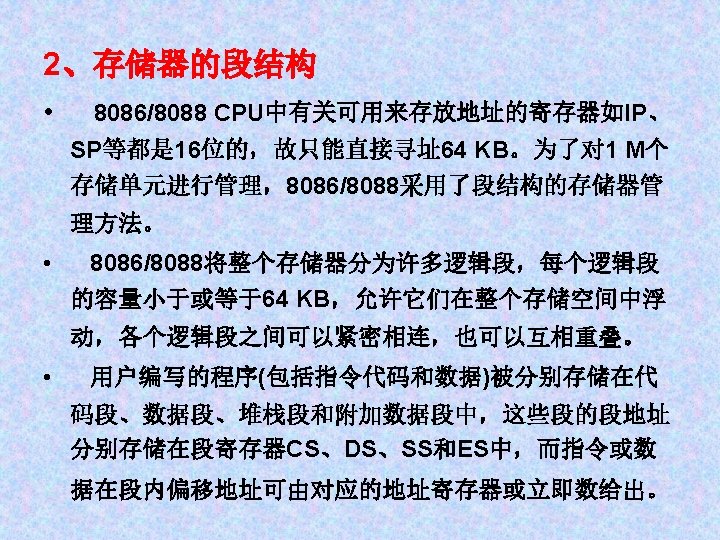

1. 概述 (1)性能的提高 a. 提高主频 Evolution of Intel’s Microprocessors Product 8085 8086 8088 80286 80386 80486 Year introduced 1976 1978 1979 1982 1985 1989 Clock rate (MHz) 3 -8 5 -10 6 -16 16 -33 25 -50 No. transistors 6500 29000 130000 275000 1. 2 million Physical memory 64 K 1 M 1 M 16 M 4 G 4 G Internal data bus 8 16 16 16 32 32 External data bus 8 16 32 32 Address bus 16 20 20 24 32 32 Data type (bits) 8 8, 16, 32 8, 16, 32

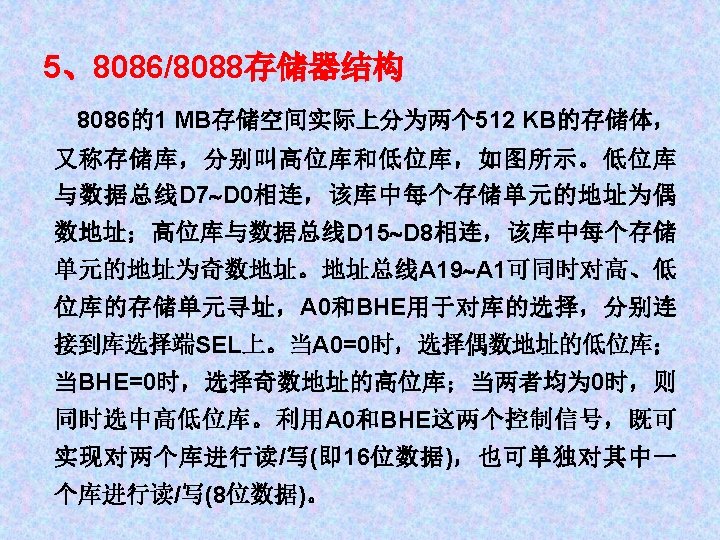

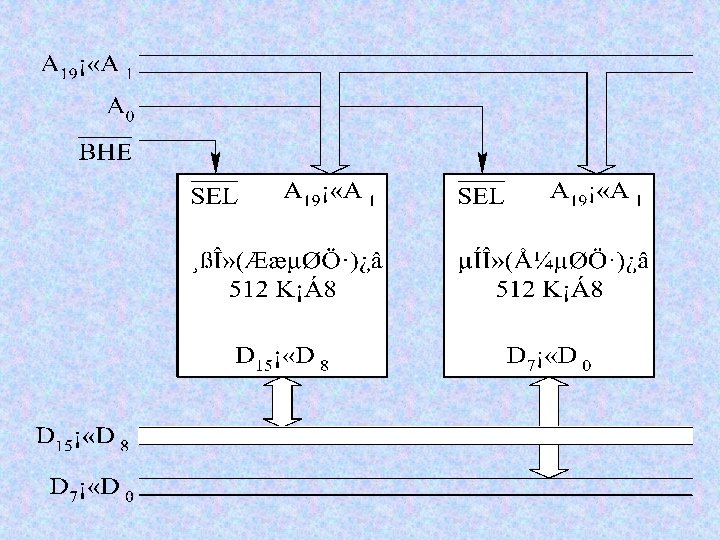

(2)采用的方法 将8086/8088微处理器分为两部分 l 执行单元(EU—Execution Unit) l 总线接口单元(BIU—Bus Interface Unit) 2. 8086/8088内部结构 执行单元(Execution Unit) 总线接口单元(Bus Interface Unit)

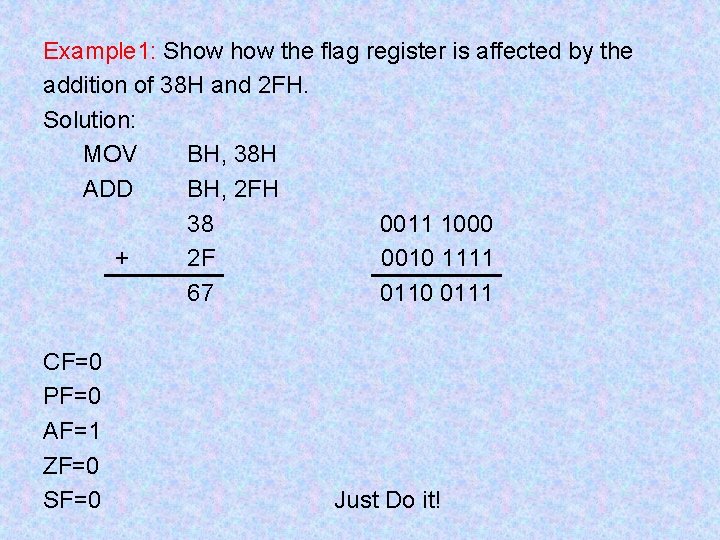

Example 1: Show the flag register is affected by the addition of 38 H and 2 FH. Solution: MOV BH, 38 H ADD BH, 2 FH 38 0011 1000 + 2 F 0010 1111 67 0110 0111 CF=0 PF=0 AF=1 ZF=0 SF=0 Just Do it!

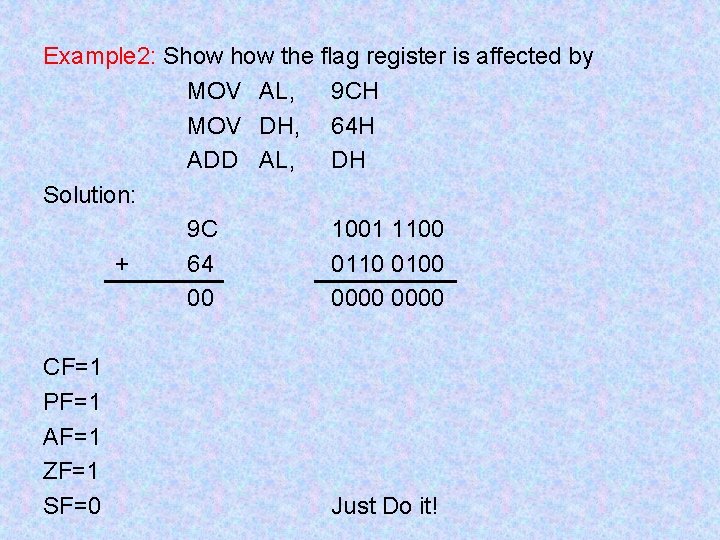

Example 2: Show the flag register is affected by MOV AL, 9 CH MOV DH, 64 H ADD AL, DH Solution: 9 C 1001 1100 + 64 0110 0100 00 0000 CF=1 PF=1 AF=1 ZF=1 SF=0 Just Do it!

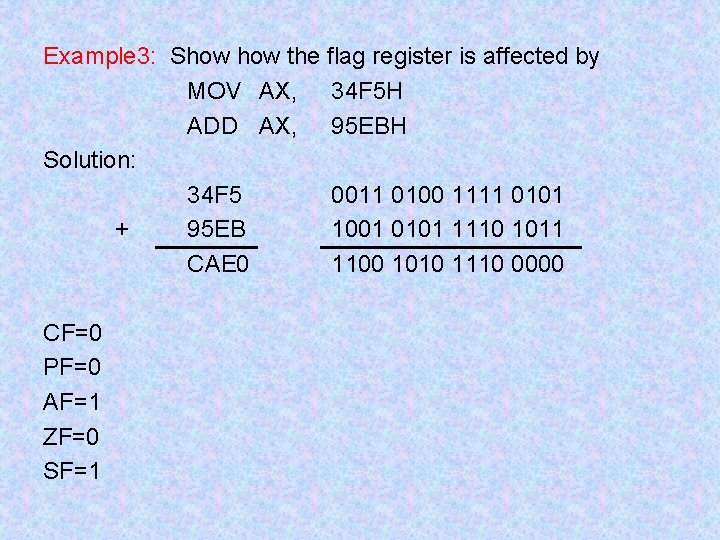

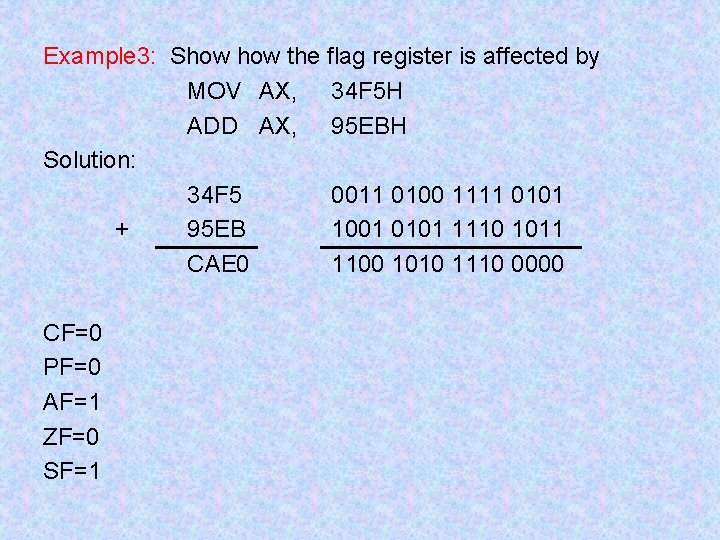

Example 3: Show the flag register is affected by MOV AX, 34 F 5 H ADD AX, 95 EBH Solution: 34 F 5 0011 0100 1111 0101 + 95 EB 1001 0101 1110 1011 CAE 0 1100 1010 1110 0000 CF=0 PF=0 AF=1 ZF=0 SF=1

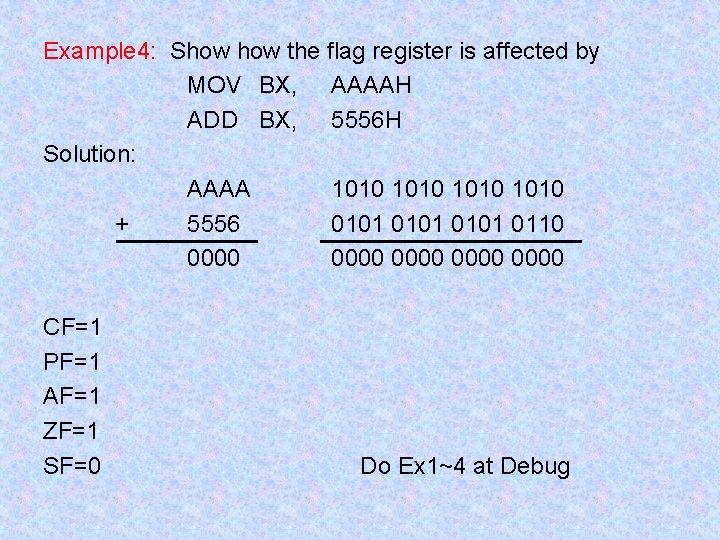

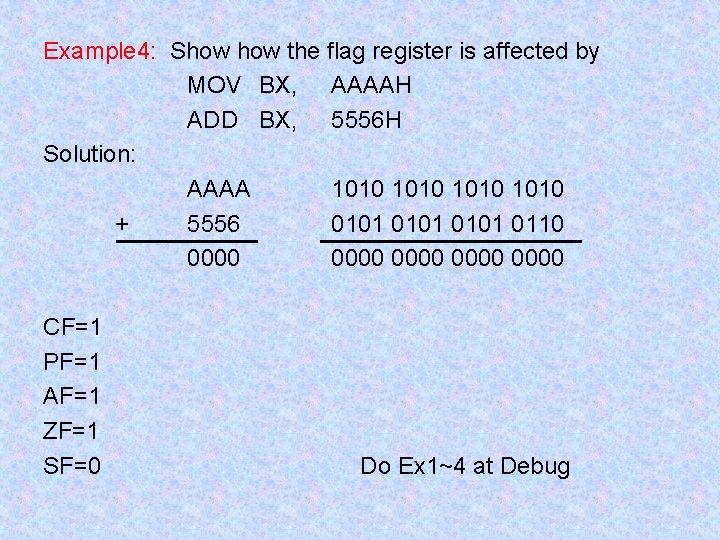

Example 4: Show the flag register is affected by MOV BX, AAAAH ADD BX, 5556 H Solution: AAAA 1010 + 5556 0101 0110 0000 0000 CF=1 PF=1 AF=1 ZF=1 SF=0 Do Ex 1~4 at Debug

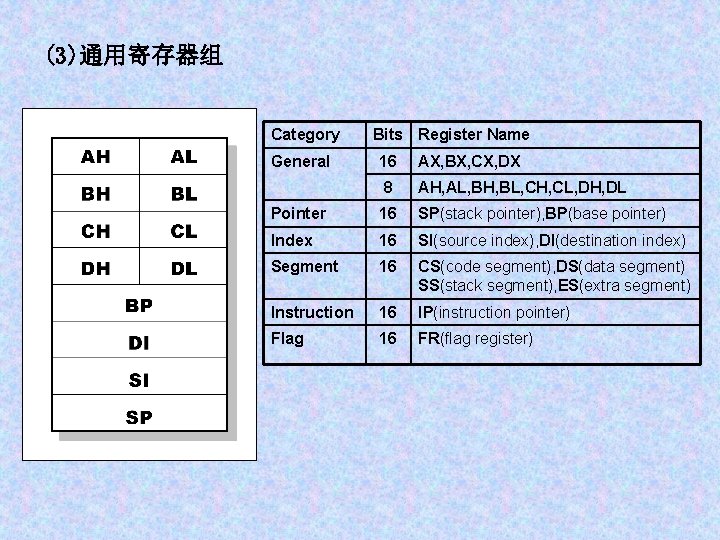

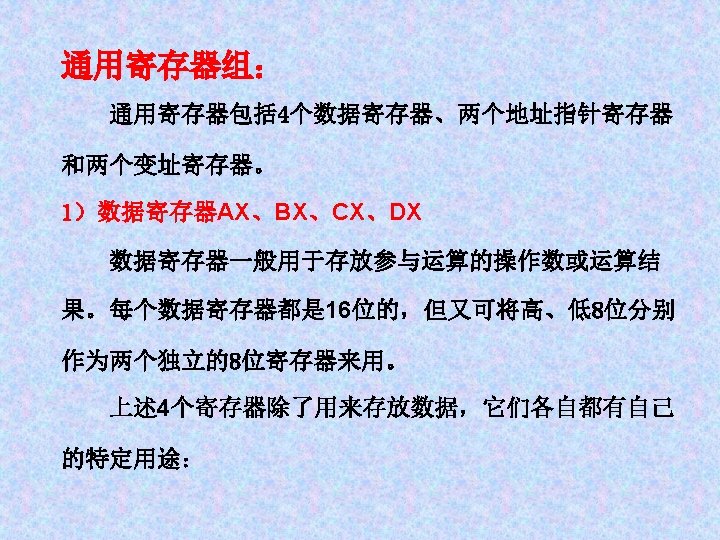

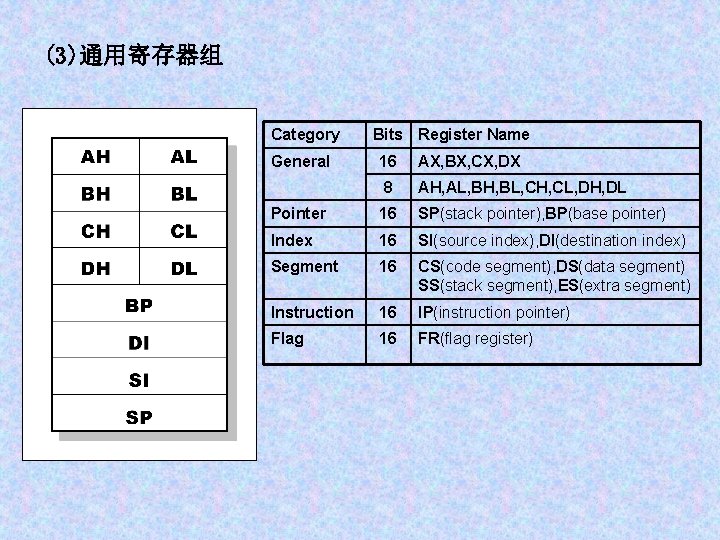

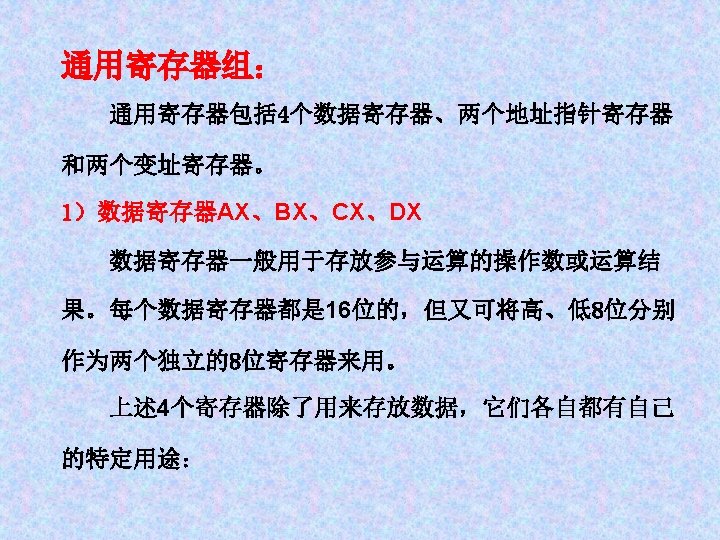

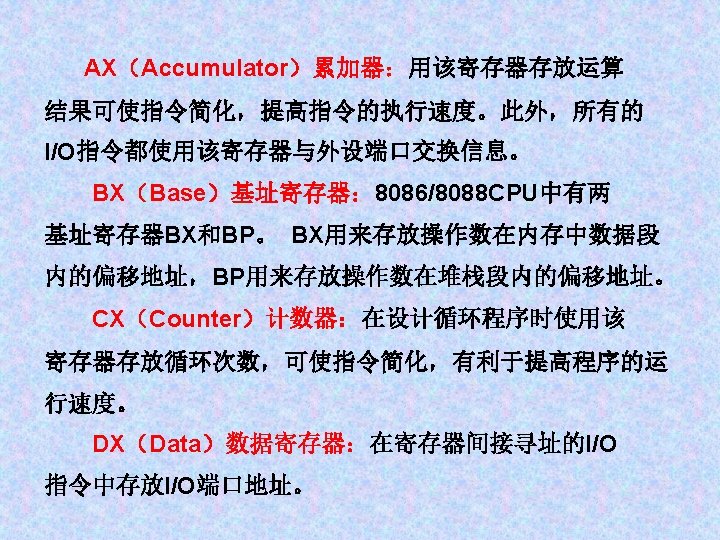

(3)通用寄存器组 Category General Bits Register Name 16 AX, BX, CX, DX 8 AH, AL, BH, BL, CH, CL, DH, DL Pointer 16 SP(stack pointer), BP(base pointer) Index 16 SI(source index), DI(destination index) Segment 16 CS(code segment), DS(data segment) SS(stack segment), ES(extra segment) Instruction 16 IP(instruction pointer) Flag 16 FR(flag register)

; FULL SEGMENT DEFINITION 握) STACK DATA CODE start: CODE 完整程序框架(熟练掌 ; -----stack segment-------SEGMENT DB 64 DUP(? ) ENDS ; -----data segment-------SEGMENT ; data definitions are placed here ENDS ; -----code segment-------SEGMENT ASSUME CS: CODE, DS: DATA, SS: STACK MOV AX, DATA MOV DS, AX - ----MOV AH, 4 CH INT 21 H ENDS END start

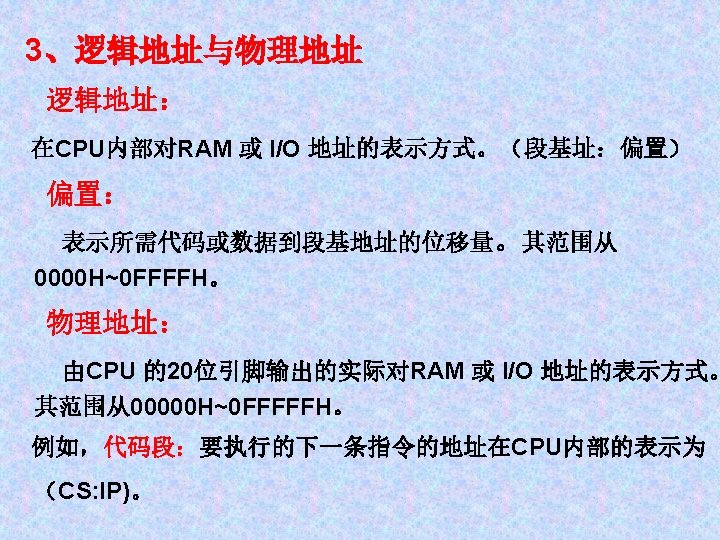

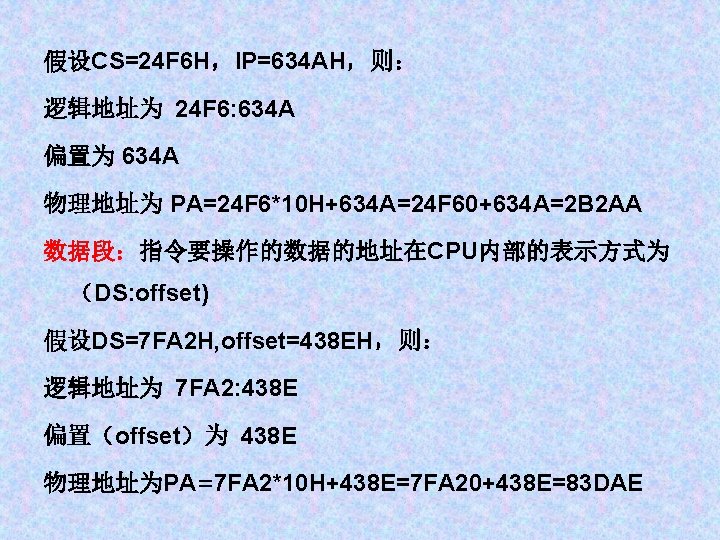

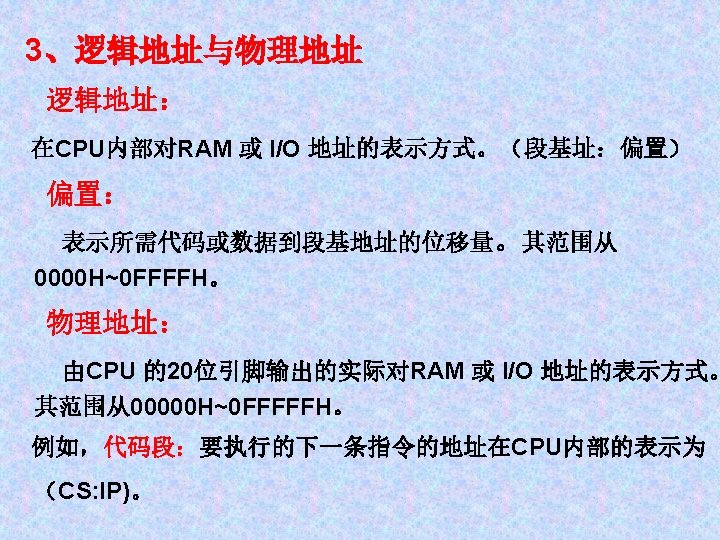

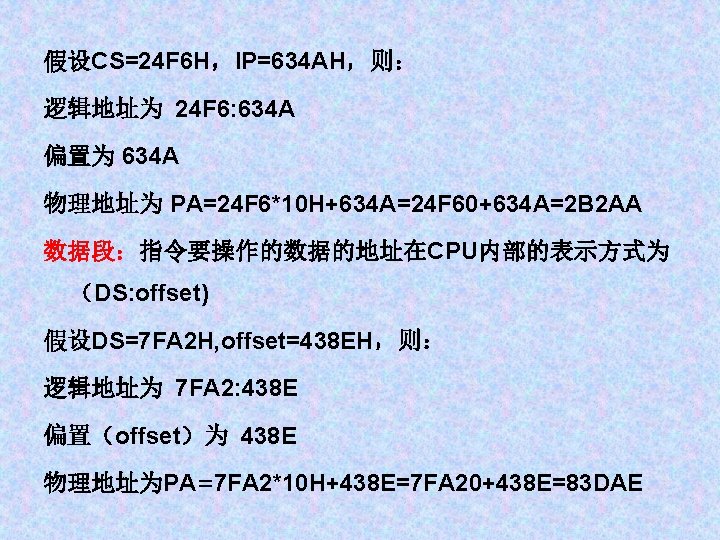

假设CS=24 F 6 H,IP=634 AH,则: 逻辑地址为 24 F 6: 634 A 偏置为 634 A 物理地址为 PA=24 F 6*10 H+634 A=24 F 60+634 A=2 B 2 AA 数据段:指令要操作的数据的地址在CPU内部的表示方式为 (DS: offset) 假设DS=7 FA 2 H, offset=438 EH,则: 逻辑地址为 7 FA 2: 438 E 偏置(offset)为 438 E 物理地址为PA=7 FA 2*10 H+438 E=7 FA 20+438 E=83 DAE

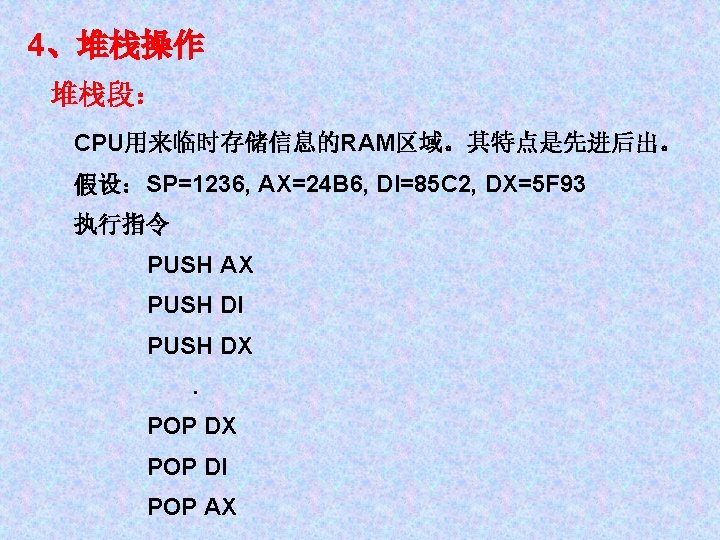

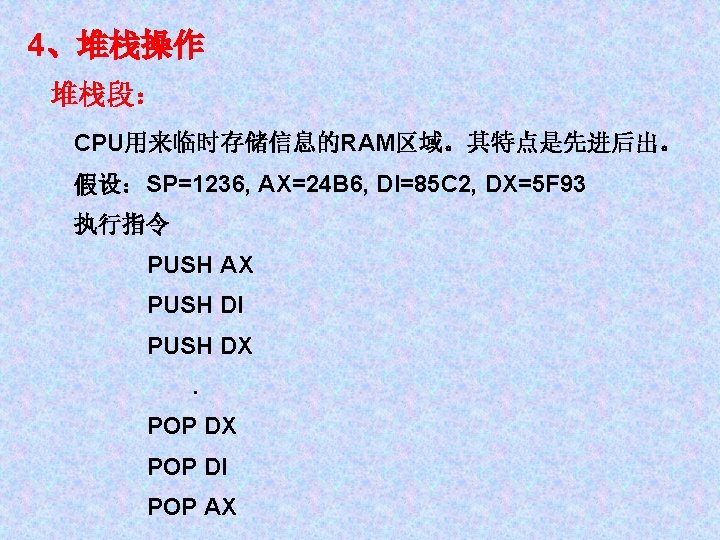

堆栈段: 假设SS=3500 H,SP=0 FFFEH,则: 逻辑地址为 SS: SP 即 3500: 0 FFFE 偏置为 0 FFFEH 物理地址为 SS*10 H+SP 即 PA=3500 H*10 H+0 FFFEH=35000 H+0 FFFEH=44 FFEH 缺省段和偏置:

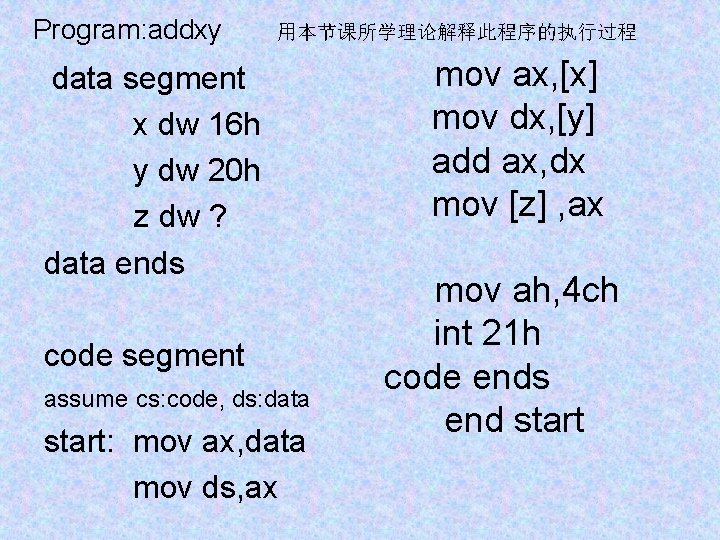

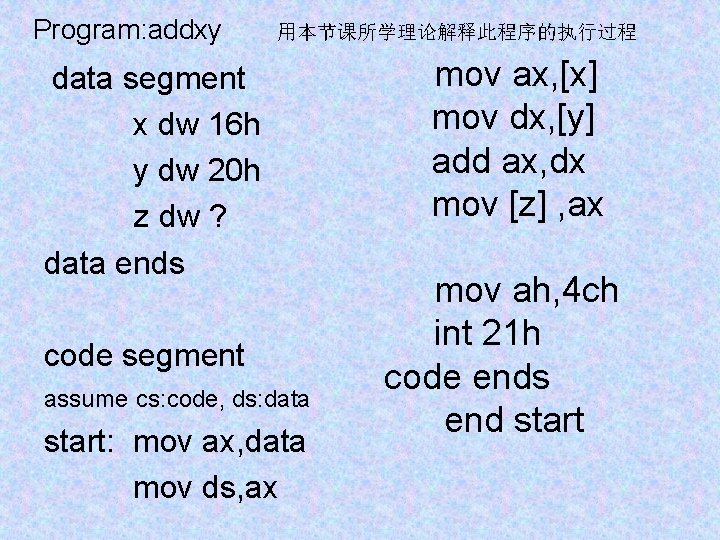

Program: addxy 用本节课所学理论解释此程序的执行过程 data segment x dw 16 h y dw 20 h z dw ? data ends code segment assume cs: code, ds: data start: mov ax, data mov ds, ax mov ax, [x] mov dx, [y] add ax, dx mov [z] , ax mov ah, 4 ch int 21 h code ends end start